據國外媒體援引業內人士的觀點指出,由于10納米以下芯片的生產工作需要大量資本投入,大量芯片制造商紛紛基于成本考慮選擇將業務重點繼續放在現有14/12納米工藝上,同時減緩了自己對更先進納米工藝的投資腳步。

眾所周知,10納米以下芯片制造工藝的研發成本非常高昂。許多芯片廠商也意識到了這一問題,并開始考慮如此高的研發投入是否能夠給自己帶來長遠收益。

海思(HiSilicon)集團不久前曾表示,公司將斥資3億美元研發基于7納米工藝的下一代SoC芯片產品。然而,包括高通和聯發科(MediaTek)都已經通過推出新的14/12納米芯片解決方案加強自己在中高端市場的競爭力。

消息人士指出,在目前的市場環境下,許多企業都對向7納米芯片技術轉型是否必要心存疑慮。

除了臺積電和三星之外,其他廠商暫緩跟進7納米的主要原因是市場需求尚未達到。目前7納米的良品率低、流片成本高,且現有產品足以支持主流應用,并不需要更高的性能。如果采用7納米工藝制造,芯片制造商大約需要每年1.2-1.5億套的產量才能夠盈虧平衡,彌補研發成本。目前看來,只有蘋果、三星、高通和聯發科能夠達到這樣的生產規模。

報道稱,高通和聯發科已將自己的7納米芯片解決方案推出時間從2018年推遲到了2019年,預計將同自己的智能手機5G解決方案一同推出市場。分析人士認為,在5G設備正式投入商用前,高通和聯發科繼續專注于中高端市場是一個合適的舉措,也同公司致力于滿足消費者當下實際需求的理念相一致。

目前,臺積電和三星都已經公布了自己7納米技術的演進路線圖。中國***芯片代工廠商聯電(UMC)則已經將自己的投資重點轉移到已經成熟和擁有技術優勢的產品線上,同時進一步弱化了同競爭對手有關更先進芯片技術的競爭。該公司希望,通過這一戰略轉型加強現有產品線競爭力,同時提高公司運營利潤。

需要指出的是,全球第二大晶圓代工廠芯片制造商GlobalFoundries上月宣布,公司放棄了開發下一代半導體技術的宏偉計劃,轉而將資源聚焦到現有技術上。這意味著GlobalFoundries將會裁掉5%的員工,也意味著下一代半導體領域剩下的廠家就只有蘋果的現任芯片代工商臺積電和前任代工商三星。

對此,GlobalFoundries CTO嘉里-派頓(Gary Patton)堅稱,公司做出這一決定不是因為技術問題,而是在謹慎考慮了7納米工藝的商業機會和財務問題后做出的選擇。

“現有14/12納米還有很大的改進空間,改進現有技術所需的資源比研發7納米甚至5納米工藝要少得多。而且即使到2022年,四分之三的芯片市場仍然只需要12納米工藝。”派頓當時解釋道。

-

芯片

+關注

關注

456文章

51192瀏覽量

427314 -

高通

+關注

關注

77文章

7508瀏覽量

191174 -

聯發科

+關注

關注

56文章

2692瀏覽量

255162 -

7納米工藝

+關注

關注

0文章

5瀏覽量

2866

原文標題:成本過高致大量芯片廠暫緩先進工藝轉型!

文章出處:【微信號:CSF211ic,微信公眾號:中國半導體論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

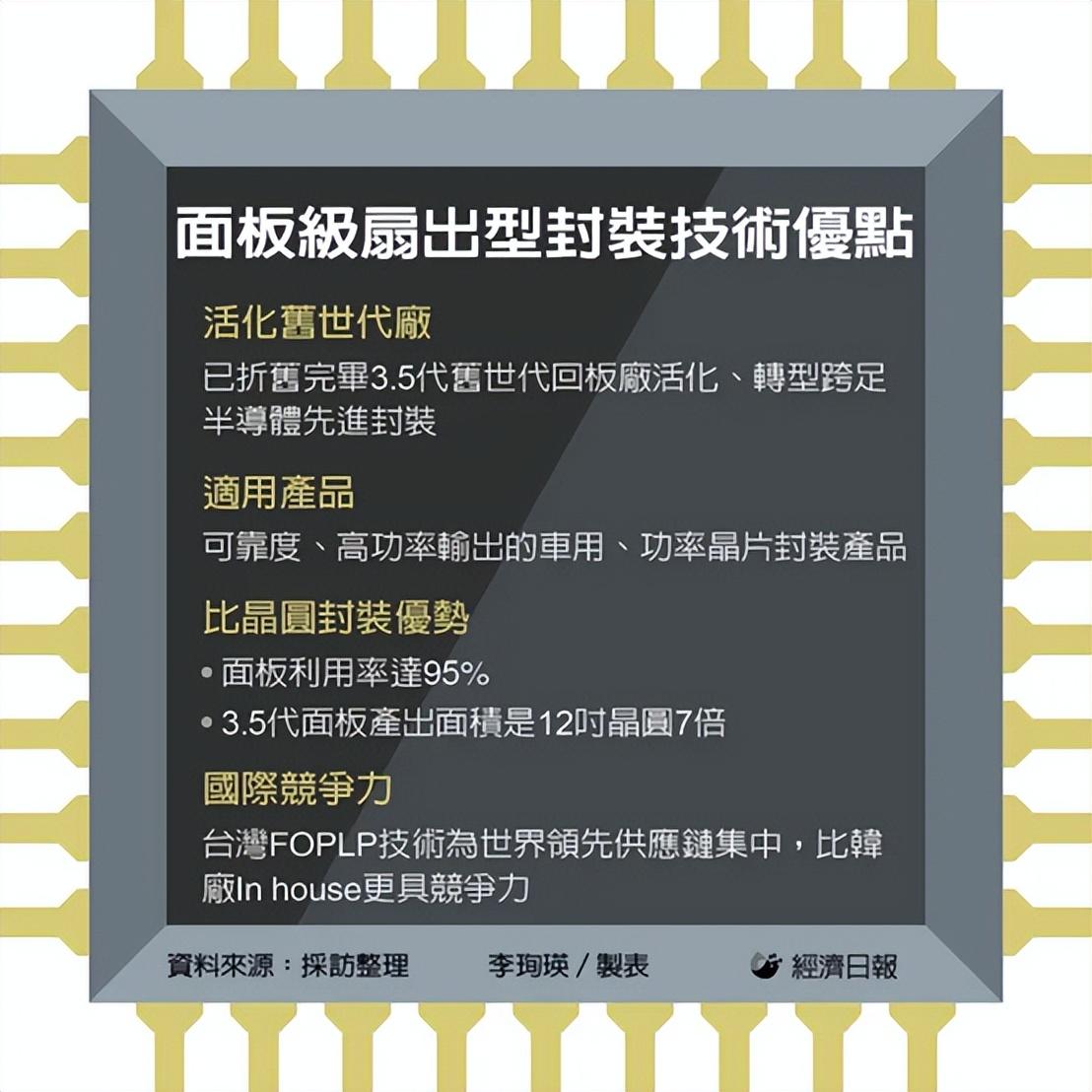

其利天下技術開發|目前先進的芯片封裝工藝有哪些

聯發科調整天璣9500芯片制造工藝

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

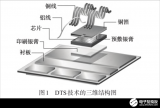

先進封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進展

晶圓廠與封測廠攜手,共筑先進封裝新未來

大廠群創華麗轉型全球最大尺寸FOPLP廠!先進封裝如此火熱,友達為何不跟進?

AI芯片制造新趨勢:先進封裝崛起

聚辰基于第二代NORD工藝平臺推出業界最小尺寸高可靠NOR Flash系列芯片

芯片鍵合:芯片與基板結合的精密工藝過程

成本過高致大量芯片廠暫緩先進工藝轉型!

成本過高致大量芯片廠暫緩先進工藝轉型!

評論