本文主要是關于tms320c6748的相關介紹,并著重tms320c6748的結構進行了詳盡的闡述。

tms320c6748

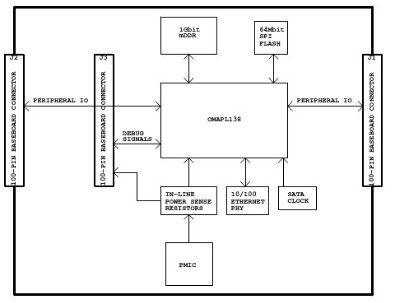

TMS320C6748是德州儀器 (TI) 推出浮點功能的全新高性能處理器 ,這款芯片也是業界功耗最低的浮點數字信號處理器 (DSP),可充分滿足高能效、連通性設計對高集成度外設、更低熱量耗散以及更長電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時也是 TI 首批集成串行高級技術附件 (SATA)的器件。 廣州創龍推出的TL6748-EVM評估套件為開發者使用TI TMS320C6748處理器提供了完善的軟件開發環境,系統支持:裸機、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開發包,以及詳細的C6748系統開發文檔,方便用戶快速評估TMS320C6748處理器、設計系統驅動及其定制應用軟件,也大大降低產品開發周期,讓客戶產品快速上市。主要面向電力、通信、工控、音視頻處理等數據采集處理行業。 TL6748-EVM評估套件是一個功能豐富的開發板,為嵌入式設計人員提供快捷簡單的實踐方式來評估TMS320C674x系列處理器,是一個完整的實驗評估平臺。

德州儀器 (TI) 推出浮點功能的全新高性能處理器 —— TMS320C6748,這款芯片也是業界功耗最低的浮點數字信號處理器 (DSP),可充分滿足高能效、連通性設計對高集成度外設、更低熱量耗散以及更長電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時也是 TI 首批集成串行高級技術附件 (SATA)的器件。

廣州創龍推出的TL6748-EVM評估套件為開發者使用TI TMS320C6748處理器提供了完善的軟件開發環境,系統支持:裸機、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開發包,以及詳細的C6748系統開發文檔,方便用戶快速評估TMS320C6748處理器、設計系統驅動及其定制應用軟件,也大大降低產品開發周期,讓客戶產品快速上市。主要面向電力、通信、工控、音視頻處理等數據采集處理行業。

TL6748-EVM評估套件是一個功能豐富的開發板,為嵌入式設計人員提供快捷簡單的實踐方式來評估TMS320C674x系列處理器,是一個完整的實驗評估平臺。

處理器

TMS320C6748圖冊TMS320C6748,C6000系列浮點DSP處理器(Pin to Pin兼容OMAPL138,AM1808處理器)

主頻:456MHz

存儲器

128M/256M/512MByte 工業級NAND Flash

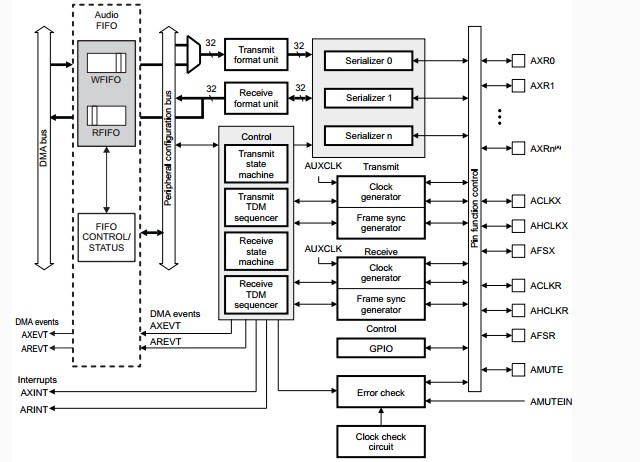

1個3.5mm Line in音頻輸入接口

1個3.5mm Mic in音頻輸入接口

1個3.5mm Line out音頻輸出接口

外設接口

串口、USB接口:

UART2,3線串口,RS232電平

1個RS485接口(RS485和UART1復用)

1 x USB2.0 OTG(Mini USB-B母座接口)

4 x USB1.1 HOST(2 x 雙層USB Type A座)

其他外設接口:

1個標準SD卡座(SD/MMC信號,支持1.8V及3.3V邏輯電壓)

1個SATA接口(7pin SATA硬盤接口)

1個RTC座(RC1220 RTC座)

1 個JTAG接口(14Pin TI Rev B JTAG接口)

擴展接口:(2x IDC3簡易牛角座(2x 25pin規格))

1路SPI總線

1路IIC總線

1路UART信號

1路VPIF總線

1路uPP總線

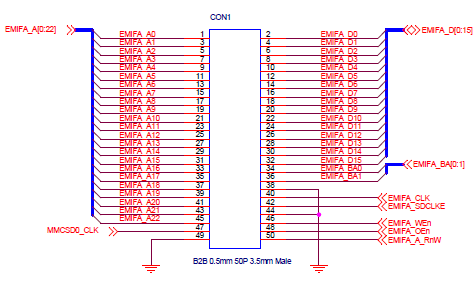

1路EMIF總線

可設置多個GPIO

輸入接口

1個非屏蔽中斷按鍵

1個可編程按鍵

1個復位按鍵

2個電源指示燈

1個系統指示燈

4個可編程指示燈

顯示單元

一個VGA接口

一個24bit真彩色LCD接口(50pinFPC排座;含4電阻式線觸摸屏接口,分辨率可支持1366x768)

電氣參數

工作電壓:3.8V~5.5V(典型值:5V)

工作溫度:-45~85℃

環境濕度:20% ~ 90% ,非冷凝

開發板:180mm*130mm

核心板:55mm*33mm

電氣指標:+5V@150mA

核心板功耗

電壓:5V

電流:98mA

功耗:0.49W

淺談tms320c6748最小系統設計和cache配置

處理器的cache是一塊存儲靠近處理器數據的高速存儲區。這幫助常用的指令和數據的快速訪問從而提高計算性能。Cache可以視為平坦式記憶體,即認為cache是CPU靠近的可以很快訪問的存儲器

存儲組織結構

圖1的左邊的模型是一個平坦式記憶體系統架構,假設CPU和片內存儲空間都運行在300 MHz,存儲訪問的延時只有在CPU訪問外存的時候才存在,而memory stall不會在訪問片內存儲區時發生。如果CPU的頻率是600 MHz,那么在訪問這部分片內存儲區的時候還是存在等待周期的。不幸的是,想在片內實現足夠大的存儲區能運行在600 MHz會非常昂貴的,如果仍然讓片內的存儲區運行在300 MHz,那么訪問這些存儲區的適合會有一個周期的延時。

一個解決方法是使用分層的存儲架構,有一個快速的靠近CPU的存儲區,訪問沒有stall但是size很小,往外的內存空間很大,但是離CPU較遠,訪問需要比較大的stall,靠近CPU的存儲區可以視為cache。

訪問定位的規律

當然,這種解決方案只有在CPU在大部分的訪問都是只針對最靠近它的存儲區時才是有效的,幸運的是,根據訪問定位的規律,這一條可以保證。訪問的定位規律表明程序在一個相對小的時間窗口對僅需要一個相對較小size的數據和代碼。數據定位的兩條規律:

?空間關聯性:當一個數據被訪問時,它臨近的數據又很大可能會被后續的存儲訪問;

?時間關聯性:一個存儲區被訪問時,在下一個臨近的時間點還會被訪問。

空間關聯性揭示了計算機程序的創建規律:通常情況下相關的數據被編譯鏈接到臨近的連續區域。例如首先處理一個數組的第一個元素,然后處理第二個,這就是空間關聯性。類似的,時間關聯性主要源于程序中存在占用時間非常多的循環,通常循環的代碼被連續執行非常多次,一般循環內訪問的數據也相當。

圖2是空間關聯性的說明,一個6-tap的FIR濾波器的數據訪問模式。如計算輸出y[0],從輸入緩沖區x[]讀取6個采樣點,當第一個訪問發生時,cache控制器讀取x[0]以及后續地址的若干個數據(取決于cache line的長度),從速度慢的存儲器加載一個cache line的數據需要一定的時鐘周期的CPU stall。這種加載的一個動機是x[0]后續的數據后面就要被訪問到。這個對于FIR濾波器是顯然的,因為后面的5個采樣點(x[1]-x[5])就要被用到。后面的這5次存儲訪問就只需要訪問高速cache就可以了。

當計算下一個輸出y[1]時,5個采樣點(x[1]-x[5])就可以重用了,只有一個采樣點(x[6])需要重新加載。所有的采樣點都在cache內了,訪問時不會有CPU stall了,這也就是剛才提到的時間關聯性,即上一步利用的數據在下一次處理中還是可能會被用到的。

Cache就是利用數據訪問的時間和空間關聯性建立的,它讓對速度較慢的外存的訪問次數盡可能的降低,而讓大部分的數據訪問都由更高層次的cache存儲區來完成。

存儲區的速度

Cache系統通常包含以下3級:

?第一級(L1)在CPU片內,運行在CPU時鐘頻率;

?第二級(L2)也在片內,但是比L1稍慢,容量較L1大;

?第三級 (L3)是外存,最慢容量也最大。

每一層次的cache有不同的數據訪問性能,相對的性能比較可以參考下面的表格。

當處理器從存儲區請求數據訪問時,首先在最高層次的cache內查找,然后再從次高級別的存儲區查找。當請求在cache內時就是cache命中,否則是一次cache miss。因而Cache系統的性能將取決于cache命中的比率。對于任意級別的cache,命中率越高性能越好。比如一個內存訪問的L1 cache命中率為70%,L2 20%, 其他來自L3,那么以圖3所示的性能下,平均一次內存的訪問時間為

(0.7 * 4) + (0.2 * 5) + (0.05 * 30) + (0.05 * 220) = 16.30 ns 考慮圖4所示的TI TMS320C64x DSP的存儲架構,兩級的片內cache加上片外外存。一級Cache分成程序(L1P)和數據(L1D) cache,每個容量為16 Kbytes。L1緩存數據訪問不會有存儲stall。L2存儲區分成L2 SRAM和L2 cache,無論是哪種配置,L2存儲區都需要兩個CPU周期完成一次數據訪問。不同的DSP,L2的容量不同,如TMS320C6454 DSP,L2的大小為1Mbytes。最后是C64x DSP最大高達2GBytes的外存,外存的訪問速度取決于使用的存儲器類型,但一般外存的頻率在100 MHz左右。圖4中的所有的cache(紅色)和數據通路都由cache控制器自動維護。

Cache的更新

Cache一直是主存的一個拷貝,因而需要cache能隨時反映主存的內容。如果數據在cache內被更新,而主存里沒有更新,這個cache內的數據就被稱為污染(dirty)數據,而數據在主存被更新但是cache內沒有更新,這時cache內的數據被稱為過時的(stale)數據。

Cache控制器使用一系列的技術來維護cache的一致性。偵聽“Snoop”和強制更新“snarf” 是兩種常用的技術。偵聽是讓cache決定主存內的數據的處理影響到被cache的地址的數據。強制更新是把數據從主存拷貝到cache存儲器。

Cache通常比主存容量小得多,因而cache最終總會被填滿,這時新進入的數據總要代替那些已經在cache內的數據了。有很多種策略決定那些已經在cache內的數據被代替更新如隨機代替,先進先出(FIFO)以及最遲不用的策略(LRU),大部分的處理器都采用LRU,即把least-recently-used數據替換為最新的數據。這種策略由于考慮到數據訪問的是時間相關性而非常有效。

直接映射的cache

Caches要么是直接映射的“direct-mapped”,要不就是組相關的“set-associative”。圖5是C64x的L1P cache,包含了512個32字節的cache lines。每個外存地址總是映射到同一個cache line,如:

?地址0000h 到 001Fh總是映射到cache line 0

?地址0020h 到 003Fh總是映射到cache line 1

?地址3FE0h 到 3FFFh總是映射到cache line 511.

當開始訪問地址4000h,cache容量被完全占用,因而地址4000h 到 401fh又映射到cache line 0.

為了保存從外存拷貝的數據信息,每個L1P的cache行包含如下信息:

?有效位,表明當前cacheline是否包含有效數據;

?標簽區域,對應于外存地址的高18位,由于每個cache行的數據可以由外存若干地址拷貝而來,如line 0保存可以來自地址0000h 到 001fh的數據也可以來自地址4000h 到 401fh。

?組號,對應于地址的5到13 bit;對于直接映射的cache而言,組號對應于cache line號。這個組號對于組相關的cache是非常復雜的。

當CPU開始訪問地址0020h時,假設cache已經被完全被設定無效了(invalidated),即沒有cache line包含有效數據。此時cache控制器開始根據當前地址的組(即地址的第5到13比特)來看對應的哪個cache line。對于地址0020h來說是cache line 1.然后cache控制器檢查line 1的標簽位,確認其是否對應于地址0020h到0039h,最后檢查有效位,發現其值為0,即該地址的數據并不在cache內,此時cache控制器標記一次cache miss。這次的miss讓控制器從外存加載整個cacheline(0020h-0039h),同時更新標簽tag位,并把有效位設置為1,同時加載的數據傳遞給CPU,此次數據訪問結束。

當還需要繼續訪問地址0020h時,cache控制器會繼續檢查組號和標簽域,并和存在標簽RAM的值比較,同時有效位的值為1,意味著此次是一個cache hit。

結語

關于tms320c6748的相關介紹就到這了,如有不足之處歡迎指正。

-

Cache

+關注

關注

0文章

129瀏覽量

28433 -

TMS320C6748

+關注

關注

3文章

42瀏覽量

13139

發布評論請先 登錄

相關推薦

TMS320C6748/C6748 DSP開發板——廣州創龍

【TL6748 DSP申請】基于TMS320C6748的視頻監控系統

求TMS320C6748相關資料

TMS320C6748 Fixed/Floating-Poi

TMS320C6748固定和浮點DSP硅修訂2.3_2.1_2.0_1.1_1.0_英版

TMS320C6748 TMS320C6748 Fixed/Floating Point DSP

tms320c6748主要參數和原理圖 tms320c6748 IO圖淺析

TMS320C6748和TMS320C6747芯片對比

TMS320C6748 OMAPL138核心板連接器引腳分布圖免費下載

德州儀器DSP的TMS320C6748技術手冊

使用TPS650061為TMS320C6742、TMS320C6746和TMS320C6748供電

淺談tms320c6748最小系統設計和cache配置

淺談tms320c6748最小系統設計和cache配置

評論