1 、引 言

電子產(chǎn)品的多樣性,小批量和周期性短是21世紀(jì)制造業(yè)的鮮明特征,對(duì)設(shè)計(jì)工作提出了更新更高的要求。如何在產(chǎn)品改進(jìn)或開(kāi)發(fā)新產(chǎn)品時(shí)減少重設(shè)計(jì)和修改設(shè)計(jì)的工作量,縮短設(shè)計(jì)周期、提高產(chǎn)品可靠性是制造行業(yè)面臨的重要課題。電子系統(tǒng)的柔性設(shè)計(jì)是采用電路結(jié)構(gòu)重置技術(shù),將多個(gè)針對(duì)不同功能要求設(shè)計(jì)好的配置文件分別存放在不同的地址空間,根據(jù)不同的外部命令,使所需的配置文件在線下載到具有重置功能的電子器件(如FPGA)中,以時(shí)分復(fù)用的形式分別完成各個(gè)功能。這種設(shè)計(jì)方式可以極大地提高電路系統(tǒng)的硬件功能靈活性。同一電路系統(tǒng)在沒(méi)有發(fā)生任何外在結(jié)構(gòu)上的改變時(shí),通過(guò)來(lái)自外部不同的命令信號(hào),電路系統(tǒng)的結(jié)構(gòu)和功能將在瞬間發(fā)生改變,從而使單一電路系統(tǒng)具有許多不同電路結(jié)構(gòu)的功能。

現(xiàn)場(chǎng)可編程門陣列FPGA是近十多年發(fā)展起來(lái)的新型可編程邏輯器件,利用FPGA的ICR特性進(jìn)行電路系統(tǒng)的柔性設(shè)計(jì),無(wú)疑將會(huì)減少重設(shè)計(jì)和修改設(shè)計(jì)的工作量、縮短系統(tǒng)的設(shè)計(jì)周期、提高系統(tǒng)的通用性和性價(jià)比,增強(qiáng)企業(yè)的競(jìng)爭(zhēng)能力。

2、 課題設(shè)計(jì)

設(shè)計(jì)一電子系統(tǒng),不改變電路結(jié)構(gòu)的條件下能夠分別完成溫度、電動(dòng)自行車速度和心率信號(hào)的測(cè)量與顯示,外加一個(gè)擴(kuò)展功能,設(shè)計(jì)具體要求如下。

(1) 測(cè)量結(jié)果用十進(jìn)制顯示,溫度的測(cè)量范圍0~100℃,電動(dòng)自行車速度的測(cè)量范圍0~0.60 km/min,心率測(cè)量范圍10~200跳/min;

(2) 測(cè)量值用3位數(shù)碼管顯示,小數(shù)點(diǎn)能自動(dòng)移動(dòng),且小數(shù)點(diǎn)左邊1位以上的零自動(dòng)熄滅;

(3) 具有超量程報(bào)警功能,在超出口前測(cè)量參數(shù)的測(cè)量范圍時(shí),發(fā)出燈光信號(hào);

(4) 電路結(jié)構(gòu)盡量簡(jiǎn)單。

3 、系統(tǒng)硬件設(shè)計(jì)

3.1 基于ICR技術(shù)的FPGA部分硬件電路設(shè)計(jì)

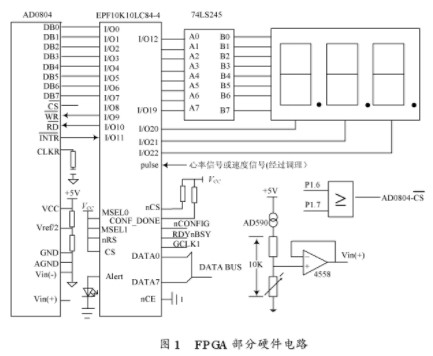

根據(jù)課題要求,設(shè)計(jì)FPGA部分硬件電路如圖1所示。FPGA芯片選用Altera公司的中檔器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT結(jié)構(gòu)的FPGA器件。根據(jù)傳送數(shù)據(jù)的方式,F(xiàn)LEX10K可以使用4種配置模式,即:主動(dòng)串行(AS)、被動(dòng)串行(PS)、被動(dòng)并行同步(PPS)、被動(dòng)并行異步(PPA)。由于PPA配置模式為并行配置,其配置速度快,且配置時(shí)鐘由FPGA內(nèi)部產(chǎn)生,更有利于在線實(shí)現(xiàn),本文就是采用PPA方式來(lái)實(shí)現(xiàn)電路系統(tǒng)的在線重構(gòu)。PPA方式配置時(shí)應(yīng)注意以下幾點(diǎn):

(1) 當(dāng)MESL0,MESL1均接高電平時(shí),為PPA模式。

(2) nCS和CS兩個(gè)片選信號(hào)只需用一個(gè),另一個(gè)必須將其直接置為有效位。

(3) nRS為讀選通輸人信號(hào),低輸人時(shí)引導(dǎo)FLEX-IOK將RDYnBSY信號(hào)置于DATA7引腳。當(dāng)nRS不用時(shí),必須將其置為高。

(4) nCE為FLEX10K器件的使能輸人,nCE為低時(shí)使能配置過(guò)程,而且為單片配置時(shí),nCE必須始終為低。

(5) DATA[7..0]接到AT89C52的P07~P00,nWS為寫選通輸人,由低到高的跳變時(shí)鎖存DATA[7..0]引腳上的字節(jié)數(shù)據(jù)。

(6) nSTATUS和CONF DONE引腳由于是雙向漏極開(kāi)路端口,所以在作輸出使用時(shí),應(yīng)該經(jīng)過(guò)1.0 kΩ的電阻上拉到VCC。其他細(xì)節(jié)可參考PPA配置方式的工作時(shí)序。

圖1中ADC0804是CMOS 8位單通道逐次漸近型的模/數(shù)轉(zhuǎn)換器,其主要性能指標(biāo)有:工作電壓+5 V、模擬輸入電壓范圍0~5 V、參考電壓2.5 V,分辨率8位。74LS245位總線收發(fā)器,用來(lái)加強(qiáng)數(shù)據(jù)總線的驅(qū)動(dòng)能力。

3.2 配置電路硬件設(shè)計(jì)及其工作原理

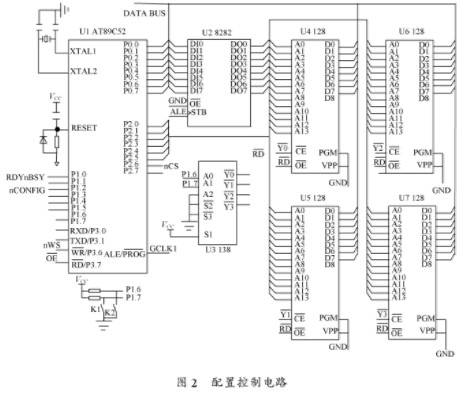

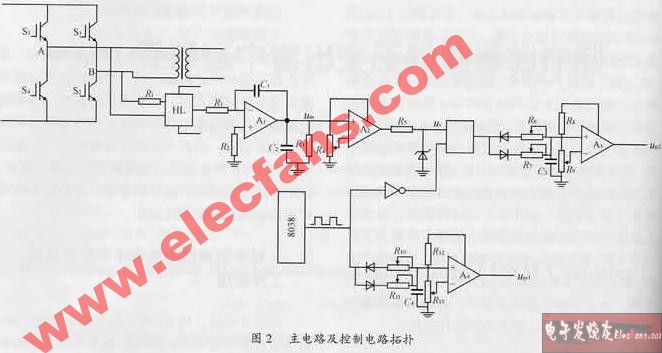

在FPGA的實(shí)際應(yīng)用中,用單片機(jī)來(lái)配置FPGA可以很好地解決系統(tǒng)保密和可升級(jí)的問(wèn)題。基于AT-MEL89C52的配置電路結(jié)構(gòu)如圖2所示。

3個(gè)不同功能的配置文件分別存放在3片外擴(kuò)程序存儲(chǔ)器27C128中,另外一個(gè)128用作進(jìn)一步擴(kuò)展時(shí)使用。K1,K2為功能選擇鍵,當(dāng)K1,K2同時(shí)閉合時(shí),系統(tǒng)實(shí)現(xiàn)溫度測(cè)量功能;K1閉合,K2打開(kāi)時(shí),系統(tǒng)實(shí)現(xiàn)轉(zhuǎn)速測(cè)量功能;K1打開(kāi),K2打開(kāi)閉合時(shí),系統(tǒng)實(shí)現(xiàn)心率測(cè)量功能。當(dāng)K1,K2同時(shí)打開(kāi)時(shí),作功能擴(kuò)展用。

4、系統(tǒng)軟件設(shè)計(jì)

4.1 FPGA配置文件的生成

使用開(kāi)發(fā)工具M(jìn)ax+PlusⅡ或QuartusⅡ可以生成多種配置編譯文件,用于不同配置方法的配置。對(duì)于不同的目標(biāo)器件,配置數(shù)據(jù)的大小不同。由于Altera公司提供的軟件工具不自動(dòng)生成.rbf文件,所以配置文件需按照下面的步驟生成:在Max+PlusⅡ編譯狀態(tài)下,選擇文件菜單中的變換SRAM目標(biāo)文件命令;在File Formatbox目標(biāo)文件對(duì)話框中指定要轉(zhuǎn)換的目標(biāo)文件.rbf,單擊OK即可。把各個(gè)功能的目標(biāo)文件按預(yù)定功能分別燒寫到EPROM27128中,且首地址設(shè)置為0002H。

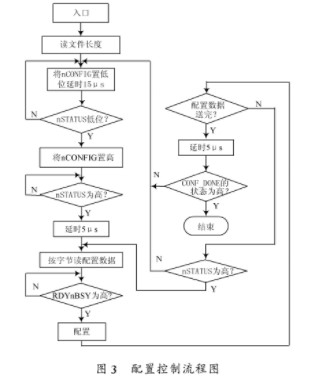

4.2 單片機(jī)實(shí)現(xiàn)配置過(guò)程的控制程序

該系統(tǒng)中單片機(jī)主要用來(lái)產(chǎn)生配置時(shí)序,所以首先要熟悉PPA方式配置FPGA的時(shí)序波形圖,才能設(shè)計(jì)出合理的單片機(jī)程序。由于篇幅的限制,這里僅給出單片機(jī)實(shí)現(xiàn)配置過(guò)程的控制程序流程如圖3所示,PPA配置方式的時(shí)序圖請(qǐng)參考Altera公司的器件資料。

5 、結(jié) 語(yǔ)

基于在線重置技術(shù),結(jié)合實(shí)例提出了電子系統(tǒng)的柔性設(shè)計(jì)。隨著微電子技術(shù)特別是EDA的飛速發(fā)展,這種方案將會(huì)在復(fù)雜電子系統(tǒng)的設(shè)計(jì)中得到廣泛采用。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606062 -

單片機(jī)

+關(guān)注

關(guān)注

6043文章

44621瀏覽量

638624 -

Altera

+關(guān)注

關(guān)注

37文章

787瀏覽量

154183

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

fpga的工作原理

數(shù)字LED技術(shù)工作原理及其應(yīng)用看了就知道

介紹LoRaWAN網(wǎng)關(guān)的技術(shù)基礎(chǔ)及其工作原理

ICR技術(shù)簡(jiǎn)介

抑制偏磁的簡(jiǎn)單電路拓?fù)?b class='flag-5'>及其工作原理

FPGA,FPGA工作原理是什么?

FPGA的工作原理及其基本特點(diǎn)

MOS管工作原理及其驅(qū)動(dòng)電路

FPGA多重配置硬件電路的原理及其設(shè)計(jì)方案的介紹

FPGA基礎(chǔ)知識(shí)及其工作原理與基本的功能塊案例

FPGA的硬件架構(gòu)和工作原理

PLC的硬件結(jié)構(gòu)配置與工作原理

基于ICR技術(shù)的FPGA配置電路硬件設(shè)計(jì)及其工作原理

基于ICR技術(shù)的FPGA配置電路硬件設(shè)計(jì)及其工作原理

評(píng)論