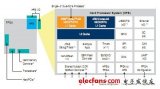

許多新式 FPGA 設計采用了一些用于控制的嵌入式處理器。一種典型解決方案需要使用諸如 NIOS 等嵌入式軟處理器。另一種解決方案則使用包含一個內置硬處理器的 SoC 器件。圖 1 示出了一個典型的 Altera FPGA 系統,該系統包含處理器和一系列通過 Avalon 內存映射 (MM) 總線連接的外設。這些處理器極大地簡化了最終應用,但是要求開發人員擁有堅實的編程背景和精細復雜工具鏈的相關知識。這會阻礙調試工作的推進,特別是如果硬件工程師需要一種不會煩擾軟件工程師即可完成外設讀寫的簡單方法。

圖 1:通過 Avalon 內存映射 (MM) 總線連接的典型 Altera FPGA 系統

該設計思想運用了 Altera 的 SPI 從端至 Avalon MM 橋接器,以提供一種跳上 Avalon 總線的簡單方法。采用這種方法有兩項優勢:它并未損害原始系統設計,而且該橋接器能夠與嵌入式處理器共存。對于圖 1 中所示的系統,SPI-Avalon MM 橋接器將允許設計師直接控制 LTC6948 分數 N PLL 的頻率,設定 LTC1668 DAC 電壓,從 LTC2498 讀取一個電壓,或者從 LTC2983 讀取溫度,就像處理器一樣。

圖 2:熒光筆 + 示例代碼 + 反向工程 = Python 腳本

Altera 提供了一款針對 SPI-Avalon MM 橋接器的參考設計。不幸的是,文檔充其量是稀少的,并且使用一個 NIOS 處理器作為 SPI 主控器。這實際上違背了 SPI 橋接器的初衷,因為 NIOS 處理器可直接連接至 Avalon MM 總線。一款實用的 SPI 主控器是凌力爾特的 Linduino?微控制器,它是具有附加特性的 Arduino 克隆產品,以與 LT 演示板相連接。附加特性之一是電平移位 SPI 端口。當連接至具有低至 1.2V 電壓的 FPGA I/O 塊時,這種電平移位功能是特別有幫助的。Linduino 固件可用于通過一個虛擬 COM 端口接受命令并把命令轉化為 SPI 事務處理。

在對 Altera 實例設計實施了反向工程之后 (圖 2 的左側),開發一個 Python 庫以生成橋接器將要接受的數據包。這些數據包隨后被轉化為 Linduino 命令。這樣,一個簡單的 Python 腳本使得硬件工程師能夠全面地控制項目,并不需要徹底改變接口協議。在 LinearLabTools Python 文件夾中提供了一個控制用于 LTC1668 DAC 的數字圖形發生器之頻率的 Python 腳本實例,可登錄獲取。圖 3 示出了演示設置。

圖 3:DC2459 在工作中

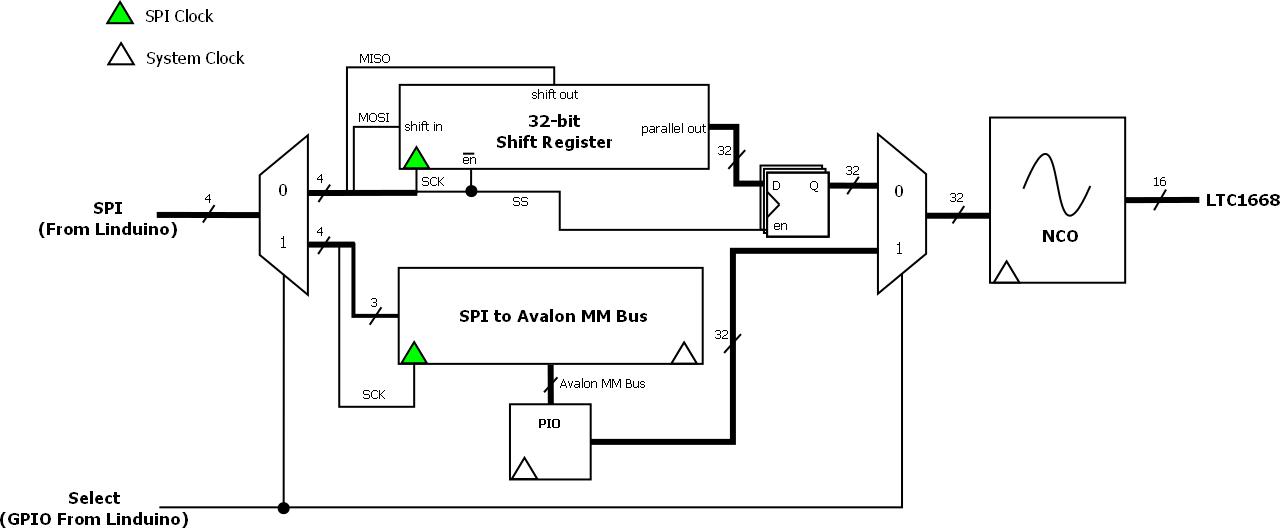

圖 4 給出了 FPGA 系統的方框圖。請注意,數控振蕩器 (DCO) 可由移位寄存器或 PIO 內核來控制。內置移位寄存器用于調試,因為它提供了 NCO 的直接控制。把 GPIO 線邏輯電平設定為“高”將使能 SPI-Avalon MM 橋接器,該橋接器接著通過 Avalon MM 總線控制一個 32 位 PIO 端口。然后,PIO 輸出控制 NCO 頻率。

圖 4:DC2459A FPGA 系統方框圖

當最基本的系統運行時,可以把額外的 Avalon 外設 IP 內核連接至 Avalon MM 總線。為了設計系統,Altera 提供了一款被稱為 Qsys 的系統集成工具。這款工具提供一個 GUI 以相互連接 IP。Qsys 隨后被用于把 GUI 系統轉化為硬件描述語言 (HDL) Verilog。圖 5 示出了該 GUI。最后,系統將被添加至用于實施的頂層。IP 的地址是完全可配置的。就給出的實例而言,PIO 被設定在一個 0x0 的基地址單元。

圖 5:Qsys GUI

一旦在 FPGA 中實現了設計,則 LinearLabTools 中提供的 Python 庫包含兩個函數以與設計接口:

transaction_write(dc2026, base, write_size, data)

transaction_read(dc2026, base, read_size)

這些函數的第一個參數是 Linduino 串行端口實例。第二個參數是外設在 Avalon 總線上的地址。這些函數分別接受和返還字節列表。編寫這兩個函數以在讀和寫 IP 時提供靈活性。如欲設定用于所提供實例的 NCO,則所需的就是 transaction_write 函數。

公式 1 用于確定頻率控制字。

公式 1:頻率控制字 = (期望的頻率/系統時鐘頻率) x 232

如欲把 NCO 設定至 1kHz 和一個 50Msps 采樣速率,則頻率控制字數值 = 85899。該數值用十六進制來表示即為 0x00014F8B,其作為一個 4 字節列表進行傳遞。于是,用于把 DAC 設定至 1kHz 的 Python 代碼為:

transaction_write(linduino_serial_instance, 0, 0, [0x0,0x01,0x4F, 0x8B])

注:根據邏輯設計,PIO 的基地址為零。

圖 6:Python Avalon 總線示例

提供了一個圖 6 所示的簡單 Python 腳本,以演示 FPGA 設計和 Python 腳本的接口。它包含一個簡單的文本接口以配置 NCO。一個重要提示是 Avalon SPI 橋接器采用 SPI Mode 3。這是痛苦地通過反復試驗而確定正確模式;并通過分析 Altera 實例中的 NIOS 處理器 SPI 接口進行驗證。

總括來說,該實例項目展示了完全無需“接觸”嵌入式處理器便可控制系統的能力。這讓硬件工程師不必麻煩軟件工程師就能在項目方面取得進展。這種方法的好處可以悄然地添加至 FPGA,并不會影響原始設計。硬件工程師可以把精力集中在硬件上。

-

處理器

+關注

關注

68文章

19409瀏覽量

231189 -

FPGA

+關注

關注

1630文章

21797瀏覽量

606020 -

嵌入式

+關注

關注

5092文章

19178瀏覽量

307694

發布評論請先 登錄

相關推薦

怎樣為自己的設計選擇Altera Cyclone V FPGA?

Altera發布面向FPGA的OpenCL解決方案 簡化FPGA開發

基于FPGA的多路PWM輸出接口設計

通過FPGA實現溫控電路接口及其與DSP通信接口的設計

Altera FPGA/CPLD設計(高級篇)

利用FPGA平臺解決接口的速度瓶頸

altera fpga/cpld設計

簡化Xilinx和Altera FPGA調試過程

Altera新Cyclone IV FPGA拓展了Cyclo

Altera公司SoC FPGA 簡介

具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

Altera FPGA CPLD學習筆記

通過Altera FPGA系統實現FPGA接口的簡化設計

通過Altera FPGA系統實現FPGA接口的簡化設計

評論