了解新的UltraScale ASIC時(shí)鐘架構(gòu):如何使用它,它帶來(lái)的好處以及從現(xiàn)有設(shè)計(jì)遷移的容易程度。 另請(qǐng)參閱如何使用時(shí)鐘向?qū)渲脮r(shí)鐘網(wǎng)絡(luò)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

asic

+關(guān)注

關(guān)注

34文章

1206瀏覽量

120753 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131501 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131797

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CPLD 與 ASIC 的比較

在數(shù)字電子領(lǐng)域,CPLD和ASIC是兩種廣泛使用的集成電路技術(shù)。它們各自有著獨(dú)特的優(yōu)勢(shì)和局限性,適用于不同的應(yīng)用場(chǎng)景。 1. 定義與基本原理 1.1 CPLD(復(fù)雜可編程邏輯器件) CPLD是一種

微服務(wù)容器化部署好處多嗎?

微服務(wù)容器化部署好處有很多,包括環(huán)境一致性、資源高效利用、快速部署與啟動(dòng)、隔離性與安全性、版本控制與回滾以及持續(xù)集成與持續(xù)部署。這些優(yōu)勢(shì)助力應(yīng)用可靠穩(wěn)定運(yùn)行,提升開(kāi)發(fā)運(yùn)維效率,是現(xiàn)代軟件架構(gòu)的優(yōu)質(zhì)選擇。UU云小編認(rèn)為微服務(wù)容器化部署好處

ASIC和GPU的原理和優(yōu)勢(shì)

? 本文介紹了ASIC和GPU兩種能夠用于AI計(jì)算的半導(dǎo)體芯片各自的原理和優(yōu)勢(shì)。 ASIC和GPU是什么 ASIC和GPU,都是用于計(jì)算功能的半導(dǎo)體芯片。因?yàn)槎伎梢杂糜贏I計(jì)算,所以也被稱(chēng)為“AI

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè)

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè).pdf》資料免費(fèi)下載

發(fā)表于 12-30 14:37

?2次下載

Verilog 與 ASIC 設(shè)計(jì)的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog與ASIC設(shè)計(jì)的關(guān)系 Verilog作為一種硬件描述語(yǔ)言(HDL),在ASIC設(shè)計(jì)中扮演著至關(guān)重要的角色。ASIC(Application Specific Integrated

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

的輸出,對(duì)于Ultrascale和Ultrascale+系列的器件,定時(shí)器會(huì)自動(dòng)地接入到GT的輸出。 1.2 約束設(shè)置格式 主時(shí)鐘約束使用命令create_clock進(jìn)行創(chuàng)建,進(jìn)入Timing

ASIC集成電路如何提高系統(tǒng)效率

在現(xiàn)代電子系統(tǒng)中,效率和性能是衡量一個(gè)系統(tǒng)優(yōu)劣的關(guān)鍵指標(biāo)。隨著技術(shù)的發(fā)展,ASIC集成電路因其高度定制化和優(yōu)化的特性,在提高系統(tǒng)效率方面發(fā)揮著越來(lái)越重要的作用。 ASIC的定義和特點(diǎn) ASIC是一種

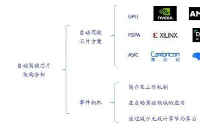

自動(dòng)駕駛?cè)笾髁餍酒?b class='flag-5'>架構(gòu)分析

當(dāng)前主流的AI芯片主要分為三類(lèi),GPU、FPGA、ASIC。GPU、FPGA均是前期較為成熟的芯片架構(gòu),屬于通用型芯片。ASIC屬于為AI特定場(chǎng)景定制的芯片。行業(yè)內(nèi)已經(jīng)確認(rèn)CPU不適用于AI計(jì)算

恩智浦MCU解讀 MCX A系列微處理器之時(shí)鐘架構(gòu)

全新的MCX A系列融合了恩智浦通用MCU的特點(diǎn),適用更為廣泛的通用應(yīng)用,實(shí)現(xiàn)了低成本,低功耗,高安全性和高可靠性。 今天,大家一起來(lái)了解一下MCX A最新產(chǎn)品的時(shí)鐘架構(gòu): MCXA153是MCX

發(fā)表于 06-20 09:21

?719次閱讀

PSoC63在CM0和CM4之間拆分BLE堆棧有什么好處?

在 PSoC63 中,在 CM0 和 CM4 之間拆分 BLE 堆棧有什么好處?

設(shè)計(jì)具有多個(gè)EVAL_PASCO2_SENSOR和 BLE 6EDL_SPI_LINK的系統(tǒng)時(shí),最佳實(shí)踐(或架構(gòu))是什么?

發(fā)表于 05-17 08:46

FPGA和ASIC兩者的設(shè)計(jì)流程

ASIC中你可以直接加寬金屬線(xiàn),比如兩倍寬度走時(shí)鐘線(xiàn),復(fù)位線(xiàn)啦,之類(lèi)的。金屬線(xiàn)寬度變大,線(xiàn)上的延遲變小,對(duì)速度也是有幫助的。

發(fā)表于 03-19 13:53

?975次閱讀

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 已經(jīng)擁有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不斷現(xiàn)代化。

發(fā)表于 03-18 10:40

?444次閱讀

UltraScale系列與7系列FPGA的差異

已從該架構(gòu)中移除BUFMRs、BUFRs、BUFIOs及其相關(guān)的路由資源,并被新的時(shí)鐘緩沖器、時(shí)鐘路由和全新的I/O時(shí)鐘架構(gòu)所取代。

PTP時(shí)鐘源設(shè)備全攻略:從普通時(shí)鐘到透明時(shí)鐘的進(jìn)階之路

在現(xiàn)代通信技術(shù)中,精確時(shí)間同步對(duì)于保障網(wǎng)絡(luò)性能至關(guān)重要。PTP(PrecisionTimeProtocol)時(shí)鐘源設(shè)備作為實(shí)現(xiàn)高精度時(shí)間同步的關(guān)鍵組件,其配置和選擇對(duì)于網(wǎng)絡(luò)架構(gòu)師和工程師來(lái)說(shuō)至關(guān)重要

單板上時(shí)鐘的注意事項(xiàng) 單板上時(shí)鐘晶體下面鋪地的好處

單板上時(shí)鐘的注意事項(xiàng) 單板上時(shí)鐘晶體下面鋪地的好處 單板上時(shí)鐘是指將時(shí)鐘晶體組件直接鋪裝在電路板上,這種設(shè)計(jì)方案在電子設(shè)備中廣泛應(yīng)用。在介紹

新UltraScale ASIC時(shí)鐘架構(gòu)的使用及好處

新UltraScale ASIC時(shí)鐘架構(gòu)的使用及好處

評(píng)論