2 蜂鳥E203開源SoC

對于一個處理器核,還需要配套的SoC才能具備完整的功能。 蜂鳥E203內核不僅僅完全開源了Core的實現,還搭配完整的開源SoC平臺,請參見《蜂鳥E203開源SoC簡介》(本篇即將發布,請持續關注公眾號;或點擊https://github.com/SI-RISCV/e200_opensource 查看詳情)了解更多SoC的介紹與信息。

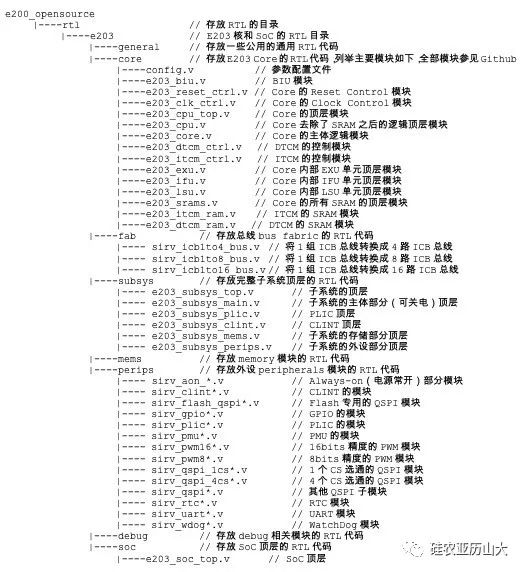

蜂鳥E203開源SoC的代碼結構如下所示。

各個主要的代碼模塊簡述如下:

general目錄主要用于存放一些通用的Verilog RTL模塊供整個SoC公用,譬如一些DFF(D觸發器寄存器)定義文件,ICB總線的基礎模塊等等。

core目錄主要用于存放處理器核模塊的Verilog RTL代碼。e203_cpu_top是蜂鳥E203處理器核的頂層。

fab目錄主要實現SoC中ICB Bus Fabric模塊的Verilog RTL代碼。 sirv_icb1to4_bus.v, sirv_icb1to8_bus.v或者sirv_icb1to16_bus.v實際例化調用了sirv_icb_splt模塊將一組ICB總線按照地址區間分發成為4組,8組或者16組ICB總線。

subsys目錄包含了SoC的主體頂層模塊的Verilog RTL代碼,其中e203_subsys_top是事實上的SoC頂層文件,它例化了Main Domain模塊(e203_subsys_main.v)和Always-onDomain模塊(e203_aon_top.v)。e203_subsys_mems模塊實現了系統存儲總線(System Memory Bus),通過調用例化sirv_icb1to8_bus模塊并且配置其參數的方式來配置每個從設備的地址區間。e203_subsys_perips模塊實現了系統設備總線(System Peripheral Bus),通過調用例化sirv_icb1to16_bus模塊并且配置其參數的方式來配置每個從設備的地址區間。除了已經實現的從設備,還預留了地址區間實現外部存儲(sysmem),外部外設(sysper)和外部快速IO(sysfio)總線接口。

mems目錄主要用于存放memory模塊的Verilog RTL代碼,由于Memory的具體實現依賴于芯片生產加工廠(foundry)譬如SIMC或者TSMC的Memory宏單元,因此本文件夾下的Verilog RTL代碼僅僅是行為模型。

perips目錄主要用于存放各種外設(Peripherals)模塊的Verilog RTL代碼,譬如GPIO,UART,SPI等。大部分的Peripherals的Verilog RTL代碼是直接復制于SiFive的Freedom E310項目中Chisel語言生成的出的Verilog RTL代碼,在此基礎上將其TileLink總線接口修改成了ICB總線接口,如圖3-5中所示的GPIO模塊ICB總線接口。

debug目錄包含了SoC中有關debugger調試器模塊的Verilog RTL代碼。

soc目錄主要用于存放SoC頂層模塊的Verilog RTL代碼。e203_soc_top.v是一個簡單地頂層SoC Wrapper模塊,將e203_subsys_top進行例化。另外由于e203_subsys_top模塊輸出的sysmem,sysfio和sysmem總線在此FPGA SoC中并沒有連接任何外部從設備。為了防止軟件程序訪問到這些總線接口的地址區間無任何返回而掛死,在e203_soc_top頂層模塊中將這些ICB總線的Command Channel信號直接反接到其Response Channel,同時將Response Channel中的其他返回信號連接成常數0。

3搭建FPGA原型平臺

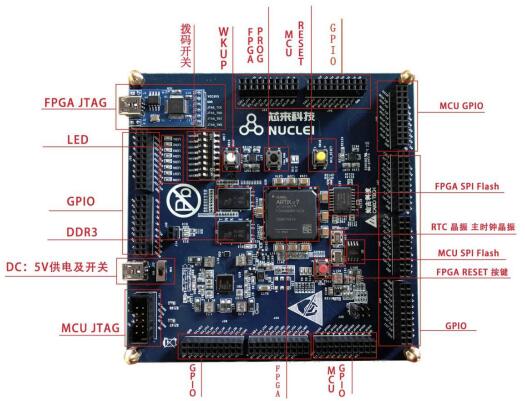

我們為蜂鳥E203開源SoC定制了專用的FPGA原型開發板和JTAG調試器, E203開源項目基于該FPGA開發板,使用蜂鳥E203開源SoC搭建完整的原型平臺與示例。

FPGA原型主要分為兩部分:FPGA開發板,和調試器。接下來章節分別予以介紹。完整的FPGA開發板原型(包括FPGA開發板和調試器)如圖3-1所示。

圖3-1 FPGA開發板原型(包括JTAG調試器)

3.1FPGA開發板和項目介紹

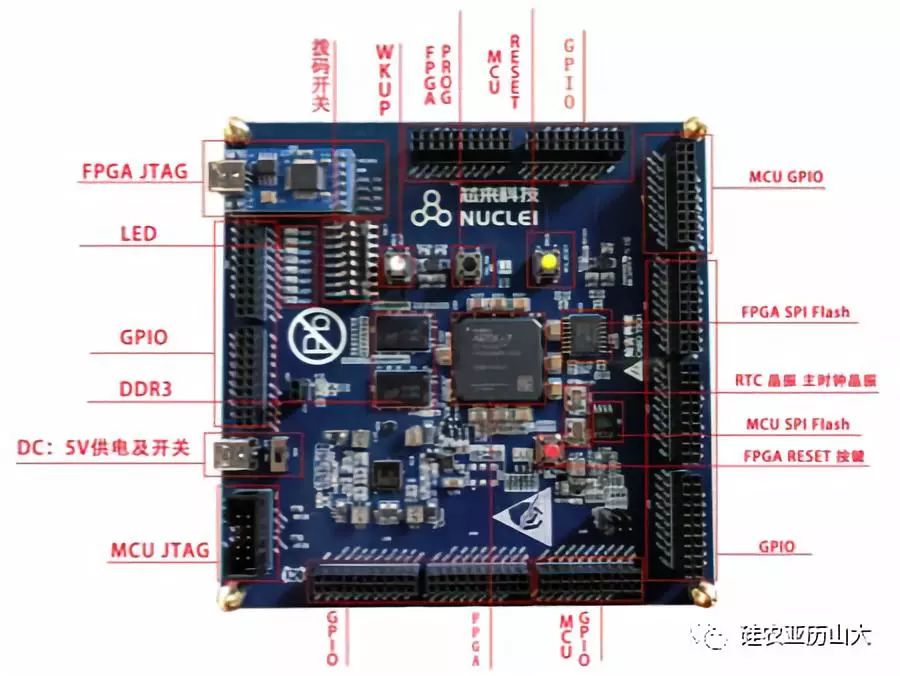

蜂鳥E203專用FPGA開發板是一款低成本的入門級XilinxFPGA開發板,如圖3-2所示。該開發板不僅可以用于一塊FPGA開發板作為電路設計使用,同時由于其預燒了蜂鳥E203開源SoC(包括E203內核),因此其可以直接作為一塊MCU SoC原型開發板進行嵌入式軟件開發。

有關此FPGA開發板的詳細介紹請參見《蜂鳥FPGA開發板和JTAG調試器介紹》。

若想購買此開發板,用戶可以在E203開源項目的Github網頁上(https://github.com/SI-RISCV/e200_opensource/tree/master/boards)了解此開發板的購買渠道。

圖3-2 蜂鳥E203專用FPGA開發板

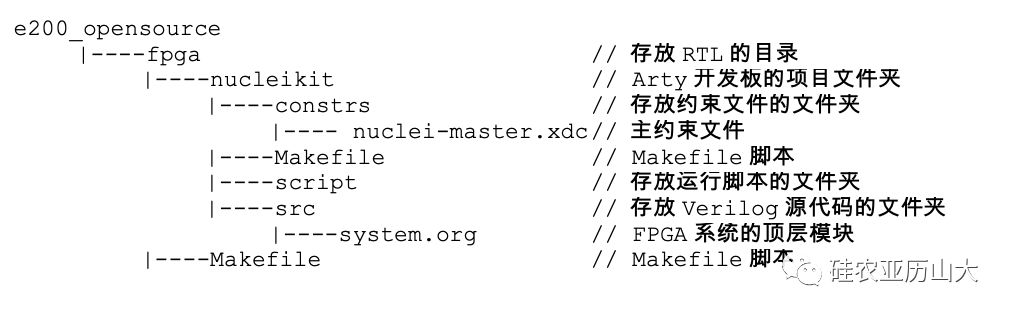

E203開源項目FPGA項目相關的代碼結構如下所示。

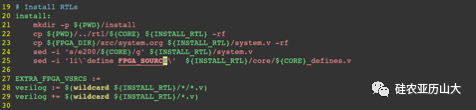

FPGA項目通過Makefile(fpga/common.mk文件)將添加一個特殊的宏FPGA_SOURCE至Core的宏文件中,如圖3-3所示。所以最終用于編譯FPGA比特流的RTL源代碼必須包含此宏(FPGA_SOURCE)。

圖3-3 FPGA項目宏定義文件中添加FPGA_SOURCE

在FPGA的頂層模塊(system.org)中除了例化SoC的頂層(e203_soc_top)之外,主要是使用Xilinx的I/O Pad單元例化頂層的Pad。另外使用Xilinx的MMCM單元生成時鐘。注意:SoC的MainDomain使用的MMCM產生的高速時鐘連接到SoC的hfextclk,Always-On Domain使用的是開發板上的低速實時時鐘(32.768KHz)。

蜂鳥E203開源SoC的頂層I/O Pad經過FPGA的約束文件(nuclei-master.xdc)進行約束使之連接到FPGA芯片外部的引腳上面(譬如將JTAG I/O約束到開發板的MCU_JTAG插口引腳上)。

3.2生成mcs文件燒寫FPGA

在前文中介紹了E203開源項目的SoC整體架構和Verilog RTL代碼,為了使得該SoC能夠真正運行在FPGA硬件上,需要將其編譯成為bitstream文件然后燒錄到FPGA中去。可以使用如下步驟進行編譯和燒錄。

//步驟一:準備好自己的電腦環境,可以在公司的服務器環境中運行,如果是個人用戶,推薦如下配置:

(1)使用VMware虛擬機在個人電腦上安裝虛擬的Linux操作系統。

(2)由于Linux操作系統的版本眾多,推薦使用Ubuntu16.04版本的Linux操作系統有關如何安裝VMware以及Ubuntu操作系統本文不做介紹,有關Linux的基本使用本文也不做介紹,請用戶自行查閱資料學習。

//步驟二:安裝Xilinx Vivado軟件至此虛擬機Linux操作系統中。有關如何安裝Xilinx Vivado軟件本文不做介紹,請用戶自行查閱資料了解。

//步驟三:將e200_opensource項目下載到本機Linux環境中,使用如下命令:

git clonehttps://github.com/SI-RISCV/e200_opensource.git

//經過此步驟將項目克隆下來,本機上即可具有如前文所述完整的e200_opensource目錄文件夾,假設該目錄為

//步驟四:設置需要編譯的Core的具體型號,使用如下命令:

cd

//進入到e200_opensource目錄文件夾下面的fpga目錄。

make install CORE=e203

//運行該命令指明需要為e203內核進行編譯,該命令會在fpga目錄下生成一個install子文件夾,在其中放置Vivado所需的腳本,且將腳本中的關鍵字設置為e203。

//步驟五:生成bitstream文件或者mcs文件(推薦使用mcs文件),使用如下命令:

make bit

//運行該命令將調用Vivado軟件對VerilogRTL進行編譯生成bitstream文件生成的bitstream文件名和路徑為

//熟悉Vivado和Xilinx FPGA使用的用戶應該了解,bitstream文件燒錄到FPGA中去之后FPGA不能掉電,因為一旦掉電之后FPGA燒錄的內容即丟失,需要重新使用Vivado的Hardware Manager進行燒錄方能使用。

//為了方便用戶使用,Xilinx的Arty開發板可以將需要燒錄的內容寫入開發板上的Flash中,然后在每次FPGA上電之后通過硬件電路自動將需要燒錄的內容從外部的Flash中讀出并燒錄到FPGA之中(該過程非常的快,不影響用戶使用)。由于Flash是非易失性的內存,具有掉電后仍可保存的特性,因此意味著將需要燒錄的內容寫入Flash后,每次掉電后無需使用Hardware Manager人工重新燒錄(而是硬件電路快速自動完成),即等效于,FPGA上電即可使用。有關此特性的詳細原理與描述,本文不做贅述,請用戶自行參閱Arty開發板手冊。

//為了能夠將燒錄FPGA的內容寫入Flash中,需要生成mcs文件,使用如下命令:

make mcs

//運行該命令將調用Vivado軟件對VerilogRTL進行編譯生成mcs文件生成的mcs文件名和路徑為

如何使用Vivado的HardwareManager燒寫mcs文件至FPGA開發板上的Flash中去,參考如下步驟。

//前提步驟1:將FPGA開發板的“FPGA JTAG接口”通過USB連接線與電腦的USB接口連接。開發板的“FPGA JTAG接口”的位置請參見圖3-2中標注所示。

//前提步驟2:將FPGA開發板的“DC:5V供電及開關”通過USB連接線與電腦USB接口或者電源插座連接,并將“開關”撥開,對FPGA開發板進行供電。開發板的“DC:5V供電及開關”的位置請參見圖3-2中標注所示。

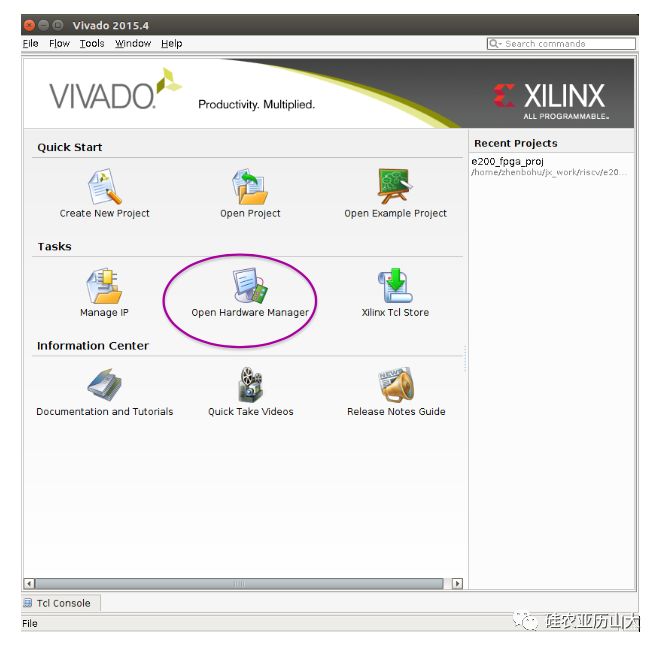

//步驟一:打開Vivado軟件。

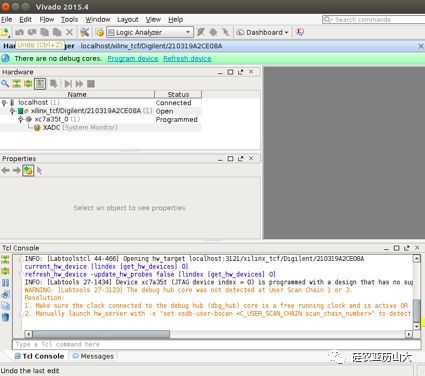

//步驟二:打開Hardware Manager,會自動連接FPGA開發板(如果前提步驟1操作正確)。如圖3-4和圖3-5所示。

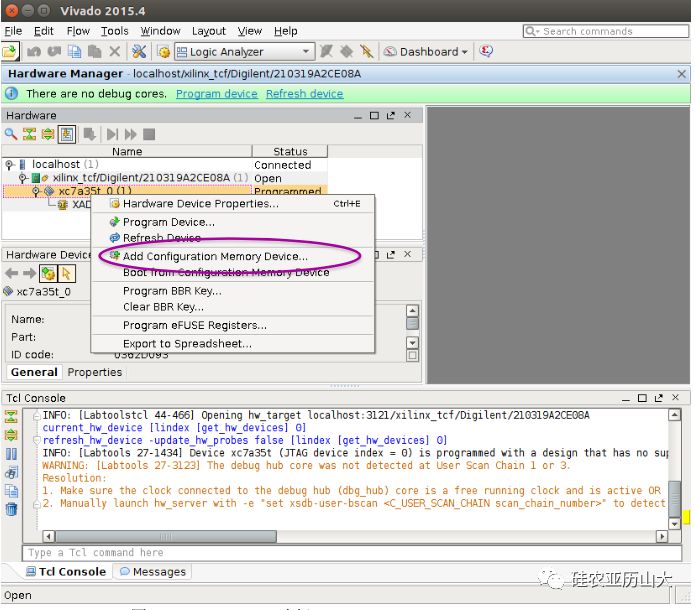

//步驟三:右鍵FPGA Device,選擇“Add Configuration Memory Device”。如圖3-6所示。

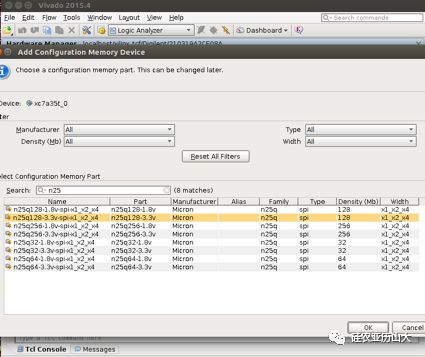

//步驟四:選擇如下參數的Flash,如圖3-7所示:

Part n25q128-3.3v

Manufacturer Micron

Family n25q

Type spi

Density 128

Width x1 x2 x4

//步驟五:彈出“Do you want to program the configuration memory device now?”,選擇OK

//步驟六:在彈出的窗口中的

//步驟七:一旦燒寫Flash成功,則可以通過按開發板上的“FPGA_PROG”按鍵觸發硬件電路使用Flash中的內容對FPGA重新進行燒錄。

注意:FPGA燒寫成功之后,則可以無需再連接“FPGA JTAG接口”的USB連接線。

圖3-4打開Vivado Hardware Manager

圖3-5使用Vivado Hardware Manager連接Arty開發板

圖3-6 FPGA Device選擇AddConfiguration Memory Device

圖3-7 選擇Flash類型

3.3JTAG調試器

圖3-8 蜂鳥E203專用FPGA開發板的MCU_JTAG插槽

為了支持使用GDB進行交互式調試或者通過GDB動態下載程序到處理器中運行,需要為FPGA原型平臺配備一個JTAG調試器(JTAG Debugger),E203內核支持通過標準的JTAG接口對其進行調試,且SoC頂層JTAG的I/O Pad連接到了 FPGA芯片的pin腳上,而該組pin腳在E203專用FPGA開發板上實際被連接到MCU_JTAG插槽上,如圖3-8中黃色圓圈所示。

我們為E203內核定制了專用的“JTAG調試器”,如圖3-9中黃色圓圈所示。

圖3-9 蜂鳥E203專用的JTAG調試器

有關此JTAG調試器的詳細介紹請參見《蜂鳥FPGA開發板和JTAG調試器介紹》。

若想購買此JTAG調試器,用戶可以在E203開源項目的Github網頁上(https://github.com/SI-RISCV/e200_opensource/tree/master/boards)了解此JTAG調試器的購買渠道。

由于“JTAG調試器”將其與上游主機PC的USB接口連接,因此上游PC的USB端口需要正確的設置以保證其有正確的權限。以Ubuntu 16.04為例,可以使用如下步驟進行配置。

//步驟一:準備好自己的電腦環境,可以在公司的服務器環境中運行,如果是個人用戶,推薦如下配置:

(1)使用VMware虛擬機在個人電腦上安裝虛擬的Linux操作系統。

(2)由于Linux操作系統的版本眾多,推薦使用Ubuntu16.04版本的Linux操作系統有關如何安裝VMware以及Ubuntu操作系統本文不做介紹,有關Linux的基本使用本文也不做介紹,請用戶自行查閱資料學習。

//步驟二:使用“JTAG調試器”將主機PC與FPGA開發板連接,如圖4-9中圓圈所示。注意使該USB接口被虛擬機的Linux系統識別(而非被Windows識別),如圖4-10中圓圈所示,若USB圖標在虛擬機中顯示為高亮,則表明USB被虛擬機中Linux系統正確識別(而非被Windows識別),將FPGA開發板通電。

//步驟三:使用如下命令查看USB設備的狀態:

lsusb //運行該命令后會顯示如下信息。

...

Bus 001Device 029: ID 15ba:002a Olimex Ltd. ARM-USB-TINY-H JTAG interface

//步驟四:使用如下命令設置udev rules使得該USB設備能夠被plugdev group所訪問:

sudo vi /etc/udev/rules.d/99-openocd.rules

//用vi打開該文件,然后添加以下內容至該文件中,然后保存退出。

# These arefor the Olimex Debugger for use with Arty Dev Kit

SUBSYSTEM=="usb",ATTR{idVendor}=="15ba",

ATTR{idProduct}=="002a",MODE="664", GROUP="plugdev"

SUBSYSTEM=="tty",ATTRS{idVendor}=="15ba",

ATTRS{idProduct}=="002a",MODE="664", GROUP="plugdev"

//步驟五:使用如下命令查看該USB設備是否屬于plugdev group:

ls /dev/ttyUSB* //運行該命令后會顯示類似如下信息。

/dev/ttyUSB0/dev/ttyUSB1

ls -l/dev/ttyUSB1 //運行該命令后會顯示類似如下信息。

crw-rw-r-- 1root plugdev 188, 1 Nov 28 12:53 /dev/ttyUSB1

//步驟六:將你自己的用戶添加到plugdev group中:

whoami

//運行該命令能顯示自己用戶名,假設你的自己用戶名顯示為your_user_name。運行如下命令將your_user_name添加到plugdev group中sudo usermod -a -G plugdev your user name。

//步驟七:確認自己的用戶是否屬于plugdev group:

groups //運行該命令后會顯示類似如下信息。

... plugdev...

//只要從顯示的groups中看到plugdev則意味著自己的用戶屬于該組,表示設置成功 。

圖3-10 虛擬機Linux系統識別USB圖標

在下一章將介紹利用該JTAG調試器如何使用GDB軟件對蜂鳥E203 SoC原型進行程序下載或遠程調試。

3.4 FPGA原型平臺DIY總結

至此,我們將以上論述的加以總結,為了能夠搭建完整的FPGA原型平臺,用戶需要做如下硬件的準備:

購買一塊蜂鳥E203專用FPGA開發板

購買一塊蜂鳥E203專用JTAG調試器

用戶需要做如下軟件的準備:

推薦安裝VMware虛擬機且安裝Linux操作系統于虛擬機中

安裝Xilinx的Vivado軟件

在下一章將介紹如何使用燒錄后的FPGA原型平臺運行真正的軟件示例。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

開發板

+關注

關注

25文章

5121瀏覽量

98190

原文標題:蜂鳥FPGA開發板全知道篇2:快速上手介紹(中)

文章出處:【微信號:real_farmer,微信公眾號:硅農亞歷山大】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

蜂鳥FPGA開發板及蜂鳥JTAG下載器講解說明

蜂鳥FPGA開發板及蜂鳥JTAG下載器講解說明

評論