前面簡(jiǎn)單介紹了ADC和DAC的基本結(jié)構(gòu),今天來(lái)看看ADC和DAC使用中要注意的要點(diǎn):

根據(jù)項(xiàng)目需要的性能進(jìn)行選型

選擇適合你項(xiàng)目的器件是第一步,因此你首先要知道都有哪些可供選擇,僅僅依賴搜索引擎是不夠的,你必須對(duì)主要的器件結(jié)構(gòu)、參數(shù)、廠商有全面的了解,一個(gè)簡(jiǎn)單的辦法就是到www.mouser.cn或www.digikey.com.cn按照分類進(jìn)行查看,如下圖,可以看到Mouser官網(wǎng)上的主要ADC、DAC的類別、供應(yīng)商以及按照關(guān)鍵參數(shù)進(jìn)行過(guò)濾得到的主要的器件型號(hào)。通過(guò)折騰這個(gè)選型表,你可以快速了解到ADC、DAC的大致情況。

半導(dǎo)體行業(yè)做ADC、DAC比較強(qiáng)的幾家公司的網(wǎng)站要經(jīng)常去溜達(dá)一下,看看他們都有啥,有什么新的器件出現(xiàn)等等。幸運(yùn)的是隨著不斷的收購(gòu)、整合,現(xiàn)在已經(jīng)沒(méi)剩下幾家了,但你至少應(yīng)該知道ADI、TI、美信(Maxim Integrated)、ST、Microchip等。

選型的時(shí)候需要考慮的幾個(gè)要點(diǎn):

模擬帶寬和采樣率(ADC)或轉(zhuǎn)換率(DAC),時(shí)鐘的類型 - 單端、差分?

分辨率,也就是用多少位的轉(zhuǎn)換器件。前面我專門講述了根據(jù)系統(tǒng)的要求以及信噪比、失真等對(duì)ADC位數(shù)和前端模擬鏈路的綜合平衡設(shè)計(jì),DAC的位數(shù)選擇也是一樣的原則,不是位數(shù)越高性能就越好,到了一定的程度就受限于板子上的噪聲和器件的失真了

數(shù)據(jù)接口方式 - 高速轉(zhuǎn)換器才用并行接口還是串行接口?一般低速的轉(zhuǎn)換器基本都采用SPI或I2C的串行接口方式,高速的器件采用并行接口以及高速串行接口

供電 - 5V?3.3V?1.8V?等,要根據(jù)自己系統(tǒng)的供電情況選用合適供電電壓的器件

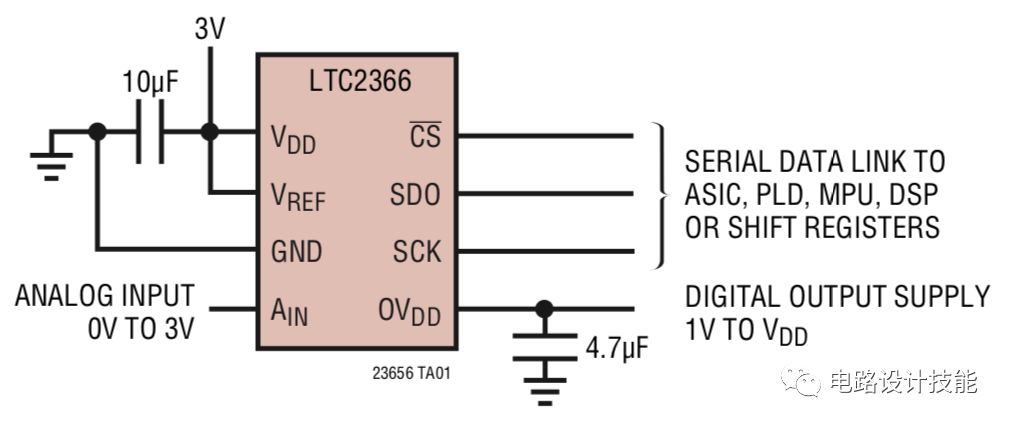

一旦選定了器件就進(jìn)入了設(shè)計(jì)部分,我們以一顆串行的ADC(LTC2366)和一顆高速并行的DAC(AD9760)來(lái)簡(jiǎn)單看一下設(shè)計(jì)中要注意的一些事宜:

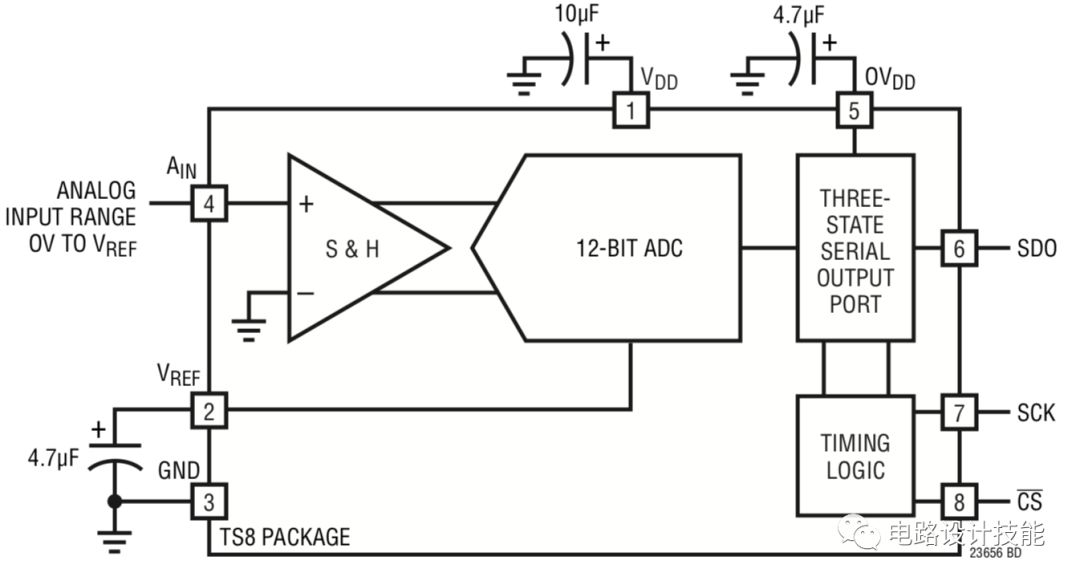

先通過(guò)框圖閱讀一下器件:

串行ADC - LTC2366:3Msps、12位取樣ADC

單端模擬信號(hào)輸入 - 輸入電壓范圍為0-Vref(參考電壓)

在簡(jiǎn)單的使用場(chǎng)景,參考電壓管腳直接連接在器件的供電電壓管腳上,當(dāng)然也可以外接參考電壓源 - 增加成本,但可以帶來(lái)靈活性

SPI串行數(shù)據(jù)接口,要注意的是SPI的時(shí)鐘頻率和器件的轉(zhuǎn)換率是兩個(gè)概念,器件能夠以3Msps的速率轉(zhuǎn)換,SPI要把這3Msps、12bit的數(shù)據(jù)傳輸出來(lái),至少要48MHz的時(shí)鐘頻率

供電電壓范圍比較寬,設(shè)計(jì)的從2.35V到3.6V之間都可以正常工作,也就是我們常用的2.5V、3V和3.3V供電系統(tǒng)都可以使用

關(guān)鍵的管腳上都要有去偶電容,由于模擬信號(hào)的頻率比較低,使用的電容一般為4.7uF - 10uF的鉭電容(注意是有極性的)

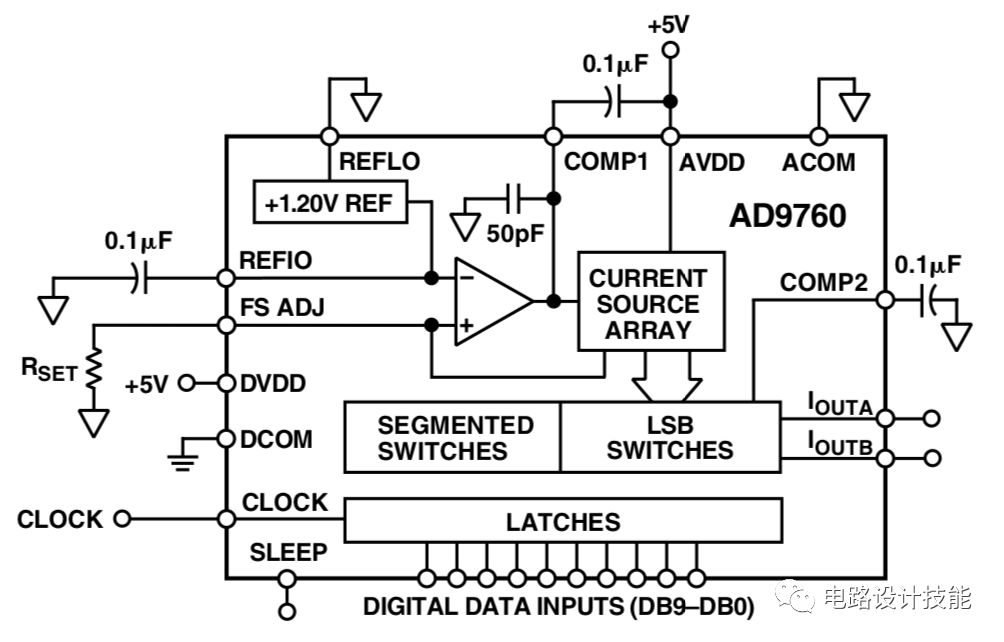

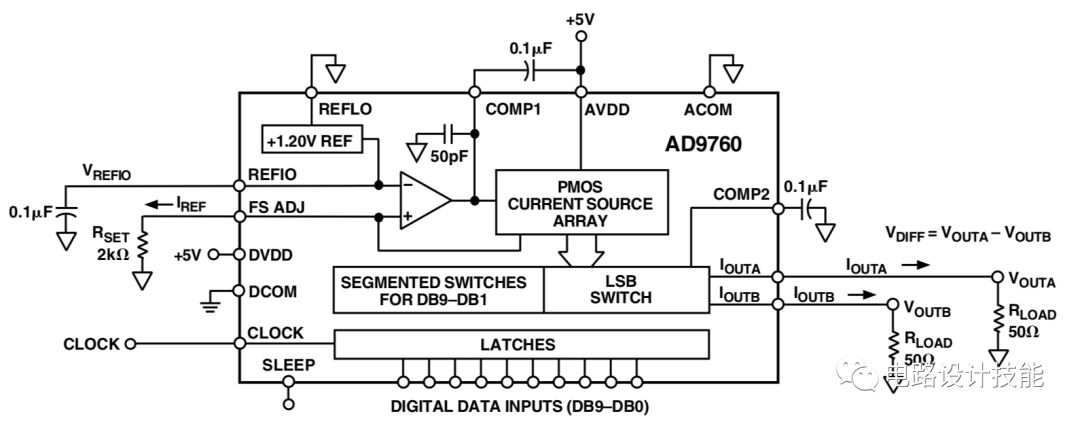

并行DAC - AD9760:

10位并行數(shù)據(jù)接口、時(shí)鐘為單端輸入

模擬信號(hào)為差分輸出,在輸出端需要差分轉(zhuǎn)單端模擬電路

+5V電壓供電 - 數(shù)字電源DVDD、模擬電源AVDD,數(shù)字地DCOM、模擬地ACOM

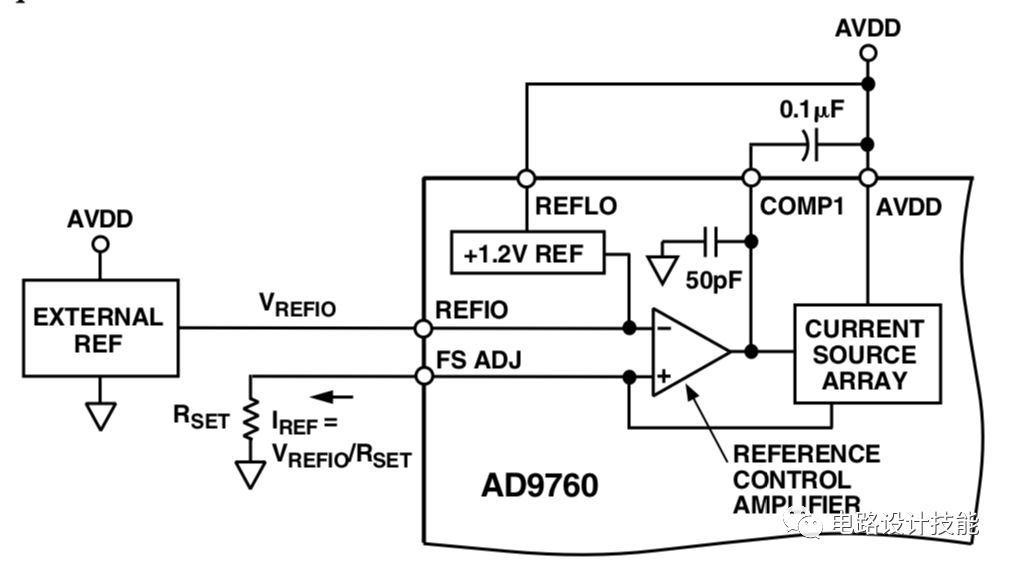

內(nèi)部1.2V參考電壓并通過(guò)外界的Rset來(lái)設(shè)定比較電流,可以通過(guò)改變Rset調(diào)節(jié)模擬輸出的電流大小

幾個(gè)重要的管腳接有0.1uF去偶電容,上面的低速串行ADC的去偶電容選用比較大的值,在這個(gè)高速的DAC電路里則選用0.1uF的陶瓷電容,最好是0603或更小的封裝

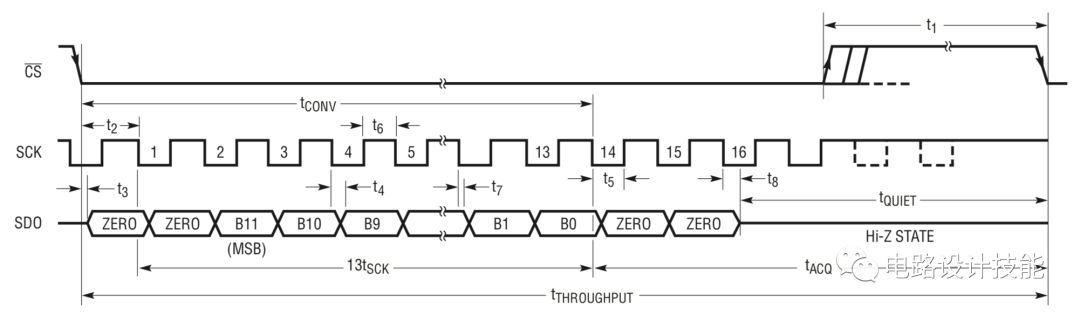

數(shù)據(jù)接口的時(shí)序以及時(shí)鐘的選用:

前面我們講過(guò)低速串行的器件一般采用I2C或SPI,在LTC2366中采用的是SPI接口,在數(shù)據(jù)手冊(cè)中一定要查看其時(shí)序圖,了解其SPI的工作模式 - 4種模式種的哪一種?從這個(gè)時(shí)序圖可以看出傳輸一次取樣的數(shù)據(jù)至少需要16個(gè)SPI的時(shí)鐘周期,也就是如果你的ADC轉(zhuǎn)換率為3Msps,SPI的時(shí)鐘周期至少要在48MHz以上,要保留一定的保護(hù)時(shí)間,最好選擇在50MHz以上,如果SPI的時(shí)鐘受限,不能工作到較高的速率,比如最高只能到30MHz,那么ADC的采樣率也就要相應(yīng)降低,以確保轉(zhuǎn)換完的數(shù)據(jù)都能夠傳遞出來(lái)。

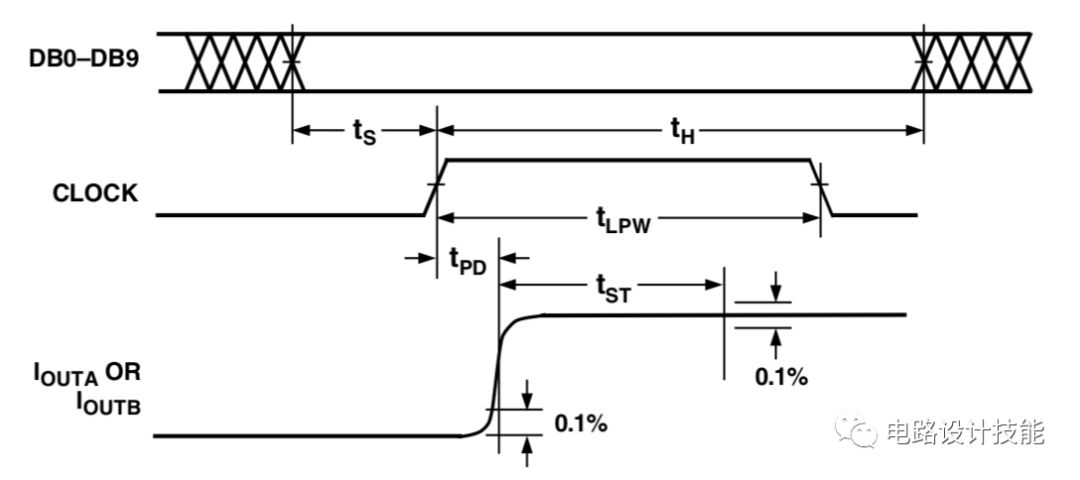

AD9760的時(shí)序圖如下,可以看出數(shù)據(jù)的轉(zhuǎn)換是由時(shí)鐘的上升沿來(lái)驅(qū)動(dòng)的,因此在連接AD9760的前方邏輯電路中一定要注意時(shí)鐘上升沿的跳變要在10根數(shù)據(jù)穩(wěn)定了以后才行,如果時(shí)鐘的上升沿與數(shù)據(jù)的改變同時(shí)發(fā)生,DAC器件就會(huì)瘋掉,出來(lái)的數(shù)據(jù)全部亂掉。ts是個(gè)很重要的指標(biāo),如果你前面的邏輯輸出信號(hào)經(jīng)過(guò)PCB上較長(zhǎng)的走線到達(dá)DAC導(dǎo)致有的數(shù)據(jù)線和時(shí)鐘之間的ts不能滿足器件數(shù)據(jù)手冊(cè)的要求,轉(zhuǎn)換就會(huì)出現(xiàn)錯(cuò)誤。因此并行傳輸?shù)腄AC在布線的時(shí)候數(shù)據(jù)、時(shí)鐘線一定要滿足時(shí)序的要求。

參考電壓的使用

無(wú)論ADC還是DAC都是通過(guò)跟一個(gè)基準(zhǔn)(電壓或電流)進(jìn)行比較而得到相應(yīng)的結(jié)果的,如果基準(zhǔn)發(fā)生了偏差,那結(jié)果自然也就是錯(cuò)誤的,因此在電路中要確保你基準(zhǔn)電壓或電流的準(zhǔn)確性、穩(wěn)定性,轉(zhuǎn)換的結(jié)果也要根據(jù)具體的基準(zhǔn)值來(lái)進(jìn)行標(biāo)定。

如下圖,LTC2366的Vref同3V的電源電壓連接在一起,意味著能夠轉(zhuǎn)換的模擬電壓滿量程為3V(最小采樣精度為3V/4096 ~ 0.73mV),因此可以通過(guò)改變Vref的值來(lái)改變被測(cè)模擬信號(hào)的精度,比如選用1.5V做Vref測(cè)量信號(hào)的精度將提高一倍(0.36mV),如果3V的供電電壓上有1%的紋波,意味著ADC的參考電壓也有這1%的波動(dòng),12位的ADC實(shí)際上還達(dá)到7位的準(zhǔn)確度。要能夠?qū)?.73mV的電壓都能分辨,要求3V上的紋波一定也要低于0.73mV。

AD9760的參考電壓可以外接,也可以直接使用內(nèi)部的1.2V的參考電壓,DAC轉(zhuǎn)換的時(shí)候是以Vref/Rset得到的電流為基準(zhǔn),因此在同樣的數(shù)字值的情況下,通過(guò)調(diào)節(jié)Vref或Rset就可以改變轉(zhuǎn)換后的模擬量。很多DDS任意信號(hào)發(fā)生器都通過(guò)調(diào)節(jié)這兩個(gè)值來(lái)對(duì)輸出電平進(jìn)行程控調(diào)節(jié),有些DAC器件還可以通過(guò)SPI接口配置內(nèi)部的控制寄存器從而改變參考電流的大小,進(jìn)而改變輸出模擬信號(hào)的大小。

要注意的是參考電壓管腳一定要加去偶電容電容,LTC2366加10uF的鉭電容濾除比較低頻率的電源噪聲,AD9760則由0.1uF的陶瓷電容實(shí)現(xiàn)干擾噪聲的高頻旁路。

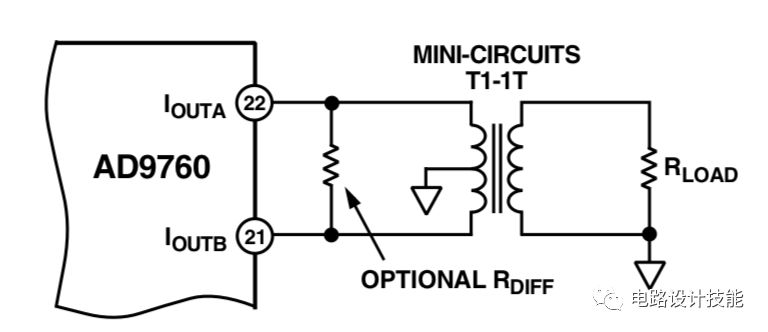

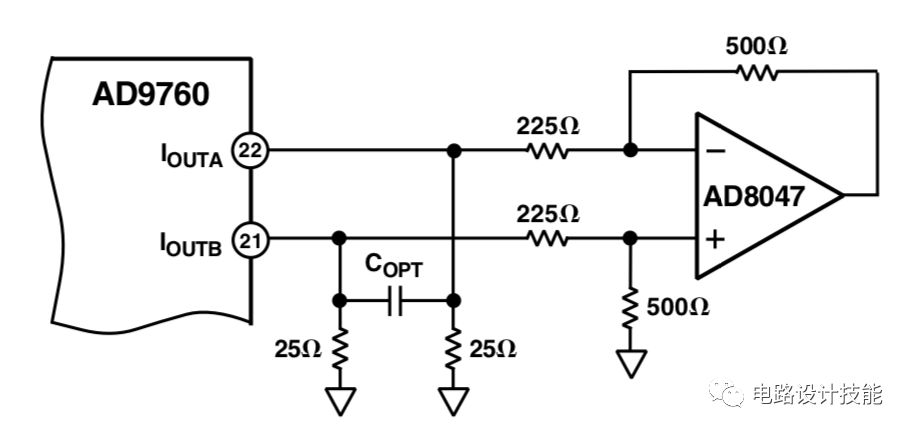

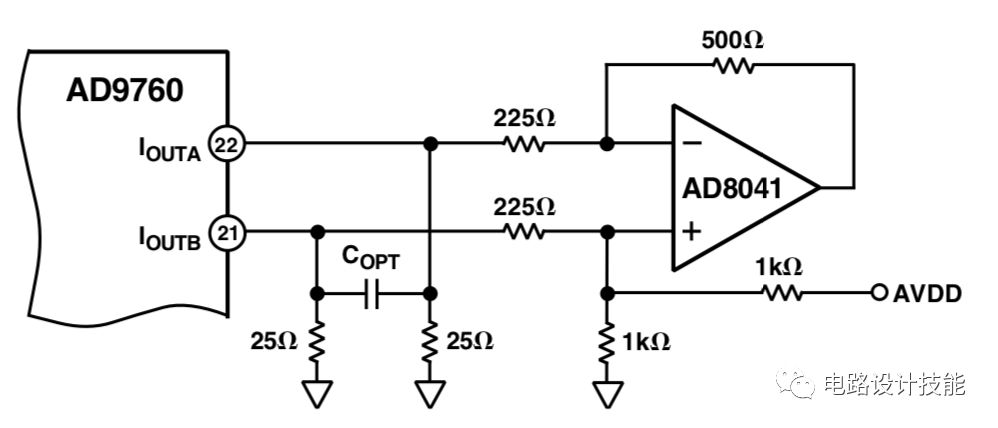

高速DAC的模擬差分輸出:

就像其它高速DAC一樣,AD9760轉(zhuǎn)換后的模擬信號(hào)采用差分電流(IoutA、IoutB)輸出的方式,因此在DAC之后需要由差分轉(zhuǎn)換為單端的電路,有以下的方式可供選擇:

通過(guò)1:1射頻變壓器實(shí)現(xiàn),要注意的是一定要保證變壓器的帶寬滿足輸出模擬信號(hào)帶寬的要求,變壓器的有點(diǎn)是“無(wú)源”也就是不需要供電電壓,結(jié)構(gòu)非常簡(jiǎn)單,缺點(diǎn)就是體積比較大,尤其是高度,在有些場(chǎng)合使用起來(lái)比較突兀。

通過(guò)運(yùn)算放大器 - 要注意運(yùn)算放大器的模擬帶寬、擺率能滿足輸出信號(hào)帶寬的要求,運(yùn)放的好處是體積比較小,缺點(diǎn)是必須提供非常低紋波的供電電壓,尤其是雙軌的電壓,為此還要設(shè)計(jì)線性穩(wěn)壓的雙路供電電路,電路變得復(fù)雜起來(lái)。

如果你實(shí)在不想在板子上折騰出一個(gè)負(fù)電壓(比如-5V或-3V),只想使用板子上的單路正電壓,可以使用下面的連接方式。

布局布線中的考慮

ADC和DAC都是連接模擬和數(shù)字的橋梁,注定了它們都是模數(shù)混合的器件,它們都分模擬部分和數(shù)字部分。

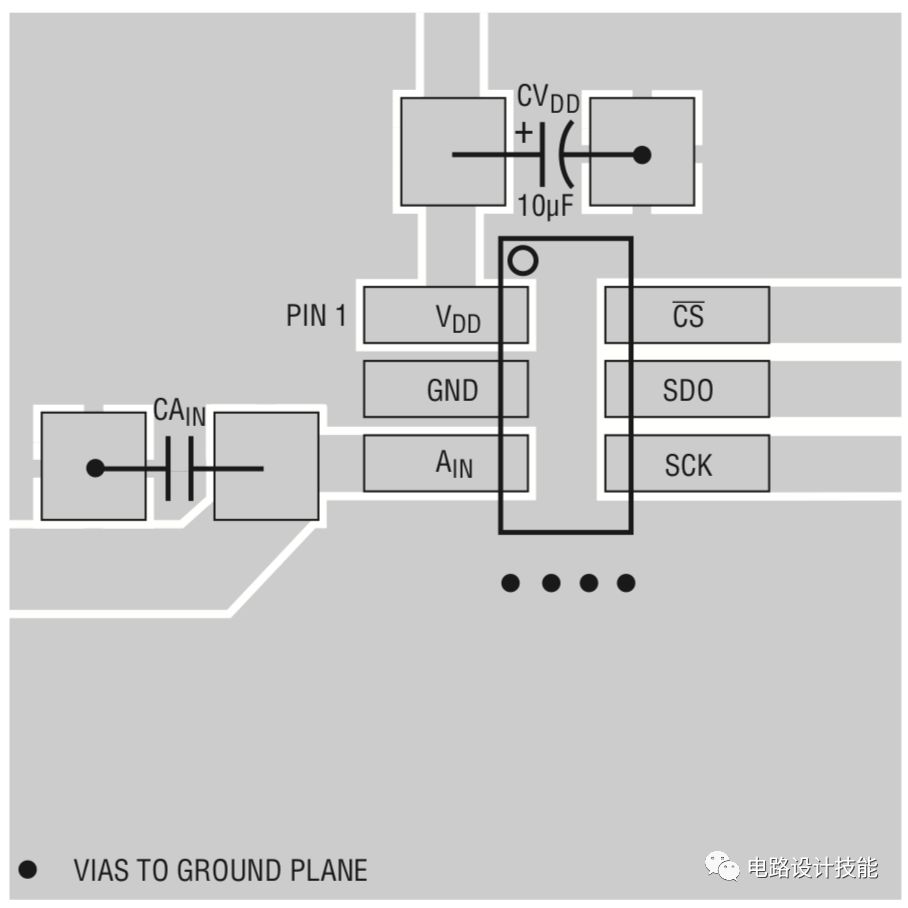

細(xì)心的工程師可能已經(jīng)發(fā)現(xiàn) - LTC2366的供電電壓和地只有一個(gè),也就是說(shuō)沒(méi)有區(qū)分模擬和數(shù)字,why?一個(gè)原因是這種器件定位的就是“小”,管腳盡可能“少”,只要不影響系統(tǒng)的性能,將模擬和數(shù)字合并在一起也沒(méi)有問(wèn)題。畢竟低速的ADC或DAC內(nèi)部的轉(zhuǎn)換邏輯速率都很低,由此產(chǎn)生的開(kāi)關(guān)噪聲也相對(duì)低很多,只要注意在電源上做比較好的去偶,也能夠保證轉(zhuǎn)換的性能。當(dāng)然在布局布線的時(shí)候也是要盡可能注意去偶電容的擺放位置以及地平面的分割,參見(jiàn)下面的LTC2366的參考Layout圖。

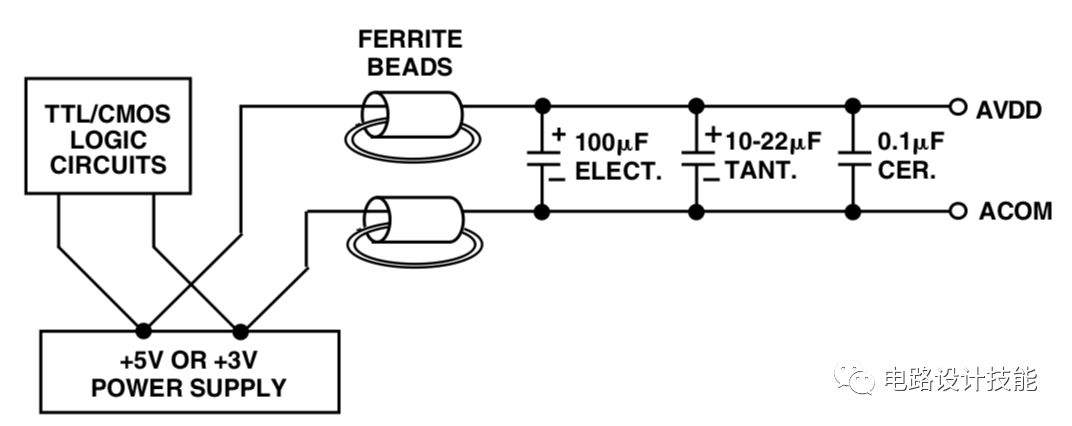

對(duì)于AD9760由于數(shù)據(jù)接口速率以及轉(zhuǎn)換速率非常高,達(dá)到了100M,因此模擬電源、地和數(shù)字電源、地都是分隔開(kāi)的,中間用磁珠進(jìn)行了隔離,我們前面的文章中已經(jīng)專門介紹過(guò)磁珠的應(yīng)用。注意在模擬電源部分使用了3個(gè)容值不同的去偶電容

100uF的電解電容用于極低頻率的噪聲抑制

10~22uF的鉭電容用于較低頻率的開(kāi)關(guān)噪聲抑制,一般由板子上的開(kāi)關(guān)電源噪聲導(dǎo)致

0.1uF的陶瓷電容用于較高頻率的噪聲抑制,比如其它數(shù)字開(kāi)關(guān)電路導(dǎo)致的噪聲等

很多MCU內(nèi)部都集成了ADC和DAC,使用起來(lái)更方便,但要注意的是雖然這些器件標(biāo)稱的轉(zhuǎn)換率比較高,但由于MCU工作于多任務(wù)的情況下沒(méi)有可能實(shí)時(shí)處理轉(zhuǎn)換完的數(shù)據(jù),因此需要內(nèi)部有一定的存儲(chǔ),如果沒(méi)有存儲(chǔ)或者可供轉(zhuǎn)換數(shù)據(jù)的存儲(chǔ)RAM空間很小,實(shí)際的轉(zhuǎn)換頻率會(huì)大打折扣,比如ESP32這個(gè)器件其標(biāo)稱的ADC轉(zhuǎn)換率和實(shí)際使用中能夠真正達(dá)到的轉(zhuǎn)換率相差好幾個(gè)數(shù)量級(jí),原因就是處理器的主營(yíng)業(yè)務(wù)是做其它的調(diào)度,根本沒(méi)有時(shí)間來(lái)理你,偶爾來(lái)讓你查看一下外部的模擬電壓值而已,即便你能跑的很快,但多數(shù)時(shí)間是讓你在那里站著。

因此多數(shù)情況下就需要選用獨(dú)立的ADC、DAC,并通過(guò)FPGA配以適當(dāng)容量的RAM來(lái)進(jìn)行存儲(chǔ),在MCU的眼里ADC、DAC永遠(yuǎn)都是偶爾處理一下的外設(shè),給你一次被臨幸的機(jī)會(huì),你就要讓它一次吞吐個(gè)夠。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8745瀏覽量

148064 -

adc

+關(guān)注

關(guān)注

99文章

6534瀏覽量

545772

原文標(biāo)題:ADC/DAC(4)- 設(shè)計(jì)中須注意的要點(diǎn)

文章出處:【微信號(hào):xiaojiaoyafpga,微信公眾號(hào):電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

雙絞線布線要注意哪些要點(diǎn)

請(qǐng)問(wèn)ADC或DAC和DSP相連接時(shí)要注意什么?

電機(jī)驅(qū)動(dòng)MCU技術(shù)有哪些要點(diǎn)需要注意?

嵌入式系統(tǒng)設(shè)計(jì)時(shí)需要注意的技術(shù)要點(diǎn)和實(shí)現(xiàn)細(xì)節(jié)有哪些?

使用STM32 DAC模塊時(shí)要注意哪些細(xì)節(jié)

注意ADC和DAC使用

pcb設(shè)計(jì)中需要注意哪些問(wèn)題?

ADC/DAC,ADC/DAC的原理是什么?

經(jīng)驗(yàn)總結(jié):5個(gè)FPC設(shè)計(jì)中需要注意的事項(xiàng)

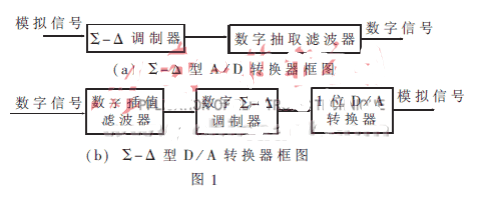

Σ-Δ型ADC和DAC的特點(diǎn)和使用注意事項(xiàng)

使用威格士葉片泵時(shí)需要注意什么

AVR單片機(jī)ADC采樣編程需要注意的問(wèn)題

ADC和DAC使用中要注意的要點(diǎn)

ADC和DAC使用中要注意的要點(diǎn)

評(píng)論