250億美元相當于1338萬臺512GB版本的iPhone XS MAX,相當于蘋果公司市值的1/30,也相當于北京市2017年全年GDP總額的1/16。

250億美元,同時也是2018年6月臺積電宣布投資5nm芯片工藝研發與生產的費用。

在行業不斷喊出“摩爾定律已死!”的當下,依舊有人在不斷埋頭推進芯片工藝,以超人的先進技術挑戰那些難如登天的任務。在7nm芯片量產的當下,5nm的芯片制造工廠、***、刻蝕機、EDA工具、市場與客戶等都已一一就位,2019年,將會是一場5nm的沖刺賽。

▲2018年1月,臺積電***南科5nm晶圓18廠第一期動工儀式

摩爾定律最后玩家!三巨頭的愛恨情仇

摩爾定律的定義為:“當價格不變時,集成電路上可容納的元器件的數量約每隔18-24個月便會增加一倍,性能也將提升一倍。”

也就是說,在一年半到兩年的時間里,你用同樣價錢能夠買到的電腦/手機/其他電子產品性能理論上可以增加一倍。

這簡直太爽了,試問哪個行業的創(賺)新(錢)速度能夠跟它媲美?

于是,就是這么兩行簡單的描述,在過去50年時間里推動著全美國——甚至全世界——的經濟高速發展,直接催生了二戰后結束后美國科技產業的全面爆發,至今仍舊引領全球。如今全球科技殿堂“美國硅谷”中的“硅”字,就是源自于集成電路的主要原材料——硅。

一塊面積不變的芯片上,如果需要容納比以前多一倍的元器件數量,那么就需要這些元器件(一般是晶體管)體積更小,同時排布得更“緊”——我們常說的10nm、7nm芯片制程就是用來描述晶體管柵極寬度大小的。納米進程數字越小,芯片能容納的晶體管數量就越多、性能就越強大。

跟牛頓第二定律這種基本物理學定律不同,摩爾定律并不是一個真正的科學定理,它只是描述了芯片技術高速發展的現狀。芯片的性能不會自動增長,真正推動摩爾定律往前發展的是那些不斷砸錢、招人、實驗、研發的芯片企業們。

不過,市場與經濟同樣有周期,摩爾定律也不例外。隨著芯片工藝越來越逼近硅的物理極限,摩爾定律在最近這幾年來發展速度不斷變慢,每一代芯片工藝的研發成本也像滾雪球一樣瘋狂飆升——比如臺積電宣布砸250億美元研發5nm工藝——隨著技術紅利不斷消失,往牌桌上砸錢的玩家也越來越少。

2018年8月28日,全球第二大芯片代工廠格羅方德宣布,它將無限期地暫停7nm芯片工藝的開發,以便將資源轉移到14nm和12nm工藝上。

同樣在2018年8月,全球第三大芯片代工廠聯電宣布,不再投資12nm以下的先進芯片制程。

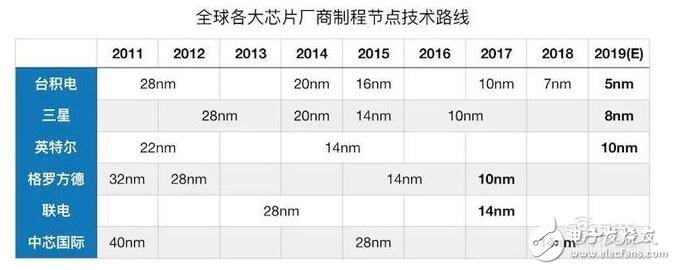

于是,從智能手機到個人電腦、從云計算到比特幣挖礦,全球無數個依靠摩爾定律紅利進行不斷研發創新的企業猛一抬頭,忽然現在市面上還在哼哧哼哧埋頭推動摩爾定律的人,就只剩臺積電、英特爾、三星這三個“老冤家”了。

他們一個是全球第一大芯片代工廠(臺積電),另外兩個則是全球芯片IDM廠商的老大和老二(英特爾和三星)。

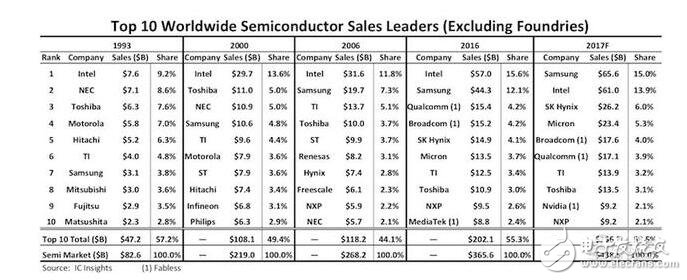

三星的半導體業務由來已久,早在1993年,三星就已經成功躋身全球第七大半導體廠商之位,在此后的二十多年里一路穩中有進,從未跌出過全球前十。去年10月,三星電子宣布通過了8nm LPP工藝驗證,但一直到2018年11月才在自家年度旗艦手機芯片Exynos 9820手上用上8nm技術,預計2019年初量產。

▲IC Insights機構發布的1993-2017F全球半導體十大廠商變遷圖,20多年里英特爾始終穩坐第一

至于老牌芯片巨頭英特爾則更是在先進芯片工藝上投入重大,早年間英特爾在半導體領域幾乎一騎絕塵,連臺積電都要仰仗英特爾的給予代工認證(1988年)。而從1999年的180nm工藝開始,英特爾以每兩年更新一代的節奏研發先進制造工藝,在過去20多年里坐穩了全球第一大半導體廠商的龍頭寶座。直到2017年,三星憑借內存價格暴漲才超越英特爾,翻身躍居第一。

英特爾的工藝研發進程在近年來受到了不小的挑戰,在2015年7月,英特爾宣布本該在2016年面世的10nm工藝推遲量產,此后英特爾雖然也在不斷優化14nm技術,部分10nm芯片也開始小批量出貨,但其10nm至今尚未正式宣布量產。

不過話說回來,早期的nm制程=柵極寬度大小,但是后期延伸出了更多讓晶體管緊湊的方法,因此nm制程與柵極寬度大小并不一一對應,取決于各家定義:比如英特爾14nm的柵極寬度為42nm,同期三星14nm的柵極寬度為48nm,而臺積電16nm的柵極寬度為45nm。在1um^2的面積上,英特爾14nm晶體管可以擺上101個,三星14nm晶體管只能擺75個,臺積電的16nm晶體管能擺上81個。

但無論怎么算,目前臺積電在先進工藝上處于大幅領先的位置,其7nm芯片已經量產并陸續接下蘋果A12、華為麒麟980、高通驍龍855、比特大陸、嘉楠耘智訂單。臺積電也常年稱霸芯片代工領域老大地位,目前市占率超過56%(第二名為9%)。

去年,臺積電已經吹響了5nm工藝制程的沖鋒號角。2018年1月,臺積電在***開設了新的5nm晶圓18廠。同年6月的半導體技術論壇上,臺積電宣布投資250億美元研發、生產5nm工藝。

而在年底的臺積電年度“供應鏈管理論壇”上,臺積電總裁魏哲家表示,該5nm晶圓廠目前已經在設備裝機中,預計2019年Q1完工,2019年Q2將進行5nm芯片制程的風險試產,2020年投入量產。

EUV極紫外***——5nm就靠你了

其實,除了臺積電之外整個芯片制造行業在推進10nm以下技術的研發都多少遇到了些問題,但這個“鍋”并不完全要他們自己背,上游設備商也要背一部分。

芯片制造的環節非常復雜,首先要對硅進行冶煉提純切割等,得到一塊大的硅晶圓。

▲硅晶圓

緊接著,晶圓要經過濕洗(去除雜質)、光刻(雕刻出芯片圖案)、離子注入(形成場效應管)、刻蝕(吹走/洗走多余的材料)、沖洗、退火、氧化、氣相淀積等眾多環節,最后通過測試才送去切割成無數小片片,經過封裝后變成我們熟悉的芯片。

如果再進一步簡化,就可以看作是:用***往硅片上雕刻出特定圖案,用刻蝕機吹走/洗走多余的材料,最后經過一系列處理成為芯片。

以上每一個環節都會涉及到專用的制造設備。由于芯片工藝制程的進一步發展,這些芯片圖案的線條也越來越細,對于設備的要求也越來越高——首當其沖的,自然是負責“雕刻”的***了。

▲光刻原理簡示

***的運作原理是:先把設計好的芯片圖案印在掩膜上,接著用激光光束穿過印著圖案的掩膜和光學鏡片,將芯片圖案曝光在帶有光刻膠涂層的硅片上,此時涂層被光照到的地方發生反應溶解,沒有被照到的地方保持不變,掩膜上的圖案就被轉移到芯片光刻膠涂層上。

▲刻蝕原理簡示

刻蝕相對光刻要容易。刻蝕機通過干刻蝕(用等離子體進行薄膜刻蝕)及濕蝕刻(液體腐蝕)的方法,根據印上去的圖案刻蝕掉有圖案(或者沒有圖案)的部分,留下剩余的部分,芯片圖案又從光刻膠涂層轉移到了硅片上。

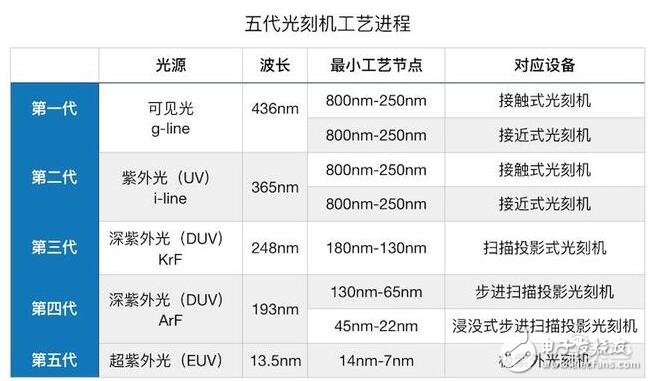

目前市面上高端芯片使用的普遍是第四代DUV深紫外***,它的激光波長是193nm(波長越小,“刻刀”越精密),它的理論“雕刻”極限大約是130nm。

然而到了2005年,***廠商還是沒能成功量產下一代波長更短、“刻刀”更精密的第五代EUV超紫外***,逼得近年來各大芯片制造廠不斷發明創新,用上了多重曝光、步進式掃描、浸潤式光刻等更多新技術,繼續維持摩爾定律從90nm到如今的14nm、10nm發展。而浸潤式光刻技術的開創者林本堅博士也獲得了2018年未來科學大獎-數學與計算機科學獎。

用193nm的DUV深紫外***造7nm芯片,就像用一支直徑是193nm的筆去寫7nm的字一樣,其難度不亞于拉著駱駝穿過針眼,半導體技術發展到最后竟然有點哲學的意思。

而且,由于頻繁用上了浸潤式光刻、三重曝光等復雜技術,用193nm DUV***打造7nm芯片的成本已然超過了EUV ,生產交期更長、技術更為復雜,因此7nm之后,行業對于第五代EUV超紫外***的呼聲越來越強烈。

EUV超紫外***的激光波長只有13.5nm,是一把非常精細的“雕刻刀”。這一技術源自于美國雷根時代的“星戰計劃”。EUV超紫外***本應在2005年就量產上陣,然而由于這一技術的研發難度巨大,EUV設備不僅所需的光源功率遲遲無法達到250W工作功率需求,而且對于光學透鏡、反射鏡系統的精密度高到變態。

比如EUV***的關鍵部件反射鏡,其瑕疵大小只能以pm(nm的千分之一)計。如果反射鏡面積有整個德國大,最高的突起處不能高于一厘米。

▲荷蘭***巨頭ASML總裁暨CEO溫彼得(Peter Wennink)

“如果我們交不出EUV超紫外***的話,摩爾定律就會從此停止。”荷蘭***巨頭ASML總裁暨CEO溫彼得(Peter Wennink)曾經這樣說。

因此,雖然英特爾、臺積電、三星這三大個老冤家彼此搶訂單、搶人才的競爭不斷,但是在2012年的時候,他們三個曾經聯袂向荷蘭ASML***廠投資41億、14億、9.75 億美元,督促ASML加快研發新一代EUV超紫外***,可見***的重要性。

雖然荷蘭ASML的EUV***跳票了十多年(并且業內老二、老三尼康與佳能紛紛放棄研發,這個節奏是不是很眼熟?),但到了2016年,ASML終于將EUV***造了出來并成功量產。

2017年,ASML出貨了11臺EUV***,2018年出貨了18臺。雖然這些EUV***基本上被臺積電、三星這些廠商優先買去了,但中芯國際也出資1億多美金購買了一臺7nm工藝EUV***,預計2019年上半年到貨。

ASML表示,由于EUV超紫外***的零組件多達5萬多個部件,從客戶下單到正式交貨,交期約21個月。

目前臺積電已經量產的華為、蘋果、比特大陸等7nm芯片都還是基于193nm的DUV深紫外***的,但是DUV技術已經逼近極限,再往下走的話成本飆升,5nm芯片的技術路徑必須轉到EUV。

2018年10月,臺積電宣布基于EUV技術的7nm芯片已經流片成功,和7nm DUV相比,7nm EUV可以提高芯片密度20%,功耗降低6%至12%。臺積電的5nm有望大面積用上EUV。

金貴的5nm和不差錢的臺積電

在先進工藝上的不斷砸錢研發也給予了臺積電豐厚的產業回報,常年稱霸芯片代工領域老大地位的臺積電,這兩年靠著蘋果、高通、華為等的訂單賺得盆滿缽滿,其2018年前三季度合并營收達新臺幣7417.03億元,較2017年同期增長6.0%,8月初的病毒事件都未曾大面積影響其財報。

上文提到,臺積電在2018年1月就開始興建5nm晶圓廠了;除了錢、晶圓廠、***之外,5nm的刻蝕機、EDA工具、客戶等也已經陸續就位:

1)5nm刻蝕機已就位;

芯片的制造過程可以簡化成用***“雕刻”圖案,用刻蝕機吹走/洗走多余的材料。相對于***,刻蝕機的研發難度要小一些,但刻蝕機也是除***以外最關鍵的設備。目前一臺刻蝕機單價在200萬美元左右,一個晶圓廠需要40-50臺刻蝕機。

國外刻蝕機設備廠商主要有應用材料(Applied Materials)、科林研發(LAM) 、東京威力科創(TEL)、日立先端(Hitach)、牛津儀器等;國內玩家則有中微半導體、北方微電子、金盛微納科技,我們跟國外的差距沒有***那么大。

2018年12月,中微半導體的5nm等離子體刻蝕機也宣布通過臺積電驗證,將用于全球首條5nm制程生產線。而在7nm時代,中微半導體的刻蝕機也進入了臺積電的7nm產線。

2)5nm EDA工具已就位;

目前,全球幾大EDA巨頭都已經陸續推出了5nm芯片設計工具,比如在2018年10月,新思科技宣布其數字和定制設計平臺通過了臺積電的5nm EUV工藝技術認證。

而另一EDA巨頭華登國際創始人兼Cadence CEO陳立武曾經告訴智東西,目前Cadence已經和很多合作伙伴開始了7nm、5nm、甚至3nm芯片工藝制程的研究。比如今年年初,比利時公司Imec與Cadence就成功流片了首款3nm測試芯片。

陳立武說,現在5nm市場是最活躍的,有很多非常積極的公司正在安排5nm相關EDA軟件與設計、IP的協同。

3)5nm客戶已就位;

有工藝,自然也需要有市場。臺積電曾表示,目前很多客戶已經開始基于新工藝開發芯片了。

不過由于芯片設計的復雜度不同,像比特大陸這種專用芯片設計起來相對容易、手機芯片次之、電腦芯片與數據中心在再次之,所以最先用上先進的工藝的往往是專用芯片而非通用芯片,比如臺積電7nm的頭批客戶只包含了比特幣與手機芯片玩家。

而根據華為海思平臺與關鍵技術開發部部長夏禹此前給出的芯片工藝路線路,華為的規劃是推出7nm芯片之后將推進5nm芯片研發進程,預計5nm芯片問世的時間點在2020年。

華為研發人員曾經告訴智東西,在7nm時代,華為和臺積電合作研發了3年,耗資3億美元,才終于在2018年拿出7nm芯片設計。

工藝越先進,需要投入的也成本越高,這個道理在芯片代工廠跟芯片設計商同理,5nm的設計總成本(人工與許可費)是7nm的1.5倍左右。

而根據臺積電數據,基于5nm工藝生產的A72芯片,芯片面積縮小了1.8倍,速度提升了14.7% -17.1%。

結語:三大巨頭的工藝競爭還將繼續

隨著研發成本越來越高,高精尖納米制程成了越來越少部分玩家的戰場,不僅芯片先進制造工藝的研發成本高、芯片設計的成本也跟著水漲船高。

在PC和手機的出貨量開始走下坡路的當下,不少機構對于今年全球半導體市場的走勢持悲觀態度。不過,AI、5G、數據中心這些高端芯片需求正處在持續上升之勢,雖然目前臺積電暫時領先,但是英特爾、三星、臺積電三大巨頭的競爭還將持續,市場對于先進工藝的熱情依舊持續。

與此同時,三星和臺積電都已經公布了3nm的線路圖。如果說5nm是一個難關的話,受到量子隧穿效應影響的3nm就更是一個逼近物理極限的重要挑戰。摩爾定律尚未完結,只是門檻越來越高了。

-

臺積電

+關注

關注

44文章

5685瀏覽量

166996 -

晶圓

+關注

關注

52文章

4973瀏覽量

128313

發布評論請先 登錄

相關推薦

臺積電猛砸250億進攻5nm!

臺積電猛砸250億進攻5nm!

評論