1

機(jī)器學(xué)習(xí)無處不在,賽靈思已成主流方案

通過收購DeePhi (深鑒科技),賽靈思專注于深度壓縮技術(shù),為業(yè)界提供了領(lǐng)先的機(jī)器學(xué)習(xí)功能。現(xiàn)在,賽靈思所提供的高層次工具,可以將ML框架訓(xùn)練的網(wǎng)絡(luò)直接編譯為優(yōu)化的FPGA或SoC實現(xiàn)。

面向Zynq?-7000 SoC和Zynq UltraScale +?MPSoC,深度神經(jīng)網(wǎng)絡(luò)開發(fā)套件(DNNDK)被設(shè)計為一個集成框架,旨在簡化和加速深度學(xué)習(xí)應(yīng)用在DeePhi深度學(xué)習(xí)處理單元(DPU)上的開發(fā)和部署平臺。如果您想提高深度學(xué)習(xí)性能,現(xiàn)在即可下載并試用常見的開發(fā)套件,如ZCU102、ZCU104和Ultra96!你很快就會意識到,這是一個比圣誕老人更好的開源專題工作坊。

面向Alveo?加速器卡和云提供商,Xilinx ML Suite支持許多機(jī)器學(xué)習(xí)框架,如Caffe,MxNet和Tensorflow,以及Python和RESTful API。Xilinx ML Suite使開發(fā)人員能夠優(yōu)化和部署加速機(jī)器學(xué)習(xí)推斷,尤其是低延遲推斷。賽靈思提供了多種入門方式:AWS Market Place,Nimbix或Alveo加速卡。如果您想試用Xilinx ML Suite,請參閱Amazon EC2 F1 FPGA實例上的點(diǎn)播教程。

2

Zynq UltraScale + RFSoC - 聽似不太可能的搭配卻證明是成功的

Zynq?UltraScale+?RFSoC將模擬、數(shù)字和嵌入式軟件設(shè)計集成到單個單片器件上,以提高系統(tǒng)穩(wěn)定性,并提供更高級別的靈活性和適應(yīng)性。Zynq UltraScale + RFSoC將RF數(shù)據(jù)轉(zhuǎn)換器和SD-FEC內(nèi)核集成到一個器件中。所有Zynq UltraScale + RFSoC都已量產(chǎn)。此外,Xilinx及其合作伙伴還提供了ZCU111評估套件、ZCU1275特性套件和RF數(shù)據(jù)轉(zhuǎn)換器評估工具,可用于快速開發(fā)和評估。

如果您錯過了它們,請參閱2018年的Adaptable Advantage博客中的幾篇文章。

1. 首創(chuàng):采用FPGA邏輯的多千兆位ADC / DAC采樣套件

2. Xilinx推出業(yè)界首款可配置集成SD-FEC

3. RF級模擬設(shè)計必須現(xiàn)已推出

3

保留還是不保留?具有PAM4功能的Virtex UltraScale + FPGA為您提供解決方案

隨著新光學(xué)和標(biāo)準(zhǔn)的變化,該行業(yè)正在加速發(fā)展。 58G PAM4將成為下一代的互連標(biāo)準(zhǔn)。支持PAM4的Virtex?UltraScale+ FPGA不僅可以實現(xiàn)下一代光學(xué)和可擴(kuò)展性,還可以在保留現(xiàn)有傳統(tǒng)25G背板的同時實現(xiàn)雙倍性能。在2018年的各種展會上,賽靈思展示了我們的58G PAM4解決方案以及業(yè)界首款112G PAM4演示。

以下是我們今年展示的幾個視頻,體現(xiàn)了賽靈思的技術(shù)領(lǐng)先地位。

58G PAM4收發(fā)器的性能

Xilinx推出具有PAM4功能的Virtex UltraScale + FPGA

Xilinx展示Virtex UltraScale + GTM收發(fā)器在XDF硅谷2018推動58G PAM4

Virtex UltraScale + 58G PAM4 FPGA和16nm 112G測試芯片

4

Alveo - 世界上最快的數(shù)據(jù)中心和AI加速卡

在2018年10月在XDF上,賽靈思推出Alveo? 數(shù)據(jù)中心加速卡,與高端CPU相比,可提供高達(dá)20倍的實時 推斷性能,與高端GPU相比,可提供高達(dá)4倍的實時推斷性能。XDF上, 賽靈思還發(fā)布了AMD EPYC和Xilinx Alveo加速卡,創(chuàng)造了每秒生成30,000張圖像的服務(wù)器吞吐量的世界紀(jì)錄。

Alveo加速器卡使開發(fā)人員能夠調(diào)整和優(yōu)化他們的算法,以改變加速工作負(fù)載,所有這些都使用相同的硬件。對于那些需要最高性能且又能適應(yīng)加速任何工作負(fù)載的應(yīng)用,馬上著手開始試用Alveo加速器卡吧。

5

Versal ACAP:支持所有應(yīng)用和所有開發(fā)者的異構(gòu)計算時代

賽靈思2018年的第一大產(chǎn)品新聞是Versal? ACAP!在XDF 2018展會上,Xilinx推出了Versal產(chǎn)品系列-業(yè)界首款自適應(yīng)計算加速平臺(ACAP)。Versal產(chǎn)品是第一個將軟件可編程性與特定領(lǐng)域的硬件適應(yīng)性相結(jié)合的平臺。Versal ACAP不是一個固定的引擎,而是利用CPU,GPU和FPGA的優(yōu)勢來加速任何應(yīng)用。最重要的是,平臺的硬件和軟件可以由具有任何背景(硬件或軟件)的開發(fā)人員進(jìn)行編程,優(yōu)化和部署。你在等什么?查看我們的白皮書,數(shù)據(jù)表概述,AI Engine blog,以及一個視頻, 這些可以幫助你快速入門。最后, 別忘了趕緊注冊個人信息以便及時獲得最新技術(shù)新聞哦!

2018年,從FPGA到加速器卡到新型的器件類別的各種技術(shù)創(chuàng)新上, 賽靈思都取得了重大進(jìn)展。我們期待著借助這些前沿的技術(shù),支持所有的開發(fā)者, 加速所有的創(chuàng)新應(yīng)用, 攜手客戶和合作伙伴創(chuàng)造新的輝煌。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8742瀏覽量

148031 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122120 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8438瀏覽量

133078

原文標(biāo)題:繼往開來,迎接2019!—— Xilinx 2018五大產(chǎn)品新聞回顧

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

三星CES 2025大放異彩 全面展示無處不在的AI魅力

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

易靈思FPGA產(chǎn)品的主要特點(diǎn)

萬物智聯(lián)時代,OpenHarmony何以「無處不在」?

直播回顧解答 | 思瑞浦TPS325產(chǎn)品系列:專注多合一智能門鎖,HMI TFT顯示+電容觸控方案

人工智能技術(shù)躍進(jìn):英特爾引領(lǐng)AI無處不在新紀(jì)元

賽思快訊 | 發(fā)展新質(zhì)生產(chǎn)力問道賽思?賽思如何下好“創(chuàng)新棋”?

無處不在的鎧俠存儲

深圳特信電子|4G5G手機(jī)信號放大器:告別信號盲區(qū),信號無處不在

是德科技Keysight World Tech Day B5G/6G助力連接無處不在分論壇

Xilinx ZYNQ 動手實操演練

給我一個FPGA,可以撬起所有顯示的接口和面板

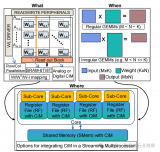

機(jī)器學(xué)習(xí)(ML)推理主要計算之存內(nèi)計算芯片

Xilinx 2018五大產(chǎn)品新聞回顧:機(jī)器學(xué)習(xí)無處不在,賽靈思已成主流方案

Xilinx 2018五大產(chǎn)品新聞回顧:機(jī)器學(xué)習(xí)無處不在,賽靈思已成主流方案

評論