在一個環境中實施從合成到塑封式布局和布線以及比特流生成的全套 FPGA 設計。界面中內置了用于運行布局和布線的常用選項,并在與合成結果相同的位置提供所有報告。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605984 -

設計

+關注

關注

4文章

818瀏覽量

69951

發布評論請先 登錄

相關推薦

一文講清芯片封裝中的塑封材料:環氧塑封料(EMC)成分與作用

在半導體封裝領域,塑封技術以其低成本、高效率、良好的保護性能,成為封裝工藝中的關鍵一環。Mold工藝,作為塑封技術的重要組成部分,通過特定的模具將芯片等組件包裹在加熱的模塑材料中,固化后形成堅硬

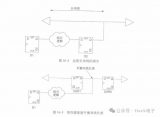

Vivado之實現布局布線流程介紹

一、前言 本文將介紹Vivado進行綜合,以及布局布線的內部流程,熟悉該流程后結合Settings中對應的配置選項,對于時序收斂調試將更具有針對性。 二、Implementation(實現) 實現

塑封、切筋打彎及封裝散熱工藝設計

本文介紹塑封及切筋打彎工藝設計重點,除此之外,封裝散熱設計是確保功率器件穩定運行和延長使用壽命的重要環節。通過優化散熱通道、選擇合適的材料和結構以及精確測量熱阻等步驟,可以設計出具有優異散熱

塑封器件絕緣失效分析

塑封器件絕緣失效機理探究與改進策略塑封器件因其緊湊、輕便、經濟及卓越的電學特性,在電子元件封裝行業中占據著重要地位。但隨著其在更嚴苛環境下的應用需求增加,傳統工業級塑封材料和技術的局限性逐漸顯現。金

高速ADC PCB布局布線技巧分享

在高速模擬信號鏈設計中,印刷電路板(PCB)布局布線需??要考慮許多選項,有些選項比其它選項更重要,有些選項??則取決于應用。最終的答案各不相同,但在所有情況下,??設計工程師都應盡量消除最佳做法

FPGA的高速接口應用注意事項

、LVDS高速接口等,FPGA需要實現相應的關鍵技術以支持數據傳輸。

布線與布局 :

時鐘信號布線:FPGA和高速DAC的時鐘信號必須保證

發表于 05-27 16:02

FPGA布局布線優化策略(五)

對設計者很通常的情況是花費幾天或幾周的時間圍繞一個設計來滿足時序,甚至多半利用上面描述的自動種子變化,只面對可以起伏通過已有布局的小改變和時序特性完全改變。

發表于 04-01 12:35

?840次閱讀

FPGA布局布線優化技術

寄存器排序是布局工具把多位寄存器的相鄰位分組放進單個邏輯元件所利用的方法。大多數基于單元的邏輯元件有不止一個觸發器,因此,相鄰位放置在一起,時序可以被優化。

發表于 03-29 11:30

?434次閱讀

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

隨著電子技術的進步.FPGA邏輯電路能完成的功能越來越多,同樣也帶來了一個很大的問題,即邏輯電路的規模越來越大,這意味著RTL代碼到FPGA的映射、布局布線所花費的時間也越來越長。

FPGA設計的塑封式布局和布線介紹

FPGA設計的塑封式布局和布線介紹

評論