隨著制程的進一步縮小,芯片制造的難度確實已經快接近理論極限了。

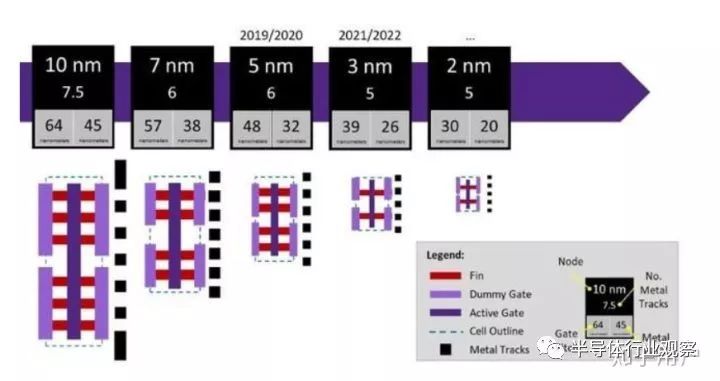

首先簡單介紹一下當前芯片先進制程的發展現狀,下圖是近些年芯片制程的發展圖,Intel 曾一度處于業內領頭羊地位,引領半導體先進制程的發展,但是從14nm 到10nm 制程時遇到了很多麻煩,一度處于難產狀態。Intel在10nm 量產后又遲遲難以進一步推進,目前7nm 量產還沒有一個確定的日期, 雖然Intel 的10nm工藝有著比競爭對手更高的晶體管密度。

半導體制程發展

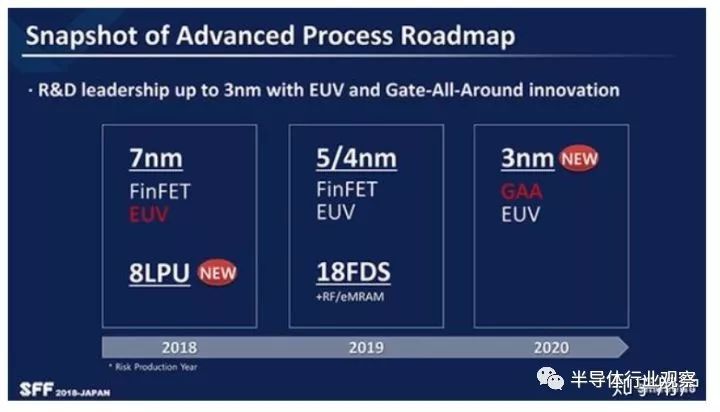

我們再來看看競爭對手,目前擁有最先進制程的廠商無疑非臺積電 (tsmc)莫屬,臺積電在2018年最早實現了7nm 制程的突破并量產, 而5nm 制程工藝也已指日可待,預計在2020年實現量產。

臺積電制程規劃

緊隨其后的是三星,在臺積電之后也成功實現了7nm 制程的量產,所不同的是,三星提前使用了EUV光刻技術來進行7nm 工藝,而臺積電則把EUV留到了5nm 以后的制程。但是,相對而言,三星的7nm 工藝不如臺積電的7nm 工藝,臺積電也因此在7nm 制程工藝上斬獲了大量的訂單。

三星制程規劃

而曾今從AMD分離的半導體大廠格羅方德則干脆直接放棄了7nm工藝的研發,表示玩不起了。

另外就算有再強的研發實力和經濟實力,也不表示這個游戲可以一直玩下去,詳細內容可以參考以下話題,目前的制程工藝已經在逼近理論極限。

我們再回到這個問題本身上來,半導體制造的難度最主要是制程的實現,半導體廠商之間的競爭也體現在先進制程的突破上。以下將從制程和其他幾個方面作簡單介紹:

先進制程

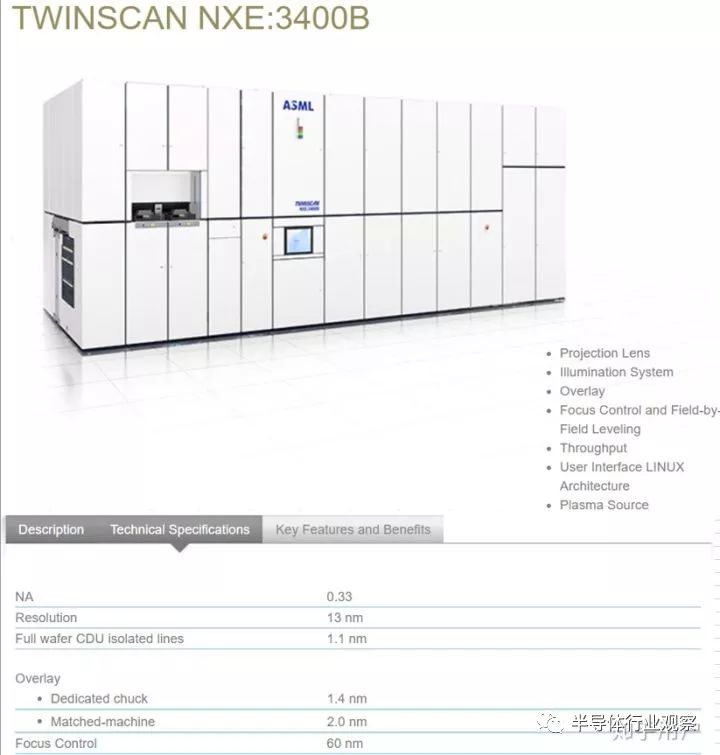

半導體工藝制程的實現需要很多的工藝相互配合,主要的有光刻工藝,蝕刻工藝,金屬工藝,化學氣相沉積工藝,離子注入工藝等。由于芯片的制造過程中所有的圖形都是有光刻工藝決定的,而其他工藝只是在光刻工藝制作出的模板上進一步加工,因此直接決定制程的就是光刻工藝。光刻工藝的精度又是由***的光學分辨率決定:

ASML設備發展

頂尖***鄰域荷蘭ASML公司一家獨大,每一次制程的進步和新型***的推出都是密不可分的。最新的7nm 制程工藝的量產就得益于 ASML EUV ***的成功研制,實際上由于大功率EUV光源實現困難,EUV***只到2018年才正式進入量產, 而不是上圖計劃中的2010年左右。

ASML EUV

***除了對分辨率的要求以外,對于對準(Overlay)有更高的要求,比如上圖中最新的EUV ***對準的誤差是1.4nm, 并且達到這一水平還需要在高速狀態下實現,有一個說法是:

“相當于兩架大飛機從起飛到降落,始終齊頭并進。一架飛機上伸出一把刀,在另一架飛機的米粒上刻字,不能刻壞了。”

實際上這個說法并不夸張,只有在這種精度級別上才能實現目前所需的制程。

當然,光刻工藝精度的提高,對其他蝕刻等工藝也會提出更高的要求,只有所有的工藝都能夠完美的配合時,才能實現新一代制程的導入。

工藝流程

半導體工藝類型只有我上面提到的不到10個(光刻,蝕刻,化學氣相沉積等),但是實際上由于芯片的制備是一層一層的加工制造,并且制程越先進,晶體管密度越大,相應的所需要的層數也越多,因此需要各種類型的工藝反復的進行加工。芯片從晶圓開始加工到結束可能需要300道以上的工序,而任何一道工序稍有失誤就可能導致大量的芯片報廢。并且很多工藝都是沒有挽救余地的,中間只要有一個工藝發生偏差就只能報廢處理,還有很多時候很小的偏差只有等到芯片制造完成進行電性能測試的時候才能發現,這樣造成的損失就更加龐大。

芯片剖面圖

因此在整個工藝流程中,設備的狀態,工藝參數,材料的供應,環境因素等等都可能導致嚴重的后果,例如臺積電最近的兩次事故,對于臺積電這種具有豐富經驗的先進制程半導體廠商都難以預防,那些新建立的芯片制造廠商可能交學費都要交到破產了。

生產運營

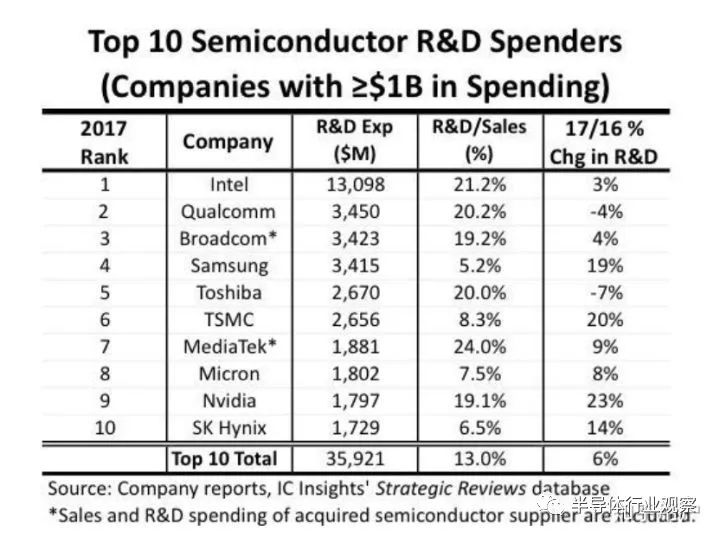

建立一條先進制程芯片產線需要大量的資金投入,而維持一條先進制程產線本身也需要大量的資金投入,因此需要保證產線盡可能滿負荷運營才能實現有競爭力的盈利。所以需要保證有充足的訂單,要想拿到訂單又需要有領先的制程技術,領先的制程技術又需要大量的研發經費, 很多半導體廠商玩不起就玩不下去了。

生產運營包含提高良品率,提高生產效率,節約成本,事故預防等等,所以芯片制造不只是制造出來就可以,還需要以盡可能低的成本制造出來。

-

芯片制造

+關注

關注

10文章

629瀏覽量

28913

原文標題:你真的知道芯片制造有多難么?

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創新聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

24位或者說高分辨率的AD到底有什么用呢?

差分輸入和和單端輸入在本質上到底有什么區別?

lm2902做的二階低通濾波器,無論怎么調試C1的值,電路的波特圖都保持不變,請問一下C1的作用到底有多大?

無人機智能巡檢系統到底有哪些作用

EWSTM8-2201 or 3101安裝說明上有的說選“是”,有的說選“否”,二者到底有什么區別?對工程有什么影響?

IPv6到底有什么用,給我們生活帶來哪些變化?

精密醫療器械激光切割機在醫療行業到底有多重要

帶你領悟芯片制造到底有多難

帶你領悟芯片制造到底有多難

評論