EDA是電子設(shè)計自動化的縮寫,在20世紀(jì)60年代中期從計算機輔助設(shè)計(CAD)、計算機輔助制造(CAM)、計算機輔助測試(CAT)和計算機輔助工程(CAE)的概念發(fā)展而來的。

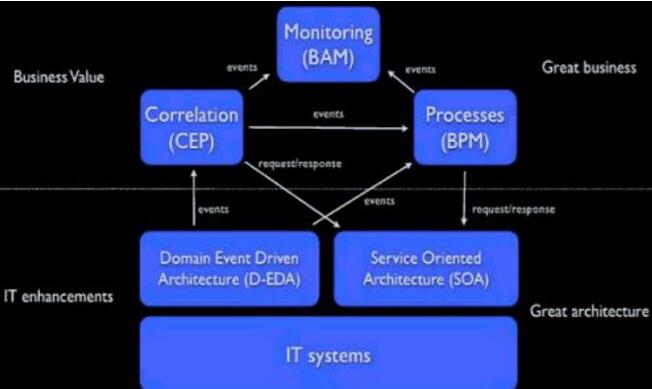

EDA技術(shù)就是以計算機為工具,設(shè)計者在EDA軟件平臺上,用硬件描述語言VerilogHDL完成設(shè)計文件,然后由計算機自動地完成邏輯編譯、化簡、分割、綜合、優(yōu)化、布局、布線和仿真,直至對于特定目標(biāo)芯片的適配編譯、邏輯映射和編程下載等工作。EDA技術(shù)的出現(xiàn),極大地提高了電路設(shè)計的效率和可操作性,減輕了設(shè)計者的勞動強度。

EDA工具軟件可大致可分為芯片設(shè)計輔助軟件、可編程芯片輔助設(shè)計軟件、系統(tǒng)設(shè)計輔助軟件等三類。

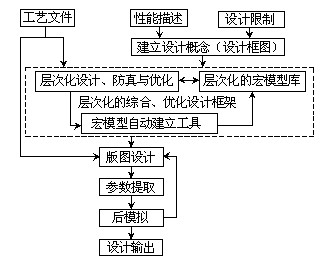

設(shè)計流程:

(1) 前端設(shè)計(系統(tǒng)建模RTL 級描述)后端設(shè)計(FPGAASIC)系統(tǒng)建模

(2)IP復(fù)用

(3) 后端設(shè)計

(4) 系統(tǒng)描述:建立系統(tǒng)的數(shù)學(xué)模型

(5) 功能描述:描述系統(tǒng)的行為或各子模塊之間的數(shù)據(jù)流圖

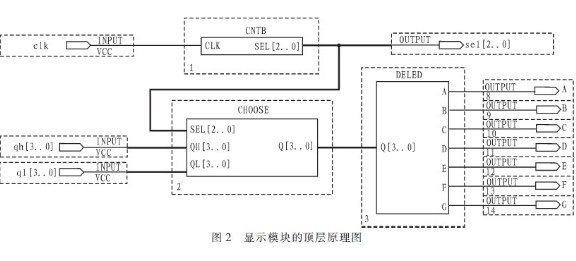

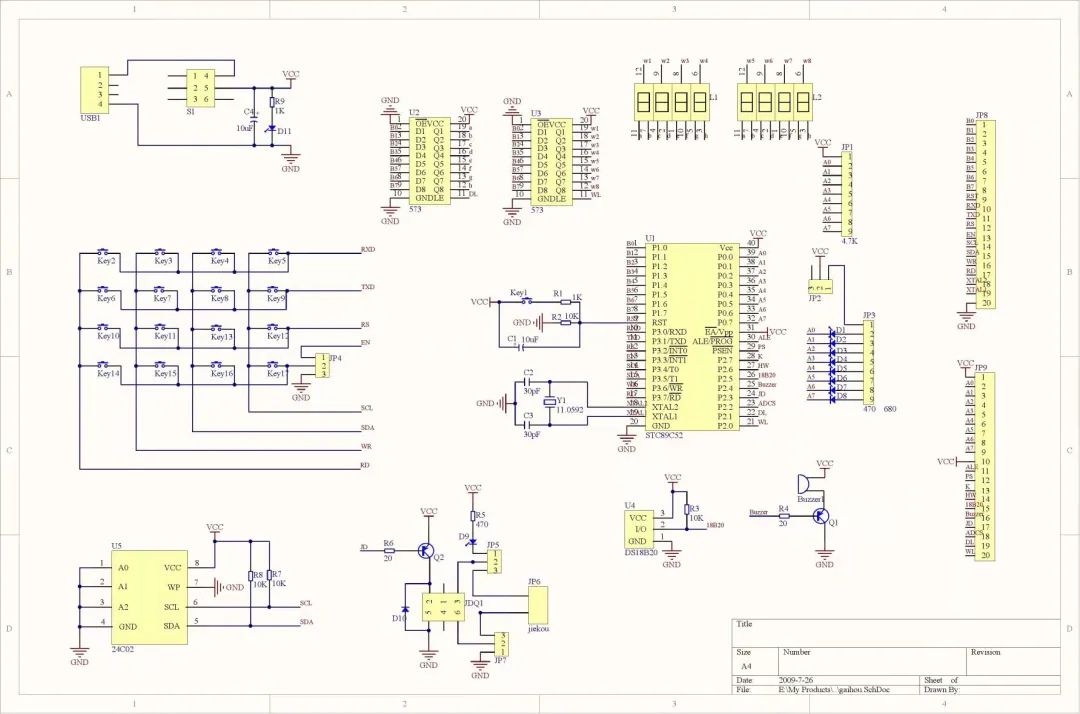

(6)邏輯設(shè)計:將系統(tǒng)功能結(jié)構(gòu)化,通常以文本、原理圖、邏輯圖、布爾表達式來表示設(shè)計結(jié)果

(7) 仿真:包括功能仿真和時序仿真,主要驗證系統(tǒng)功能的正確性及時序特性

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427215 -

計算機

+關(guān)注

關(guān)注

19文章

7536瀏覽量

88638 -

eda

+關(guān)注

關(guān)注

71文章

2787瀏覽量

173854

發(fā)布評論請先 登錄

相關(guān)推薦

基于EDA技術(shù)的電子設(shè)計要點

EDA全流程的重要意義,以及國內(nèi)EDA全流程進展

EDA技術(shù)有什么特征?

EDA技術(shù)基礎(chǔ)知識及數(shù)字系統(tǒng)設(shè)計實例

EDA技術(shù)的概念及范疇分析

EDA技術(shù)的簡單介紹及特點分析

EDA技術(shù)特點與流程介紹

一文知道EDA的設(shè)計流程

eda技術(shù)與vhdl基礎(chǔ) eda的主要功能優(yōu)點 現(xiàn)代EDA技術(shù)的特點有哪些

電子硬件EDA設(shè)計流程

EDA技術(shù)的概念介紹及設(shè)計流程分析

EDA技術(shù)的概念介紹及設(shè)計流程分析

評論