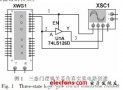

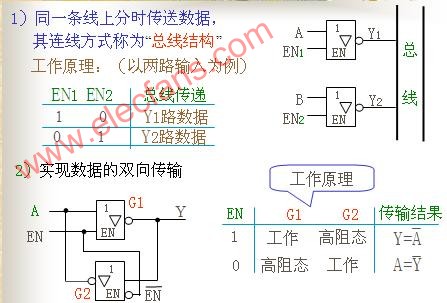

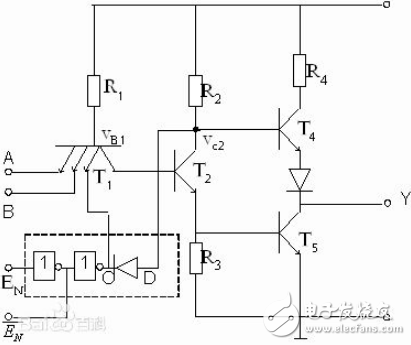

三態電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態。高阻態主要用來將邏輯門同系統的其他部分加以隔離。例如雙向I/O電路和共用總線結構中廣泛應用三態特性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605987 -

總線

+關注

關注

10文章

2903瀏覽量

88387 -

三態門

+關注

關注

1文章

34瀏覽量

18868

發布評論請先 登錄

相關推薦

什么是三態門和OC門?

三態門和OC門一、OC門實際使用中,有時需要兩個或兩個以上與非門的輸出端連接在同一條導線上,將這些與非門上的數據(狀態)用同一條導線輸送出去。因此,需要一種新的與非門電路來實現線與邏輯

發表于 05-26 13:01

【夢翼師兄今日分享】 三態門程序設計講解

等,要求信號為三態類型,也就是我們所說的輸入輸出(inout)類型。那么,本節夢翼師兄將和大家一起來探討三態門的用法。項目需求設計一個三態門電路,可以實現數據的輸出和總線“掛起”。系統

發表于 12-12 16:11

三態門邏輯功能的Multisim仿真方案

介紹了用Multisim仿真軟件分析三態門工作過程的方法,目的是探索三態門工作波形的仿真實驗技術,即用Multisim仿真軟件中的字組產生器產生三態

發表于 05-06 15:59

?0次下載

三態門如何在FPGA中實現與仿真

三態門在數字電路上可以說是應用的非常廣泛,特別是一些總線上的應用,因而,隨著數字電路的發展,就避免不了用硬件描述語言在FPGA上來設計實現三態門

發表于 02-08 11:37

?8376次閱讀

三態門邏輯電路圖大全(三款三態門邏輯電路圖)

三態指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗狀態。本文開始介紹了三態門的定義,其次介紹了三態

發表于 03-01 14:03

?8w次閱讀

FPGA之三態門

FPGA之三態門

評論