uC/OS-II的時間管理是通過定時中斷來實現的,該定時中斷一般為10毫秒或100毫秒發生一次,時間頻率取決于用戶對硬件系統的定時器編程來實現。中斷發生的時間間隔是固定不變的,該中斷也成為一個時鐘節拍。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

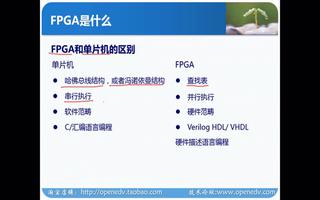

FPGA

+關注

關注

1630文章

21796瀏覽量

605988 -

定時器

+關注

關注

23文章

3255瀏覽量

115367

發布評論請先 登錄

相關推薦

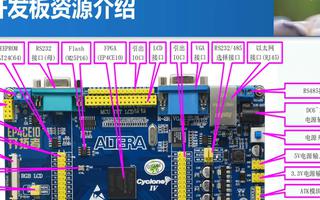

分享正點原子FPGA開發板全套資料

本帖最后由 100dongdong 于 2020-5-16 23:48 編輯

正點原子FPGA開拓者開發板,Intel(Altera) FPG

發表于 05-16 23:35

正點開拓者FPGA開發板使用問題

求問各位大佬,剛剛入門正點開拓者FPGA開發板,用板載pcf8591采集信號發生器單一頻率正弦波,再用ip核做fft,結果和matlab上fft不一樣,請問是怎么回事呢?

發表于 01-04 09:34

正點原子開拓者FPGA視頻:SignalTap II軟件的使用

可以選擇要捕獲的信號、開始捕獲的時間,以及要捕獲多少數據樣本。還可以選擇時間數據從器件的存儲器塊通過JTAG端口傳送至SignalTap II Logic Analyzer,還是至I/O引腳以供外部邏輯分析儀或示波器使用。將實時

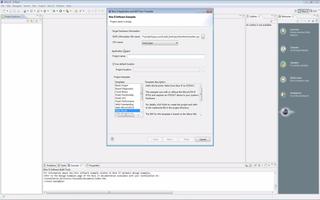

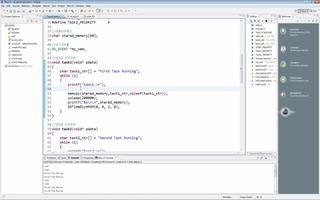

正點原子開拓者FPGA Qsys視頻:創建第一個uCOS II系統

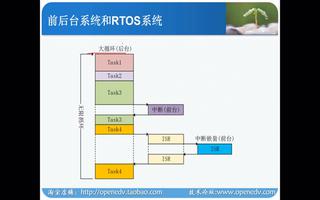

μC/OS-II由Micrium公司提供,是一個可移植、可固化的、可裁剪的、占先式多任務實時內核,它適用于多種微處理器,微控制器和數字處理芯片(已經移植到超過100種以上的微處理器應用中)。同時,該系統源代碼開放、整潔、一致,注釋詳盡,適合系統開發。

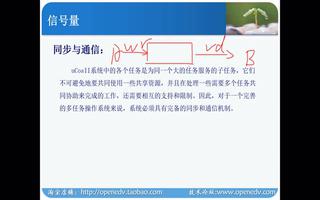

正點原子開拓者FPGA Qsys視頻:uCOS II消息郵箱和消息隊列

uC/OS-II目標是實現一個基于優先級調度的搶占式的實時內核,并在這個內核之上提供最基本的系統服務,如信號量,郵箱,消息隊列,內存管理,中斷管理等。

正點原子開拓者FPGA Qsys視頻:uCOS II任務管理與時間管理

μC/OS-II由Micrium公司提供,是一個可移植、可固化的、可裁剪的、占先式多任務實時內核,它適用于多種微處理器,微控制器和數字處理芯片(已經移植到超過100種以上的微處理器應用中)。同時

正點原子開拓者FPGA Qsys視頻:uCOS II任務管理與時間管理(2)

正點原子開拓者FPGA Qsys視頻:uCOS II任務管理與時間管理(2)

評論