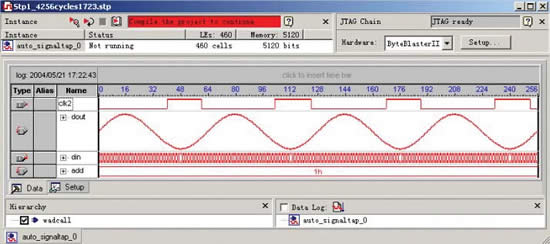

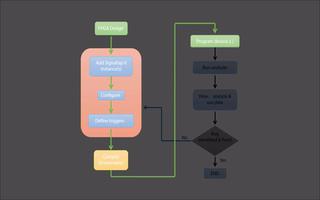

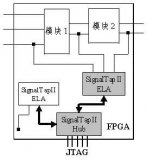

SignalTap II獲取實時數(shù)據(jù)的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以預(yù)先設(shè)定的時鐘采樣實時數(shù)據(jù),并存儲于FPGA片上ram資源中,然后通過JTAG傳送回Quartus II分析。可見SignalTap II,其實也是在工程額外加入了模塊來采集信號,所以使用SignalTap II需要一定的代價,首先是ELA,其次是ram,如果,工程中剩余的ram資源比較充足,則SignalTap II 一次可以采集較多的數(shù)據(jù),相應(yīng)的如果FPGA資源已被工程耗盡則無法使用SignalTap II調(diào)試。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606037 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7145瀏覽量

89584 -

工具

+關(guān)注

關(guān)注

4文章

314瀏覽量

27911

發(fā)布評論請先 登錄

相關(guān)推薦

SignalTap II 采樣時鐘????

SignalTap的使用方法及工具下載

【鋯石A4 FPGA試用體驗】SignalTap II使用

使用SignalTap II邏輯分析儀調(diào)試FPGA

使用SignalTap II邏輯分析儀調(diào)試FPGA

常用手機(jī)焊接工具使用方法

調(diào)試?yán)?b class='flag-5'>SignalTap II的使用_QuartusII的奇幻漂流-Chap.5

鋯石FPGA A4_Nano開發(fā)板視頻:SignalTap II軟件使用講解

FPGA之軟件工具篇:SignalTap II軟件使用講解

正點原子開拓者FPGA視頻:SignalTap II軟件的使用

SignalTap II的特點、設(shè)置流程及邏輯分析儀的設(shè)計

如何輕松掌握SignalTAP II工具的使用方法

如何輕松掌握SignalTAP II工具的使用方法

評論