JK觸發器類似于SR觸發器,但當J和K輸入均為低電平時狀態沒有變化

基本SR NAND觸發器電路在順序邏輯電路中有許多優點和用途,但它有兩個基本的切換問題。

1。必須始終避免設置= 0和復位= 0條件(S = R = 0)

2。如果在使能(EN)輸入為高電平時置位或復位改變狀態,則可能不會發生正確的鎖存動作

然后,為了克服SR觸發器設計的這兩個基本設計問題,JK觸發器

開發。

這個簡單的JK觸發器是所有觸發器設計中使用最廣泛的,被認為是通用觸發器電路。標有“J”和“K”的兩個輸入不是縮寫其他單詞的縮寫字母,例如Set的“S”和復位的“R”,但它們本身是由其發明者Jack Kilby選擇的自主字母來區分翻轉其他類型的翻轉設計。

JK觸發器的順序操作與前一個具有相同“設置”和“復位”輸入的SR觸發器完全相同。這次的不同之處在于,即使 S 和 R 都處于邏輯“1”,“JK觸發器”也沒有SR Latch的無效或禁止輸入狀態。

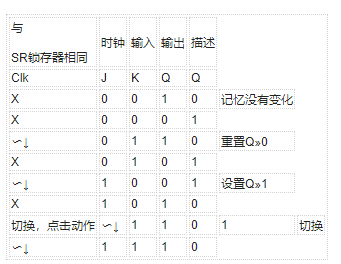

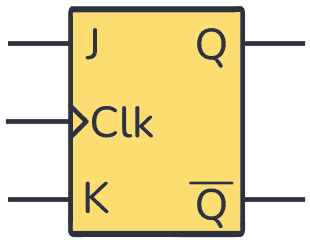

JK觸發器基本上是一個門控SR觸發器,增加了一個時鐘輸入電路,可以防止輸入S和輸入時出現的非法或無效輸出條件R等于邏輯電平“1”。由于這個額外的時鐘輸入,JK觸發器有四種可能的輸入組合,“邏輯1”,“邏輯0”,“無變化”和“切換”。 JK觸發器的符號類似于 SR Bistable Latch 的符號,如前一個教程所示,除了添加時鐘輸入。

Basic JK Flip-觸發器

<<<>>>>

先前SR雙穩態的 S 和 R 輸入現在已被兩個名為 J <的輸入所取代/ span>和 K 分別在其發明者Jack Kilby之后輸入。然后,這相當于: J = S 和 K = R 。

兩個2輸入 AND 門門控SR雙穩態現已被兩個3輸入 NAND 門取代,每個門的第三個輸入連接到 Q 和 Q 的輸出端。 SR觸發器的這種交叉耦合允許先前無效的 S =“1”和 R =“1”狀態用于產生“切換動作” “因為兩個輸入現在是互鎖的。

如果電路現在是”SET“, J 輸入被 Q 通過較低的 NAND 門。如果電路為“RESET”, K 輸入被 Q 的“0”狀態禁止通過上 NAND 門。由于 Q 和 Q 總是不同,我們可以使用它們來控制輸入。當輸入 J 和 K 等于邏輯“1”時,JK觸發器將切換,如下面的真值表所示。

真相JK函數表

然后JK觸發器基本上是一個帶有反饋的SR觸發器只有兩個輸入端子中的一個,SET或RESET在任何時候都有效,從而消除了之前在SR觸發器電路中看到的無效狀態。

同樣當 J 和 K 輸入同時處于邏輯電平“1”,時鐘輸入脈沖為“高電平”,電路將從其SET狀態“切換”到RESET狀態,或反之亦然。這導致當兩個端子都為“高”時,JK觸發器更像是T型觸發器。

雖然這個電路是時鐘SR觸發器的改進,但如果輸出 Q 在時鐘輸入的定時脈沖有時間之前改變狀態,它仍然會遇到稱為“競爭”的定時問題去“關”。為避免這種情況,定時脈沖周期( T )必須盡可能短(高頻)。由于現代TTL IC有時無法做到這一點,因此開發了大大改進的Master-Slave JK觸發器。

Master-Slave JK Flip-flop

主從觸發器通過使用串聯配置連接在一起的兩個SR觸發器消除了所有時序問題。一個觸發器充當“主”電路,其在時鐘脈沖的前沿觸發,而另一個觸發器充當“從”電路,其在時鐘脈沖的下降沿觸發。這導致兩個部分,主部分和從部分在時鐘信號的相反半周期期間被使能。

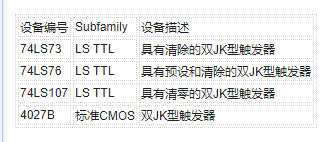

TTL 74LS73是雙JK觸發器IC,其包含兩個單獨的JK在單個芯片中鍵入雙穩態,可以制作單個或主從觸發觸發器。其他JK觸發器IC包括具有清零的74LS107雙JK觸發器,74LS109雙正邊沿觸發JK觸發器和具有預置和清除輸入的74LS112雙負邊沿觸發觸發器。

雙JK觸發器74LS73

其他流行的JK觸發器IC

主從式JK觸發器

主從式觸發器基本上是兩個門控SR觸發器,它們與從器件串聯配置連接在一起具有反相時鐘脈沖。來自“Slave”觸發器的 Q 和 Q 的輸出反饋到“Master”的輸入,“Master”觸發器的輸出為連接到“Slave”觸發器的兩個輸入。從從機輸出到主機輸入的這種反饋配置給出了JK觸發器的特性切換,如下所示。

主從JK觸發器

輸入信號 J 和 K 連接到門控“主”SR觸發器,“鎖定“輸入條件,而時鐘( Clk )輸入在邏輯電平”1“為”高“。由于“從”觸發器的時鐘輸入是“主”時鐘輸入的反相(補碼),因此“從”SR觸發器不會切換。當時鐘輸入變為“低”到邏輯電平“0”時,“主”觸發器的輸出僅被門控“從”觸發器“看到”。

當時鐘為“低”時“,”主“觸發器的輸出被鎖存,其輸入的任何其他變化都將被忽略。門控“從”觸發器現在響應由“主”部分傳遞的輸入狀態。

然后在時鐘脈沖的“從低到高”轉換時,輸入“主”觸發器被饋送到“從”觸發器的門控輸入,并且在“從高到低”轉換時,相同的輸入反映在“從”的輸出上,使得這種類型的觸發器邊緣或脈沖觸發。

然后,當時鐘信號為“高”時,電路接受輸入數據,并在時鐘信號的下降沿將數據傳遞給輸出。換句話說,主 - 從JK觸發器是一個“同步”器件,因為它只通過時鐘信號的時序傳遞數據。

在下一個教程中關于順序邏輯電路,我們將看一下用作波形發生器的多諧振蕩器,以產生時鐘信號來切換時序電路。

-

電路

+關注

關注

173文章

5966瀏覽量

172971 -

觸發器

+關注

關注

14文章

2003瀏覽量

61353

發布評論請先 登錄

相關推薦

JK觸發器基本教程,講的超詳細!!

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

JK人字拖觸發器和函數表

JK人字拖觸發器和函數表

評論