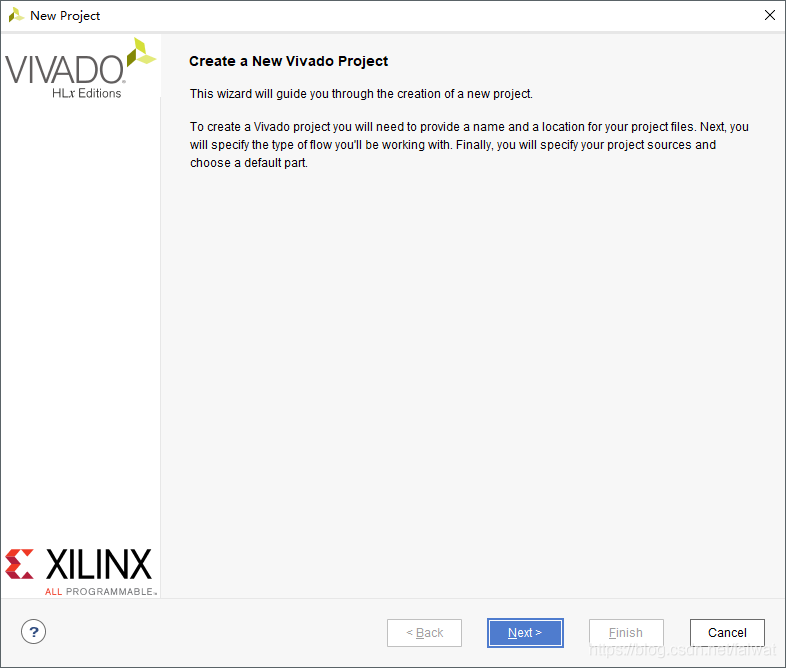

工欲善其事,必先利其器。我們 Designer 最看重的就是,工具趁不趁手。FPGA/SoC 開發,28nm 我們推薦您用 Vivado;20nm 開發,您只能用 Vivado;16nm 開發,Vivado 剛剛滴... 那怎么才能用好 Vivado 呢?

5 Vivado 中的 “邏輯調試” 功能詳解

學習如何使用 Vivado 設計套件中的 “邏輯調試(Logic Debug)”功能,以及如何在設計中添加邏輯調試 IP,如何使用 Vivado 邏輯分析器(Logic Analyzer)來操作該 IP。更多Vivado培訓視頻,敬請訪問 http://china.xilinx.com/training/vivado。

6 UltraFAST 設計方法中 “Checklist”的使用

學習如何執行 UltraFAST 設計方法中的”Checklist“功能來確保您的設計以及設計環境已為 Vivado 設計套件做好優化。”Checklist“強調了許多在 UG949 中所提到的建議。它由一系列的,針對設計流程每一階段中的問題和對應措施組成。設計前確保設計或設計環境已為Vivado優化將可以大大增加您的設計效率,同時減少設計收斂或處還能理工具的問題所花的時間。

-

邏輯

+關注

關注

2文章

833瀏覽量

29515 -

16nm

+關注

關注

0文章

32瀏覽量

27954

發布評論請先 登錄

相關推薦

FPGA開發Vivado的仿真設計案例分析

深入淺出玩轉Xilinx Vivado工具實戰設計技巧

Vivado+Zedboard之Linux開發環境搭建

關于16nm UltraScale+ 器件的工具與文檔分析和介紹

Xilinx 宣布Vivado設計套件開始支持16nm UltraScale+產品早期試用

使用VIVADO對7系列FPGA的高效設計心得

Vivado中使用debug工具步驟與調試技巧

16 款優秀的Web開發輔助工具推薦

Vivado--16nm開發最好工具

Vivado--16nm開發最好工具

評論