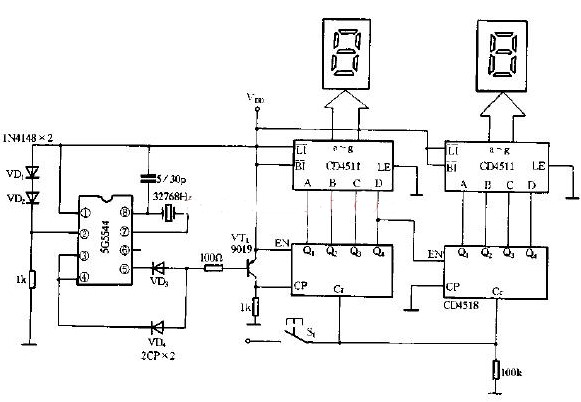

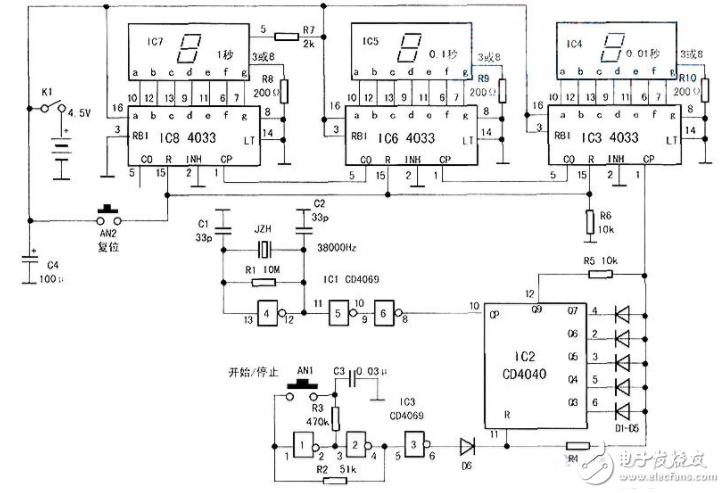

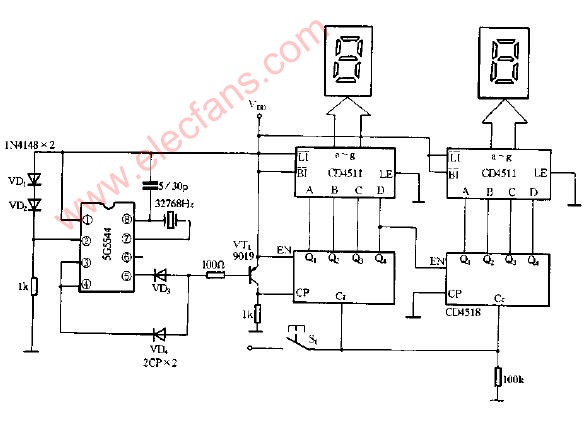

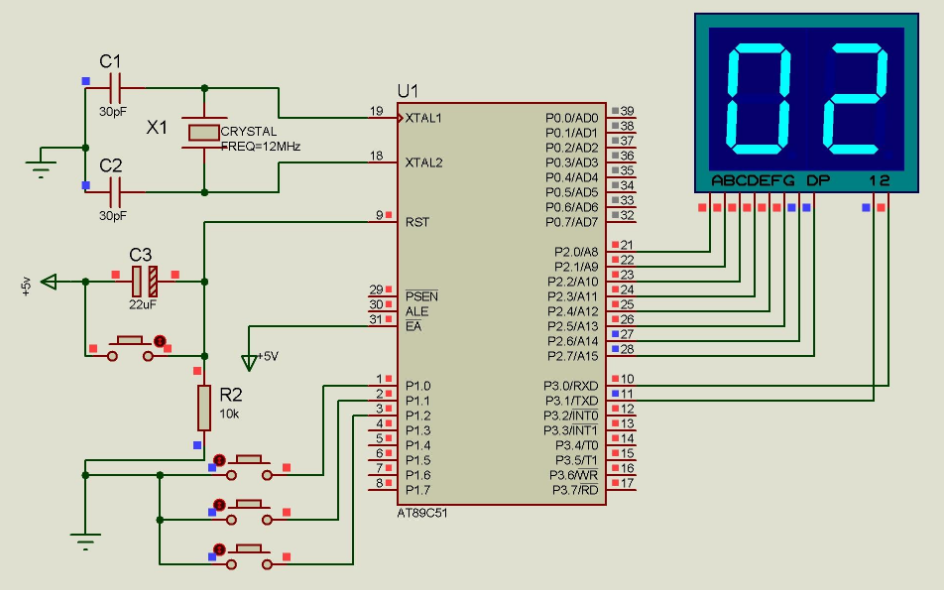

數字秒表由計數顯示電路、復位電路、控制電路與電源電路組成。通過計數電路、譯碼電路在顯示器上輸出,以上部分組成計數顯示電路;通過電源清零電路和反饋清零電路實現復位功能,構成復位電路;利用啟動開關和停止開關控制觸發器產生啟動/停止信號,實現秒表的啟動和停止動能,構成控制電路;在整個秒表中,電源電路是采用外接電源來實現的。經過布線、焊接、調試等工作,數字秒表成形。在秒表電路中利用一個譯碼器譯出計數器所計時間并經LED顯示器顯示出來,利用控制電路對秒表進行啟動/停止控制。當計時結束后,利用復位電路對其進行復位。

在整個秒表中最關鍵的是如何獲得一個精確的100HZ計時脈沖,除此之外,數字秒表需有清零控制端,以及啟動控制端、保持保持,以便數字時鐘能隨意停止及啟動。數字秒表顯示由時(12或24進制任選)、分(60進制)、秒(60進制)、百分之一秒(一百進制)組成,利用掃描顯示譯碼電路在八個數碼管顯示。

設計內容及步驟:

1、根據電路持點,用層次設計概念。將此設計任務分成若干模塊,規定每一模塊的功能和各模塊之間的接口,同時加深層次化設計概念;

2、軟件的元件管理深層含義,以及模塊元件之間的連接概念,對于不同目錄下的同一設計,如何熔合;

3、適配劃分前后的仿真內容有何不同概念,仿真信號對象有何不同,有更深一步了解。熟悉了CPLD/FPGA設計的調試過程中手段的多樣化;

4、按適配劃分后的管腳定位,同相關功能塊硬件電路接口連線;

5、所有模塊盡量采用VHDL語言設計。

-

電源

+關注

關注

184文章

17836瀏覽量

251791 -

計數器

+關注

關注

32文章

2261瀏覽量

94982 -

觸發器

+關注

關注

14文章

2003瀏覽量

61347

發布評論請先 登錄

相關推薦

基于CD4033的數字秒表的設計

SDH數字微波通信技術的組成、特點及應用介紹

基于單片機的數字秒表的設計簡介

一種基于FPGA的數字秒表設計方法

基于8051單片機的數字電子秒表的設計

基于單片機的數字秒表

數字秒表的組成及主要設計步驟介紹

數字秒表的組成及主要設計步驟介紹

評論