debug,尤其是通信芯片的debug,可以有很多的方法。一個(gè)數(shù)據(jù)幀從進(jìn)入到輸出,可以在通路上的關(guān)鍵節(jié)點(diǎn)處設(shè)置監(jiān)測(cè)如各種計(jì)數(shù)器等,可通過VIO(xilinx)定時(shí)上報(bào)實(shí)時(shí)狀態(tài)。可以把VIO的各個(gè)信號(hào)線設(shè)置成類似于CPU總線的結(jié)構(gòu),監(jiān)測(cè)計(jì)數(shù)器或者狀態(tài)寄存器編成相應(yīng)的地址,輪詢讀取回PC,在PC上通過TCL或者其它語言捕獲數(shù)據(jù)。甚至可以將多個(gè)FPGA芯片都通過VIO進(jìn)行調(diào)試,遠(yuǎn)程操作,效率也可以大大提升。另外,也可以設(shè)置專門的測(cè)試幀,在里面打各種不同大小的閉環(huán),層層檢測(cè),發(fā)現(xiàn)問題。

這個(gè)VIO比chipscope有多大優(yōu)勢(shì)?

原理是一樣的,不同的就是可以方便操控,可以寫腳本抓取數(shù)據(jù),還可以遠(yuǎn)程操控。VIO有輸入也有輸出,可以實(shí)時(shí)的配置寄存器。http://xilinx.eetrend.com/blog/11987,VivadoVIO (virtual input output)虛擬IO使用;

一、使用方法概述

一般情況下VIO用在設(shè)計(jì)中,可以提供模擬IO(我們主要用到模擬輸出接口的功能)。如圖1所示,紅框內(nèi)vio_0模塊的兩個(gè)輸出probe_out[0:0]和probe_out[7:0]都可以接到其他模塊直接使用,但是我們不需要用到板子上的實(shí)際接口(比如按鍵)。那么為什么我們?cè)?a href="http://www.qldv.cn/v/tag/1247/" target="_blank">電腦上點(diǎn)一點(diǎn)鼠標(biāo),就可以將數(shù)據(jù)傳遞到FPGA內(nèi)部呢?數(shù)據(jù)是通過什么傳輸?shù)紽PGA內(nèi)部?答案是JTAG,電腦上的VIVADO軟件可以通過JTAG軟件與FPGA實(shí)現(xiàn)通信,這就是VIO模塊在FPGA內(nèi)部模擬IO引腳的原理。

圖1 VIO IP核

1、VIO IP核的配置

下面用實(shí)際例子說明VIO IP核的配置過程:

在某設(shè)計(jì)中,需要使用按鍵出發(fā),但是板子上沒有設(shè)計(jì)按鍵,所以需要使用VIO模擬按鍵輸入還有其他信號(hào)的輸出。具體過程如下:

(1)例化VIO IP核 ;

(2)參數(shù)配置,配置輸入探針數(shù)量和輸出探針數(shù)量,如圖2所示。分別可以設(shè)置0-256個(gè)。(一般輸入探針用不到,最常用的是輸出探針,在這里這兩種探針都在圖里體現(xiàn)了)。

圖2 探針數(shù)量設(shè)置

(3)配置輸出探針數(shù)據(jù)位寬及初始值

輸出探針的數(shù)據(jù)位寬,及初始化數(shù)據(jù)(in hex)配置如圖3所示

圖3配置輸出探針數(shù)據(jù)位寬及初始值

3、 VIO IP核的例化

VIO IP核代碼實(shí)例化如下圖所示。

ILA_wrapper ILA(

.clk ( ),

.probe0 (),

.probe1 (),

.probe_out0 (),

.probe_out1 (),

.probe_in0 ()

);

4、 VIO IP核的使用

在hw_vio界面加入輸出探針,并且配置對(duì)應(yīng)的參數(shù),此時(shí)FPGA內(nèi)部的輸出探針就會(huì)相應(yīng)地發(fā)出信號(hào),如圖4所示。

圖4 VIO IP核的使用

二、使用VIO實(shí)現(xiàn)大量寄存器讀寫

1、背景

在FPGA調(diào)試中,如果沒有CPU接口及操作系統(tǒng),但同時(shí)希望能夠有一種類似于有CPU且可以實(shí)時(shí)在線讀寫FPGA內(nèi)部狀態(tài)寄存器或者配置FPGA內(nèi)部寄存器的功能,就可以采用VIO來實(shí)現(xiàn)一個(gè)模擬的CPU接口,以下進(jìn)行詳細(xì)的介紹。

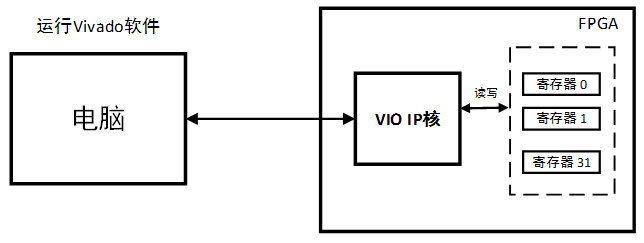

2、 原理框圖及VIO字段定義

在Vivado 2016.2 軟件環(huán)境,Zedboard硬件平臺(tái)下,實(shí)現(xiàn)了一個(gè)示例工程,該工程的功能是,電腦運(yùn)行Vivado軟件,并通過Jtag與zedboard相連,利用VIO模擬CPU接口,實(shí)現(xiàn)寄存器讀寫功能(寄存器數(shù)量為32個(gè),位數(shù)為32位),如圖5所示。

圖5原理框圖

其參數(shù)配置說明如下:

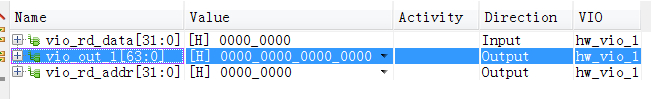

如圖6所示,vio_out_1的前32位是寫地址,后32位是寫數(shù)據(jù);

圖6 VIO寫地址與寫數(shù)據(jù)

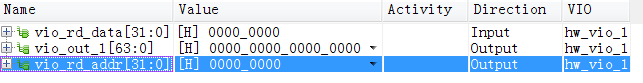

如圖7所示,vio_rd_addr代表讀地址;

圖7 VIO讀地址

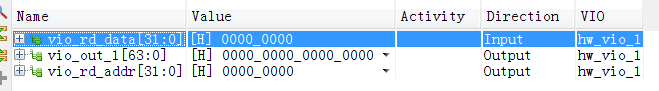

如圖8所示,vio_rd_data代表讀數(shù)據(jù)

圖8 VIO讀數(shù)據(jù)

3、操作示例

這里給出一個(gè)寄存器讀寫的例子,在這里不用tcl腳本,直接用圖形界面,使用更加方便。

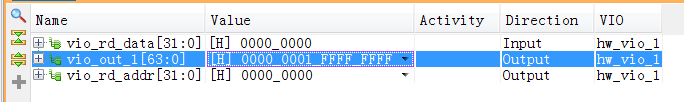

(1)給地址為1的寄存器寫入數(shù)據(jù)32'hffff_ffff,即配置vio_out_1[63:0]為64'h0000_0001_FFFF_FFFF,如圖9所示。

圖9 VIO寫入數(shù)據(jù)

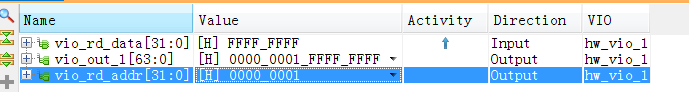

(2) 將讀地址設(shè)置為1,觀察讀數(shù)據(jù)變化,如圖10所示。

圖10 VIO讀數(shù)據(jù)

觀察圖10可以發(fā)現(xiàn),配置讀地址vio_rd_addr為32'h0000_0001后,讀數(shù)據(jù)vio_rd_data[31:0]由圖9中的32'h0000_0000變?yōu)閳D10中的32'hffff_ffff,與寫入的數(shù)據(jù)相同,寄存器讀寫操作成功。

三、源代碼

1、約束文件源碼

set_property PACKAGE_PIN Y9 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

上述源碼及約束文件適用于Xilinx的Zedboard開發(fā)板,已上板驗(yàn)證。另外,上面僅是原理性的簡單演示,可以把寄存器應(yīng)用于自己設(shè)計(jì)中的各個(gè)內(nèi)部關(guān)鍵模塊中,調(diào)試的過程中,實(shí)時(shí)的從VIO接口獲取數(shù)據(jù),或者動(dòng)態(tài)的配置FPGA內(nèi)部的寄存器,使其按照寄存器約定的功能運(yùn)行。雖沒有CPU,卻等效有了CPU,可大大提高FPGA調(diào)試的效率。VIO占用資源情況與chipscope類似。

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427250 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121161

原文標(biāo)題:使用VIVADO中VIO模擬CPU接口進(jìn)行在線寄存器讀寫調(diào)試(附源代碼)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

XILINX FPGA Debug with VIO and TCL

使用VIO IP在ISE Design SUite軟件中調(diào)試時(shí)遇到以下錯(cuò)誤該怎么辦?

Chipscope中的ILA,VIO和ATC2有什么區(qū)別?

Chipscope學(xué)習(xí)教程

CHipScoPe使用

Chipscope的使用

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

SDK和ChipScope配合工作

chipscope使用教程以及FPGA在線調(diào)試的方法

Vivado之VIO原理及應(yīng)用

VIO比chipscope有多大優(yōu)勢(shì)?

VIO比chipscope有多大優(yōu)勢(shì)?

評(píng)論