Codasip推出低功耗嵌入式處理器核和設計自動化工具集CodasipStudio

與同級內核相比,CodasipL110每瓦性能提高50%,代碼規模縮小20% 德國慕尼黑,2024年....

Codasip高可靠性的定制計算解決方案滿足不同領域的需求

又到一年尾牙時!11月的第二個星期對于Codasip來說是個繁忙且收獲滿滿的一周,我們以RISC-V....

Codasip致力于提供卓越的定制計算解決方案

2023第29屆中國集成電路設計業年會(ICCAD)是中國半導體和集成電路設計領域的一場盛會,來自世....

Codasip利用RISC-V向量擴展實現領域專用加速器

Codasip Labs 致力于創新并深耕于創新的商業化落地。隨著人工智能(AI)和機器學習(ML)....

Codasip推出全新高度可配置的RISC-V基準處理器系列

RISC-V定制計算領域領導者 Codasip 今天宣布推出全新高度可配置的RISC-V基準處理器系....

可定制RISC-V ISA的優勢

多樣性與兼容性的統一 處理器供應商一直試圖在其產品周圍創建一個龐大的軟件生態系統,因為這可以產生黏性....

Codasip向客戶提供Tessent Enhanced Trace Encoder增強型追蹤編碼器解決方案

德國慕尼黑,2023年9月5日——RISC-V定制計算領域的領導者Codasip宣布:公司現在可為其....

處理器設計技能的短缺有哪些

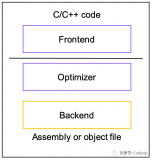

? 眾所周知,使用 "現成 "處理器內核的傳統設計方法存在局限性。傳統上,軟件工程師試圖使代碼適應所....

Codasip的系列RISC-V處理器助力RISC-V生態建設

德國慕尼黑,2023年6月—RISC-V定制計算領域的領導者Codasip日前宣布,其已選擇 Sma....

Codasip致力于創建一個高效的數字耳朵

? Codasip Labs之前與NimbleAI的項目合作旨在于推動神經形態視覺的邊界擴展。而如此....

看看4種不同類型的CPU漏洞

在設計一個復雜的處理器內核時,可能會出現1000到2000個不等的bug,經驗告訴我們這是事實,盡管....

Codasip協作引領RISC-V的廣泛采用

在業界屢獲獎項的Codasip L31是一個小型、高效的32位嵌入式RISC-V處理器核,針對低功耗....

為處理器驗證創建一個“瑞士奶酪模型”,以保證高效的驗證品質!

在應用于處理器驗證的瑞士奶酪模型中,其原理類似于航空業:如果有一條直接穿過所有切片的路徑,那么飛機就....

是什么定義了處理器漏洞的復雜性以及如何檢測它?

為了衡量一個漏洞的復雜性,我們可以對漏洞進行分類,供整個處理器驗證團隊來使用。在之前的一篇博文中,我....

Codasip宣布新人事任命 滿足客戶對可定制RISC-V處理器的強勁需求

可定制RISC-V處理器知識產權(IP)的領導者Codasip日前宣布:已任命胡征宇(Julian ....