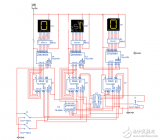

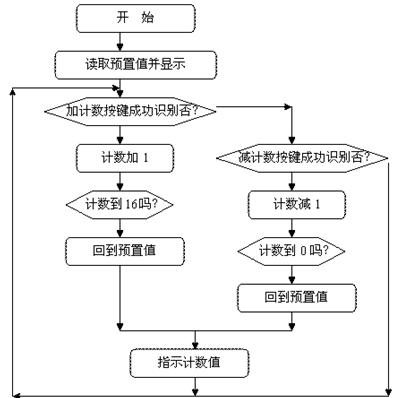

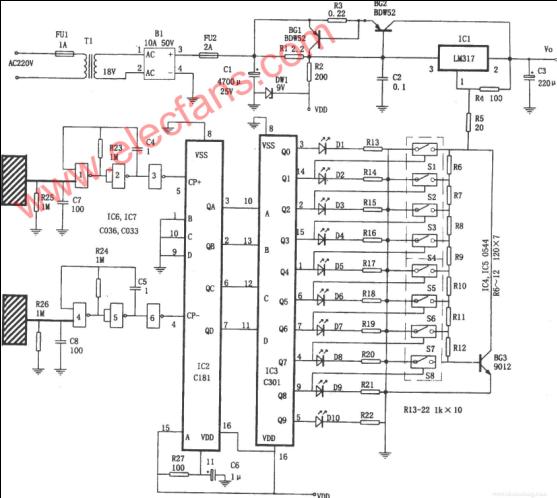

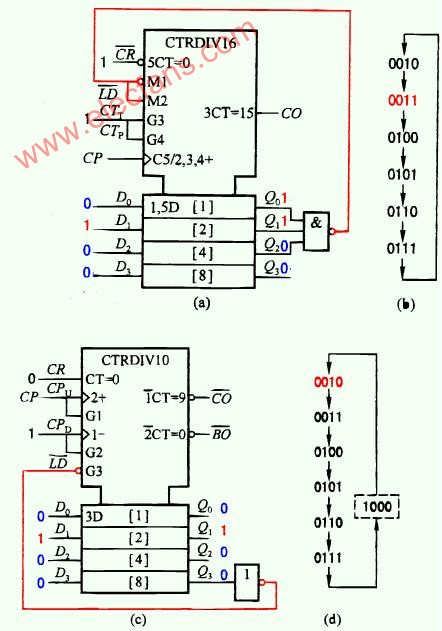

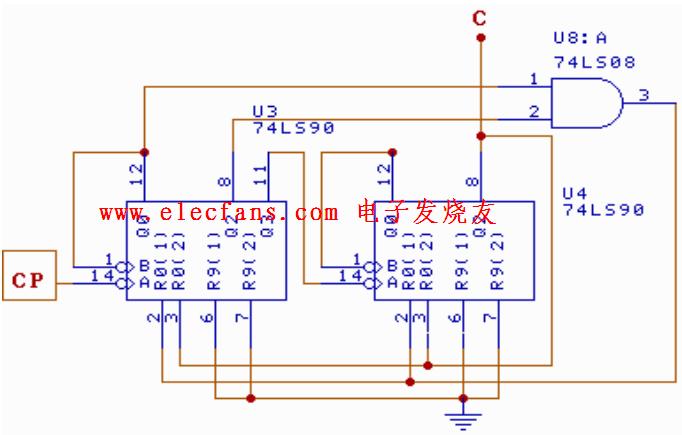

C181 2-10進制可預置可逆計數(shù)器的應用線路圖

- 計數(shù)器(91962)

相關推薦

SIMATIC S7-1500 PLC SIMATIC計數(shù)器-加計數(shù)器

加計數(shù)器(S_CU)在計數(shù)初始值預置輸入端S上有上升沿時,PV裝入預置值,輸入端CU每檢測到一次上升沿,當前計數(shù)值CV加1(前提是CV 小于999);當前計數(shù)值大于0時,Q輸出為高電平“1”;當R端子的狀態(tài)為“1”時,計數(shù)器復位,當前計數(shù)值CV為“0”,輸出也為“0”。加計數(shù)器指令和參數(shù)見圖2

2023-04-27 15:38:22 741

741

741

741

可預置同步4位二進制計數(shù)器;同步復位-74HC_HCT163_Q100

可預置同步4位二進制計數(shù)器;同步復位-74HC_HCT163_Q100

2023-02-21 18:35:38 0

0

0

0可預置同步4位二進制向上/向下計數(shù)器-74HC_HCT193_Q100

可預置同步 4 位二進制向上/向下計數(shù)器-74HC_HCT193_Q100

2023-02-15 19:39:51 0

0

0

0基于FPGA的十進制計數(shù)器

本方案是一個基于 FPGA ?的十進制計數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進制計數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實現(xiàn)。

2022-12-20 14:52:25 2

2

2

2十進制計數(shù)器的工作原理

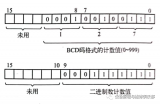

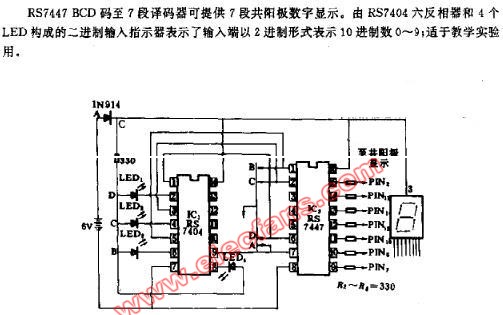

二進制編碼的十進制是一個串行數(shù)字計數(shù)器,可計數(shù)十位數(shù)字,它會為每個新的時鐘輸入重置。由于它可以通過10種獨特的輸出組合,因此也被稱為“十進制(BCD)計數(shù)器”。十進制計數(shù)器可以計數(shù)0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11019

11019

11019

11019

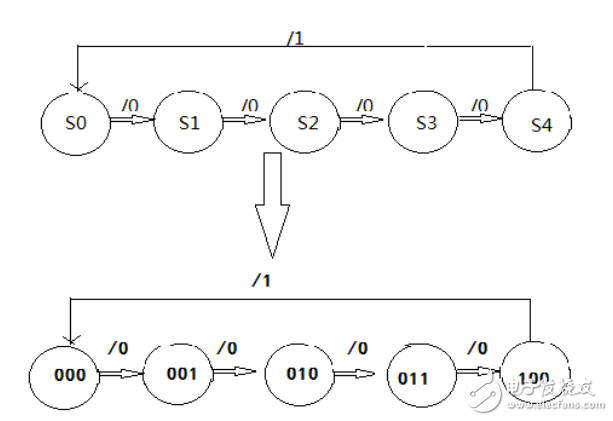

N進制計數(shù)器的實現(xiàn)

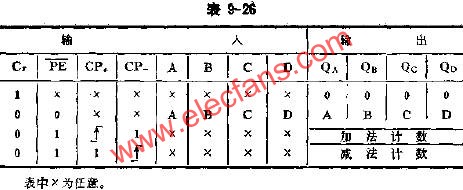

,在用預置數(shù)法組成任意進制計數(shù)器時,同樣應該加以區(qū)分。為了能夠正確使用集成計數(shù)器,應該首先認識常用的集成計數(shù)器具備哪些擴展功能。下面,我們就針對一些具有典型代表意義的集成計數(shù)器芯片進行研究。圖

2008-07-05 13:41:26

74ls160價格 74ls160十進制計數(shù)器簡介

芯片74ls160是十進制計數(shù)器,這種同步可預置十進計數(shù)器是由四個D型觸發(fā)器和若干個門電路構成。

2021-06-05 14:35:38 12686

12686

12686

1268674ls190應用電路圖大全(五款74ls190不同進制計數(shù)器電路)

本文主要介紹了五款74ls190應用電路圖。包括了60和100進制計數(shù)器(遞增)電路,56進制遞減計數(shù)器與100進制遞減計數(shù)器電路和2位十進制可加減計數(shù)器電路。

2018-05-28 16:18:11 54071

54071

54071

54071

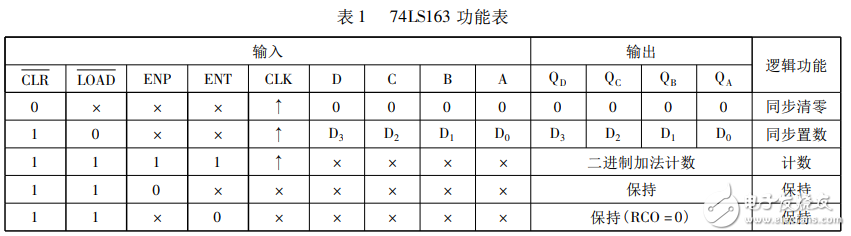

74ls163應用電路圖大全(N進制計數(shù)器\分頻電路\時鐘脈沖)

本文主要介紹了74ls163應用電路圖大全(N進制計數(shù)器\分頻電路\時鐘脈沖)。74LS163是(模16)四位二進制同步計數(shù)器。該計數(shù)器能同步并行預置數(shù)據(jù),同步清零,具有清零、置數(shù)、計數(shù)和保持四種

2018-05-08 14:27:23 51924

51924

51924

51924

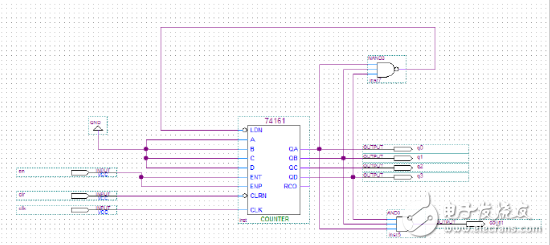

74ls163實現(xiàn)任意進制計數(shù)器

本文主要介紹了74ls163實現(xiàn)任意進制計數(shù)器。74LS163是集成4位二進制加法計數(shù)器,功能表如表1所示。其中CLK為時鐘脈沖輸入端、ENP及ENT為計數(shù)控制端、LOAD為同步預置數(shù)控制端、CLR

2018-05-08 12:10:14 78487

78487

78487

78487

同步計數(shù)器74ls162設計24進制計數(shù)器

本文首先介紹了計數(shù)器種類與應用,其次介紹了74LS160并行置零法設計24進制計數(shù)器電路圖,最后介紹了74ls162設計24進制計數(shù)器原理電路圖。

2018-05-08 11:46:43 54648

54648

54648

5464874ls160和74ls161區(qū)別

本文主要介紹了74ls160和74ls161區(qū)別。74ls161為四位二進制,74ls160 為2-10進制;且都為同步可預置計數(shù)器。74ls161 是4位二進制同步計數(shù)器(直接清除),74ls160 是4位十進制同步計數(shù)器(直接清除)。

2018-05-08 10:23:35 113147

113147

113147

113147

74ls160十進制計數(shù)器

本文主要介紹了74ls160十進制計數(shù)器電路的設計與實現(xiàn)。74LS160是二~十進制同步可預置計數(shù)器,1腳Cr為清零端,低電平有效.2腳CP為時鐘脈沖輸人端,上升沿觸發(fā).3~6V腳D1一D4為數(shù)據(jù)

2018-01-18 15:14:45 182091

182091

182091

182091

74LS161集成計數(shù)器電路(2、3、4、6、8、10、60進制計數(shù)器)

本文主要介紹了74LS161集成計數(shù)器電路(2、3、4、6、8、10、60進制計數(shù)器)。74LS161是4位二進制同步計數(shù)器,該計數(shù)器能同步并行預置數(shù)據(jù),具有清零置數(shù),計數(shù)和保持功能,具有進位輸出端

2018-01-18 10:56:39 324594

324594

324594

324594

74ls161制作24進制計數(shù)器設計

74ls161為二進制同步計數(shù)器,具有同步預置數(shù)、異步清零以及保持等功能。兩片74ls161可設計一個24進制計數(shù)器。

2018-01-16 15:30:46 110315

110315

110315

110315

74ls161構成12進制計數(shù)器設計

74LS160是十進制計數(shù)器,要實現(xiàn)十二進制計數(shù)器必須用兩片實現(xiàn)級聯(lián),把各位芯片預置1,當數(shù)碼管顯示9時,個位芯片開始進位即B端為0C端為1,經(jīng)過與非門輸出高電平,十位芯片開始工作,十位芯片由0變?yōu)?/div>

2018-01-16 15:17:32 111115

111115

111115

111115

74ls90設計60進制計數(shù)器

60進制計數(shù)器,由于24進制、60進制計數(shù)器均由集成計數(shù)器級聯(lián)構成,且都包含有基本的十進制計數(shù)器,從設計簡便考慮,芯片選擇同步十進制計數(shù)器

2017-12-22 13:55:48 148134

148134

148134

148134

基于74LS160的N進制計數(shù)器仿真設計

針對任意進制(N進制)計數(shù)器的設計目的,采用反饋復零法對基于同步十進制計數(shù)器7415160進行設計,分別采用異步清零法實現(xiàn)了6進制計數(shù)器和同步置數(shù)法實現(xiàn)7進制計數(shù)器的設計,通過應用EWB軟件對所設

2017-12-21 17:08:37 60783

60783

60783

60783

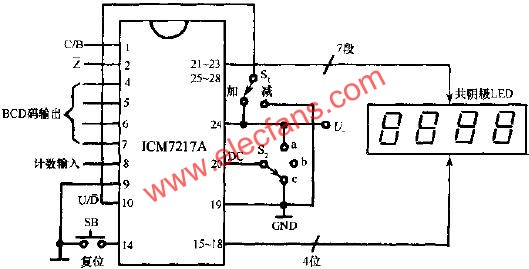

基于74LS192千進制可逆計數(shù)器的設計與研究

計數(shù)器是一個用以實現(xiàn)計數(shù)功能的時序部件,它主要用于時鐘脈沖計數(shù)、數(shù)字系統(tǒng)的定時、分頻和執(zhí)行數(shù)字運算以及其他特定的邏輯功能,在科研、工業(yè)、農(nóng)業(yè)等各個領域中具有重要的作用。本文以74LS192十進制可逆

2017-12-21 11:34:45 7718

7718

7718

7718

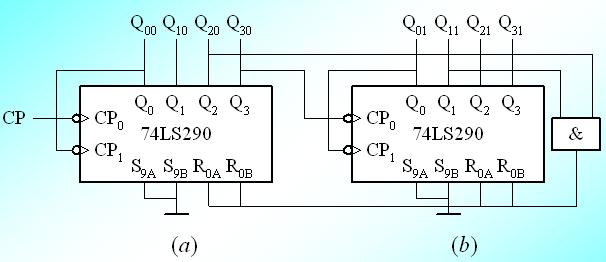

24進制計數(shù)器的設計

討論,但各文獻側重于多次置數(shù)控制方法的實現(xiàn)以及側重multsim仿真軟件的應用。因此義中主要討論的是利用已有集成計數(shù)器設計任意計數(shù)器時,其實現(xiàn)途徑的靈活性與多樣性問題。文中以2片74290實現(xiàn)24進制計數(shù)器為例,詳細分析其實現(xiàn)

2017-11-09 16:36:16 81

81

81

81十進制計數(shù)器/分頻器

約翰遜MC14017B是五級十進制計數(shù)器內(nèi)置代碼轉(zhuǎn)換器。 高速運行和約翰遜spike-free輸出是通過使用十進制計數(shù)器的設計。 十個解碼輸出通常是低,只在適當?shù)氖?b style="color: red">進制時間走高。 輸出的正向變化的時鐘脈沖。 這部分可用于分頻應用程序以及十進制計數(shù)器或十進制譯碼顯示應用程序。

2017-04-06 09:03:48 28

28

28

28基于Proteus的任意進制計數(shù)器設計與仿真

提出一種基于Proteus 軟件的任意進制計數(shù)器的設計。以74LS163 集成計數(shù)器為基礎,用置數(shù)法設計了兩種48 進制計數(shù)器,采用Proteus 軟件對計數(shù)器進行仿真。結果表明,Proteus 軟件具有實現(xiàn)48 進制計數(shù)器的功能。仿真圖像清晰,能快速準確地驗證設計結果。

2016-07-29 18:53:03 24

24

24

24集成計數(shù)器實現(xiàn)N進制計數(shù)

集成計數(shù)器實現(xiàn)N進制計數(shù)集成計數(shù)器實現(xiàn)N進制計數(shù)集成計數(shù)器實現(xiàn)N進制計數(shù)

2016-06-08 14:28:43 15

15

15

15采用歸零法的N進制計數(shù)器原理

計數(shù)器是一種重要的時序邏輯電路,廣泛應用于各類數(shù)字系統(tǒng)中。介紹以集成計數(shù)器74LS161和74LS160為基礎,用歸零法設計N進制計數(shù)器的原理與步驟。用此方法設計了3種36進制計數(shù)器,并

2012-03-20 10:21:38 95

95

95

95基于MSI的N進制計數(shù)器設計方法

計數(shù)器是數(shù)字邏輯系統(tǒng)中的基本部件,它是數(shù)字系統(tǒng)中用得最多的時序邏輯電路,本文主要闡述了用中規(guī)模集成計數(shù)器設計任意進制同步加法計數(shù)器的設計思想,并對設計方法和步驟作

2012-02-28 11:41:43 6157

6157

6157

6157

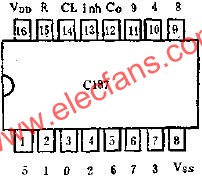

C187 2-10進制計數(shù)器/脈沖分配器的應用線路圖

C187是由5級計數(shù)單元數(shù)組成的約翰遜編碼計數(shù)器,它本身帶有譯碼器.約翰遜計數(shù)器實質(zhì)上是一種串行移位寄存器,將末級的Q輸出反饋到第一級的輸入D而構成的,主要特

2010-10-19 16:19:54 2379

2379

2379

2379

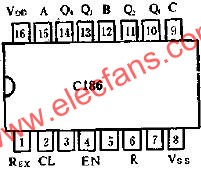

C186任意進制串行計數(shù)器的應用線路圖

C186是任意進制串行計數(shù)器,所謂任意進制,即在進行計數(shù)或分頻時,不需外加門電路,依靠本身管腳引出線的

2010-10-19 16:09:24 1361

1361

1361

1361

C183二進制同步加法計數(shù)器的應用線路圖

C183與C180基本上是一樣的,不同的僅是計數(shù)碼制不同,C180是2-10進制,C183是四位二進制.C183的管腳外引線排列和功用

2010-10-19 15:48:59 1042

1042

1042

1042

C182可預置數(shù)1/N計數(shù)器的應用線路圖

C182可預置數(shù)1/N計數(shù)器基本上是一個減法計數(shù)器,均由四個"T"型觸發(fā)器和附加控制門組成,具有級連N個計數(shù)器

2010-10-19 15:23:07 963

963

963

963

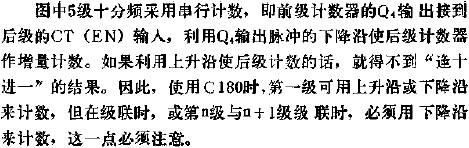

C180組成時基分頻器線路圖

圖中所示是用C180 2-10進制同步加法計數(shù)器組成的時基分頻器(多級串行計數(shù))線路.圖中晶體振蕩器采用振蕩頻率為

2010-10-19 15:03:29 1511

1511

1511

1511

C180 2-10進制同步加法計數(shù)器的應用線路圖

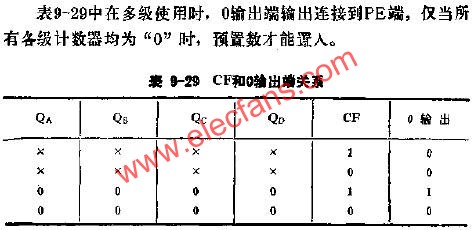

C180(CMOS)2-10進制同步加法計數(shù)器由同步的四級D型觸發(fā)器組成.它的管腳外引線排列和功用如圖所示,C180 2-10進制

2010-10-19 14:56:14 1889

1889

1889

1889

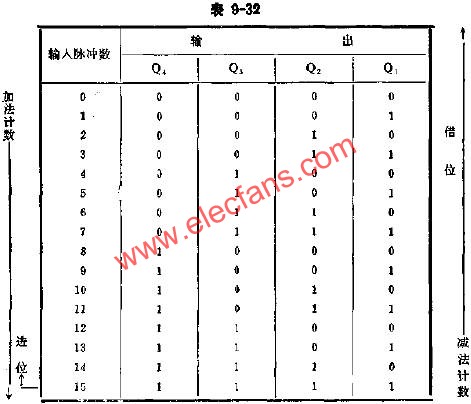

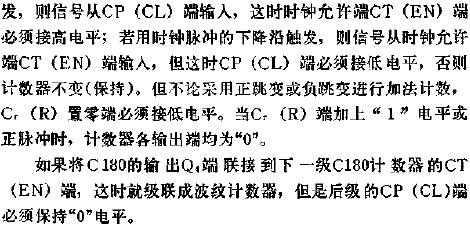

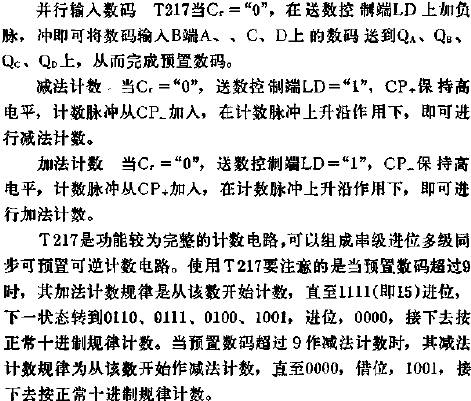

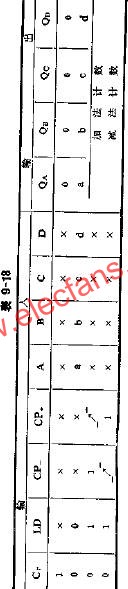

T217 2-10進制同步可預置可逆計數(shù)器的應用電路圖

T217是2-10進制同步可預置可逆計數(shù)器,能同時作加法計數(shù)和減法計數(shù).它的主要電參數(shù)為:電源電流ICC小于100MA,計數(shù)

2010-10-19 14:41:30 811

811

811

811

T216 2-10進制同步可預置計數(shù)器的應用線路圖

T216是2-10進制同步可預置計數(shù)器,它的電源電流ICC小于94MA,計數(shù)工作頻率約為10MHZ,CP到輸出的平均延遲時間小于45NS,

2010-10-19 14:33:22 775

775

775

775

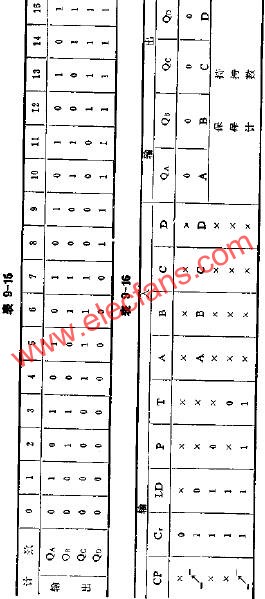

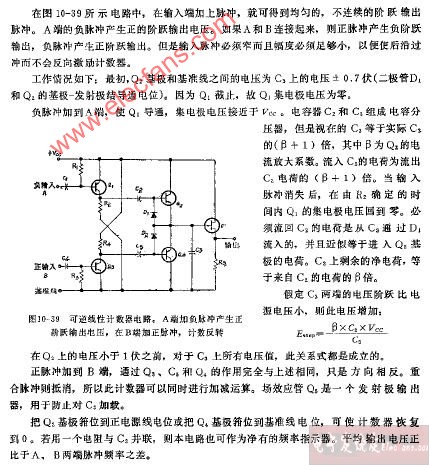

T215組成的階梯波發(fā)生器線路圖

圖中所示是用TTL T215同步可預置可逆計數(shù)器組成的階梯波發(fā)生器線路,圖中,除一塊T215外,用了四個二極管,四個偏

2010-10-19 14:16:13 1597

1597

1597

1597

T215 2-16進制同步可預置可逆計數(shù)器的應用電路圖

T215是2-16進制同步可預置可逆計數(shù)器.它能同時作加法計數(shù)和減法計數(shù).它的主要電參數(shù)為:電源電流ICC小于100M

2010-10-19 14:09:21 1197

1197

1197

1197

T214 2-16進制同步可預置計數(shù)器的應用電路圖

T214 2-16進制同步可預置計數(shù)器,它主主要電參數(shù)是:電源電流ICC小于94MA,計數(shù)工作頻率FM>10MHZ,CP到輸出的平均延遲

2010-10-19 13:51:41 1388

1388

1388

1388

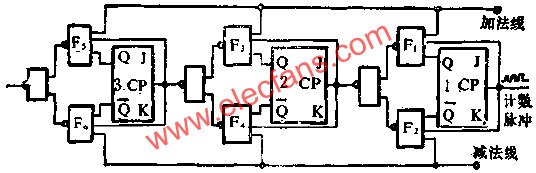

T211 2-5-10進制可預置計數(shù)器的應用電路圖

T211計數(shù)器和T210計數(shù)器相比,在形成BCD-8421碼或5421碼計數(shù)輸出上完全一樣,但T211增加了四位數(shù)預置的功能.T211

2010-10-19 13:20:34 1098

1098

1098

1098

可預置可逆4位計數(shù)器

利用AT89S51單片機的P1.0-P1.3接四個發(fā)光二極管L1-L4,用來指示當前計數(shù)的數(shù)據(jù);用P1.4-P1.7作為預置數(shù)據(jù)的輸入端,接四個撥動開關K1-K4,用P3.6/WR和P3.7/RD

2010-09-24 15:44:37 60

60

60

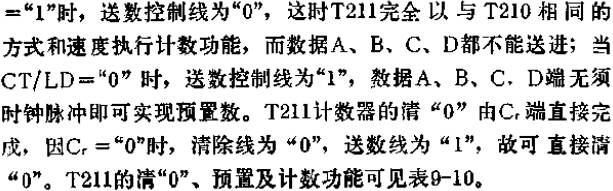

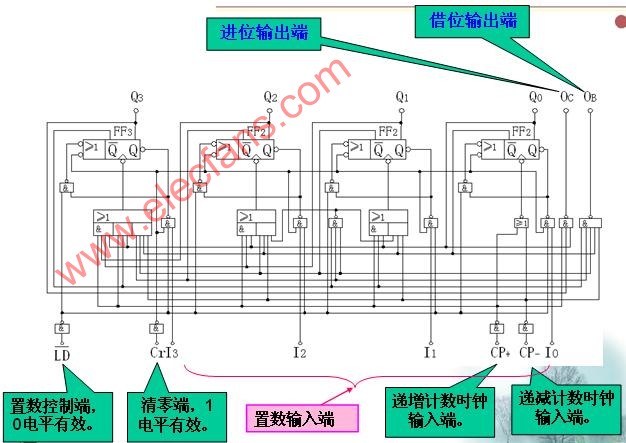

60J-K觸發(fā)器組成可逆計數(shù)器電路圖

圖中所示是J-K觸發(fā)器組成可逆計數(shù)器電路。要求計數(shù)器能夠在一定條件下,從加法計數(shù)改換成減法計數(shù),也可以

2010-09-24 01:03:53 2756

2756

2756

2756

十進制計數(shù)器,十進制計數(shù)器原理是什么?

十進制計數(shù)器,十進制計數(shù)器原理是什么?

二進制計數(shù)器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特

2010-03-08 13:19:54 23684

23684

23684

23684什么是二進制計數(shù)器,二進制計數(shù)器原理是什么?

什么是二進制計數(shù)器,二進制計數(shù)器原理是什么?

計數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數(shù),還可以實現(xiàn)

2010-03-08 13:16:34 29984

29984

29984

29984同步二進制計數(shù)器

同步二進制計數(shù)器

1. 同步與異步二進制加法計數(shù)器比較態(tài)序表和工作波形一樣電路結構不同: 異步二進制加法

2009-09-30 18:37:29 10744

10744

10744

10744

24進制計數(shù)器電路

24進制計數(shù)器電路

在百進制基礎上,采用反饋歸零法即可組成二十四進制計數(shù)器。計數(shù)范圍為0~23,24為過渡狀態(tài),當高位計數(shù)至2、低位計數(shù)至4

2009-09-16 15:50:29 19522

19522

19522

19522

100進制計數(shù)器

100進制計數(shù)器一、 實驗目的:1、 熟悉MAX+PLUS環(huán)境的基本操作。2、 掌握VHDL和原理圖的設計輸入方式。3、 設計100進制計數(shù)器。二、&

2009-06-28 00:07:21 7414

7414

7414

7414可逆、可預置計數(shù)器CD4029構成的任意N分頻減法計數(shù)電路

圖3是可逆、可預置計數(shù)器CD4029構成的任意N分頻減法計數(shù)電路,U/D接“L”電平進行減法計數(shù),B/D接“L”電平按BCD輸出碼進行計數(shù),低位的Co進位到高位的CT輸

2009-06-22 07:44:38 4593

4593

4593

4593

可預置可逆4位計數(shù)器

可預置可逆4位計數(shù)器 1. 實驗任務 利用AT89S51單片機的P1.0-P1.3接四個發(fā)光二極管L1-L4,用來指示

2009-04-16 09:44:35 1513

1513

1513

1513

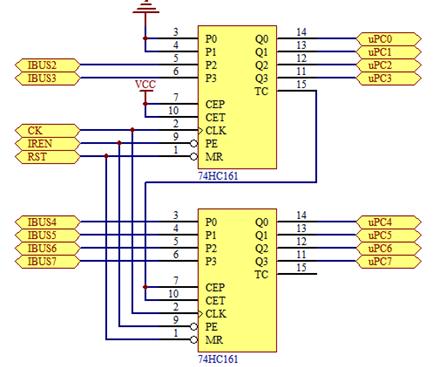

uPC(八位帶預置計數(shù)器)原理圖

uPC是由兩片74HC161構成的八位帶預置計數(shù)器,預置的數(shù)據(jù)來自IBUS。指令IBUS[7:0]的高六位被接到uPC預置的高六

2009-04-01 21:12:00 2254

2254

2254

2254

74LS161構成的五十(50)進制計數(shù)器電路圖-原理圖

兩片4位二進制數(shù)加法計數(shù)器74LS161級聯(lián)成五十進制計數(shù)器。

2009-03-28 10:10:23 33045

33045

33045

33045

100進制計數(shù)器

100進制計數(shù)器

異步級聯(lián)法組成的100進制計數(shù)器

定義集成計數(shù)器的高低位,1#芯片為低位(相當

2008-07-05 14:25:17 5412

5412

5412

5412

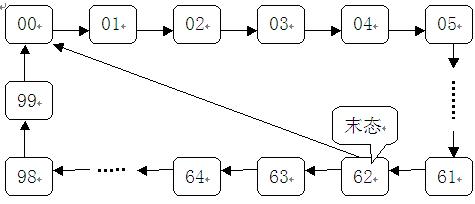

先級聯(lián)后預置數(shù)構成的63進制計數(shù)器

先級聯(lián)后預置數(shù)構成的63進制計數(shù)器:我們同樣也可以先用級聯(lián)法組成10i計數(shù)器、或16i計數(shù)器,再用預置

2008-07-05 13:58:00 1405

1405

1405

1405

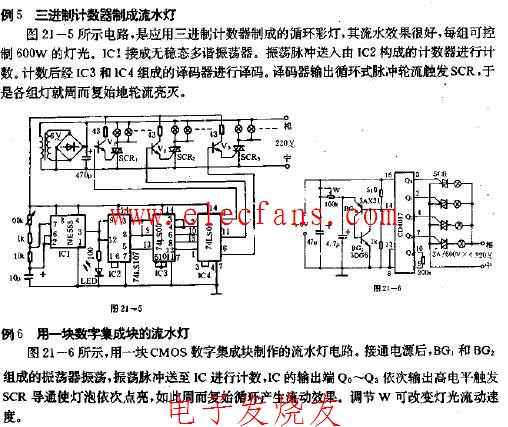

三進制計數(shù)器制成流水燈

三進制計數(shù)器制成流水燈是應用三進制計數(shù)器制成的循環(huán)彩燈,其流水效果很好,每組可控制600W的燈光,IC1接成無穩(wěn)態(tài)多諧振蕩器。

2007-12-26 19:27:57 2273

2273

2273

2273

十進制計數(shù)器

十進制計數(shù)器

二進制計數(shù)器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特別是當二進制數(shù)的位數(shù)較多時,閱讀非常困難,還

2007-06-20 13:46:05 3559

3559

3559

3559 電子發(fā)燒友App

電子發(fā)燒友App

評論