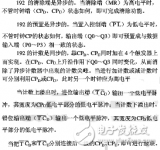

由題目及其要求分析可知,首先要使用74LS192或40192設計一個4進制計數器和一個7進制計數器,然后通過數碼管來顯示狀態。兩種進制間的切換可以通過一個單刀雙擲開關來實現。其重點和難點在于設計一個4進制計數器和一個7進制計數器。

通過分析74LS192和40192的特點,發現可以使用清零法來設計一個4進制計數器,而7進制則不能直接通過置數或者清零獲得。因此我選擇采用置數法將74LS192或40192設計的從0到7的8進制計數器改裝為從1到7的計數器,然后再通過一個減法器使從1到7的計數器變為從0到6的7進制計數器。而減法器可以使用集成加法器和四個異或門來實現。

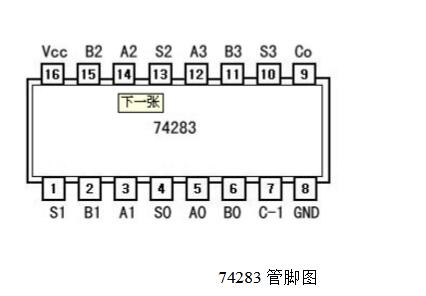

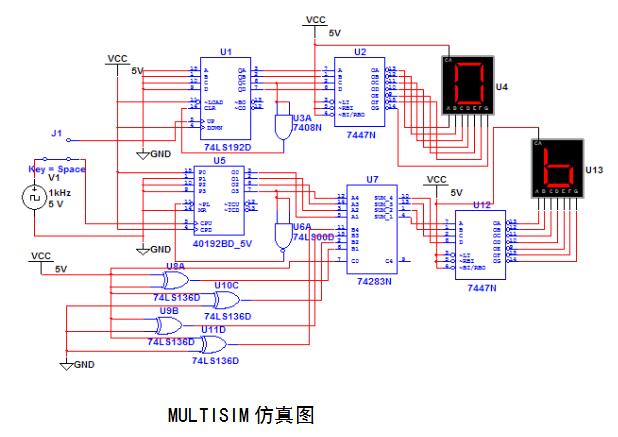

在本課程設計中,主要用到了74LS192計數器、7447譯碼器、74LS00與非門、7408與門、74LS136異或門、74283加法器、七段數碼顯示器和一個單刀雙擲開關等元器件。

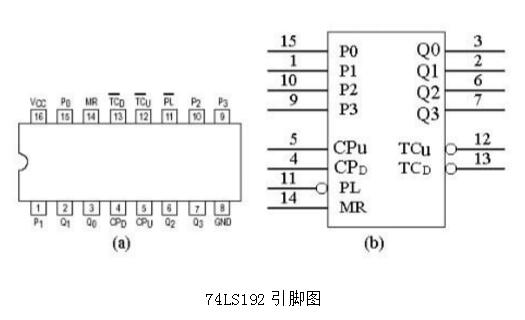

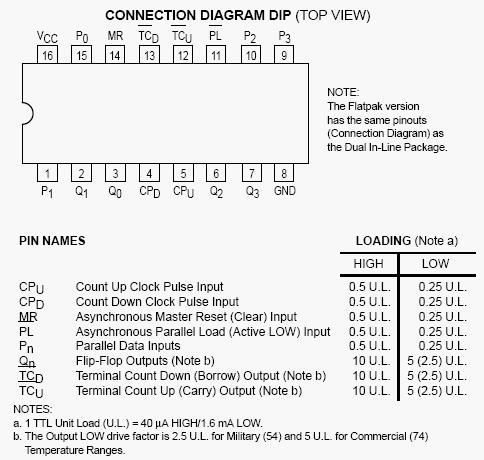

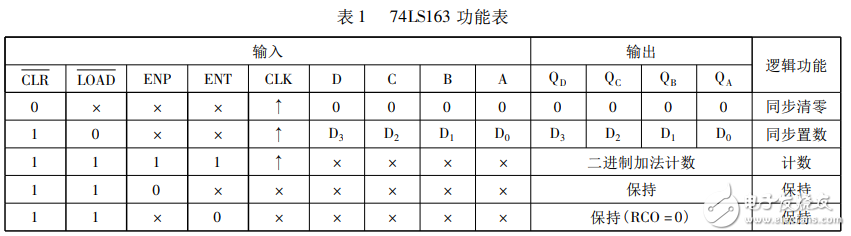

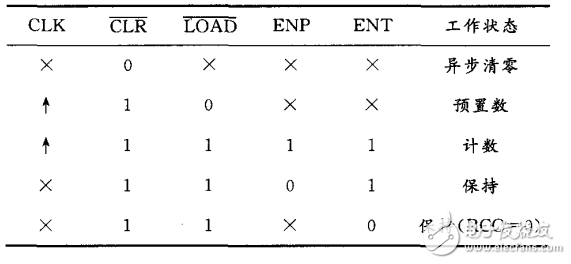

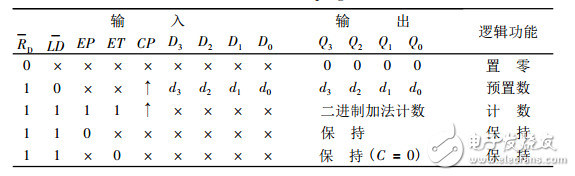

一、十進制同步可逆計數器74LS192 功能如下:

1、異步清零。74LS192的輸入端異步清零信號CR,高電平有效。僅當CR=1時,計數器輸出清零,與其他控制狀態無關。

2、異步置數控制。LD非為異步置數控制端,低電平有效。當CR=0,LD非=0時,D1D2D3D4被置數,不受CP控制。

3、加法計數器,當CR和LD非均無有效輸入時,即當CR=0、LD非=1,而減數計數器輸入端CPd為高電平,計數脈沖從加法計數端CPu輸入時,進行加法計數;當CPd和CPu條件互換時,則進行減法計數。 4. 保持。當CR=0、LD非=1(無有效輸入),且當CRd=CPu=1時,計數器處于保持狀態。

5、進行加計數,并在Q3、Q0均為1、CPu=0時,即在計數狀態為1001時,給出一進位信號。進行減計數,當Q3Q2Q1Q0=0000,且CPd=0時,BO非給出一錯位信號。這就是十進制的技術規律。

在設計過程中,我主要利用74LS192的計數功能,通過置數法和清零法將其改造為一個4進制計數器和一個7進制計數器。

二、顯示譯碼器

七段數碼顯示器

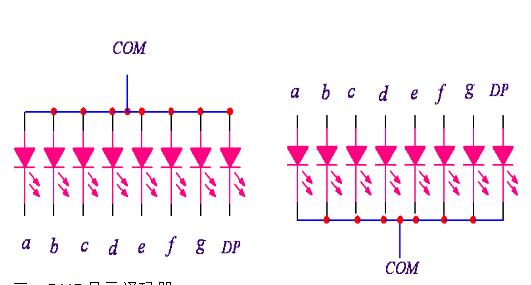

七段式數碼顯示器是目前使用最廣泛的一種數碼顯示器。這種數碼顯示器有分布在同一平面的七段可發光的線段組成,可用來顯示數字、文字、符號。最常用的七段數碼顯示器有半導體數碼管和液晶顯示器兩種。根據發光二極管的連接形式不同,分為共陰極顯示器和共陽極顯示器(如圖)。共陰極顯示器將七個發光二極管的陰極連接在一起,作為公共端。在電路中,將公共端接于低電平,將某段二極管的陽極為高電平時,相應段發光。共陽極的顯示方式和共陰極相反。

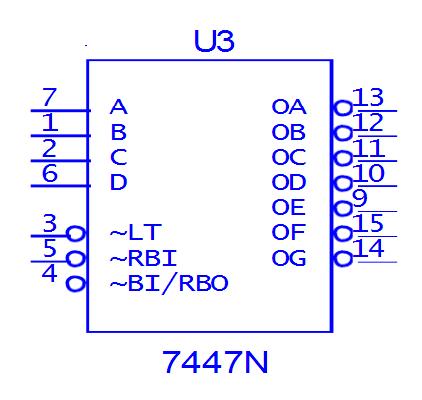

三、7447顯示譯碼器

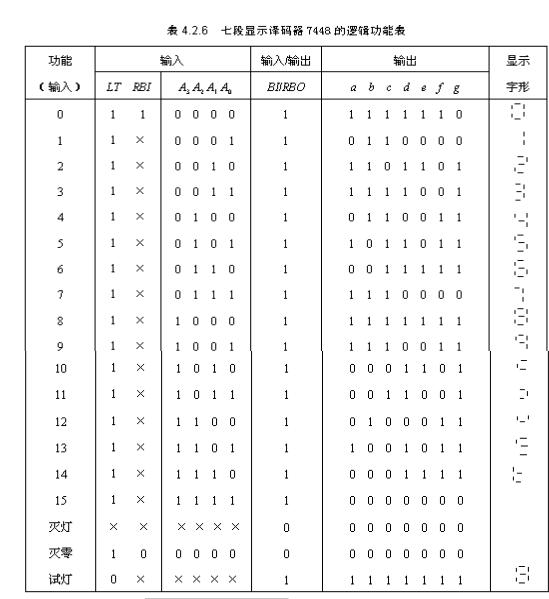

七段顯示器譯碼器把輸入的BCD碼,翻譯成驅動七段LED數碼管各對應段所需的電平。七段顯示譯碼器7447是一種與共陰極數字顯示器配合使用的集成譯碼器。它用于對十進制數的8421BCD碼進行譯碼,以驅動七段顯示器顯示十進制數字。其輸入為8421BCD碼,輸出高電平有效,可直接驅動陰極顯示器,其功能表和7448的功能表一樣如圖所示,表中10~15六個狀態一般不用。除了譯碼輸入、輸出外,7447還有三個輔助控制端,以增強器件功能。

四、74283加法器

每一位的進位信號送給高位作為輸入信號,因此,任一位的加法運算必須在低一位的運算完成之后才能進行,這種進位方式成為串行進位,這種加法器的邏輯電路較為簡單。

五、電路設計及計算

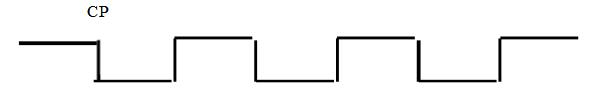

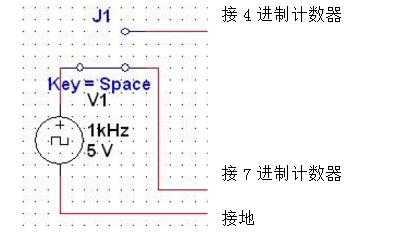

1、選擇一個方波信號發生器作為輸入信號源;

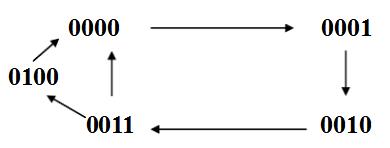

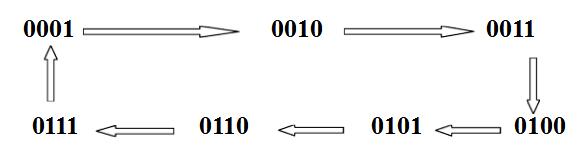

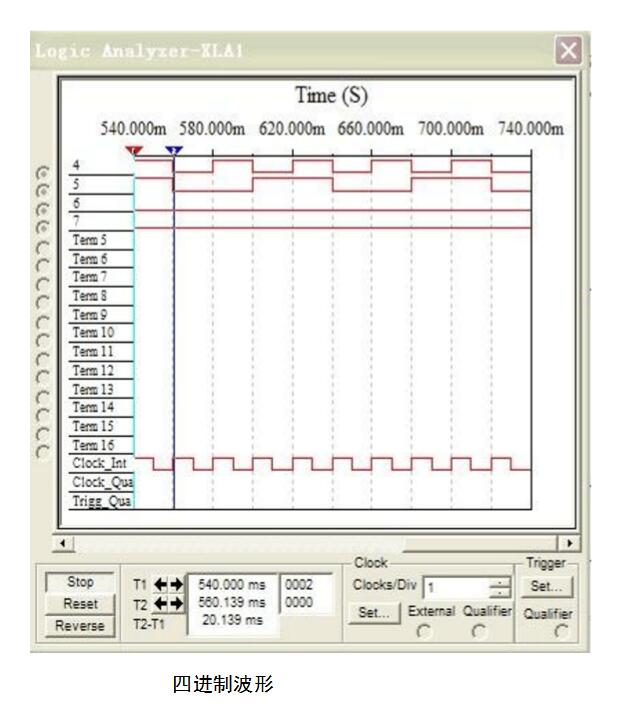

2、利用74LS192,通過清零法設計一個四進制計數器,狀態圖如下:

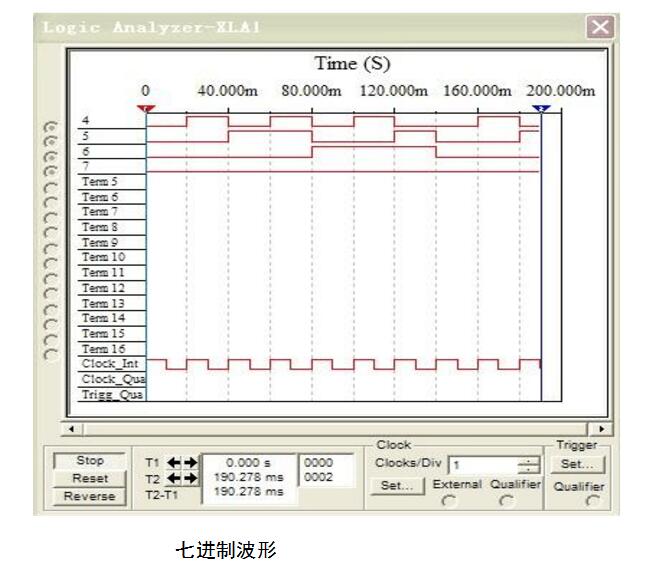

3、利用74S192通過置數法設計一個從1到7的計數器,狀態圖如下:

然后通過減法器在每一個狀態的基礎上減去一個1,從而實現一個7進制計數器。

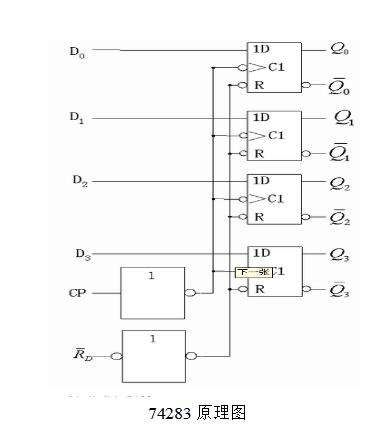

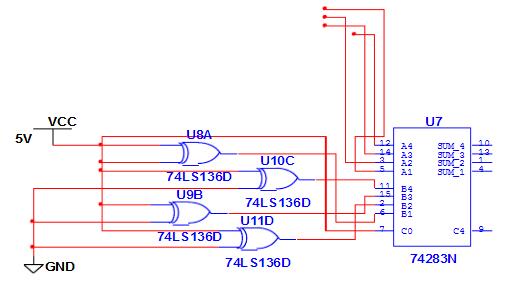

減法器電路如圖所示

4、通過一個單刀雙擲開關控制信號源,從而進行四進制和七進制之間的轉換。

5、進行四進制計數時,在74LS192后面接一個7447顯示譯碼管,將8421BCD碼轉換成十進制,最后通過一個七段顯示數碼管來顯示數據輸出狀態。

6、在進行七進制計數時,用40192進行置數法計數,預置數為0001,計數到1000后反饋到置數端,循環計數,后面接一個74238加法器構成的減法器,使輸出顯示數字在0000~0110之間計數,在經過7447譯碼管將其轉化為十進制數0~6,從而實現七進制計數器功能。

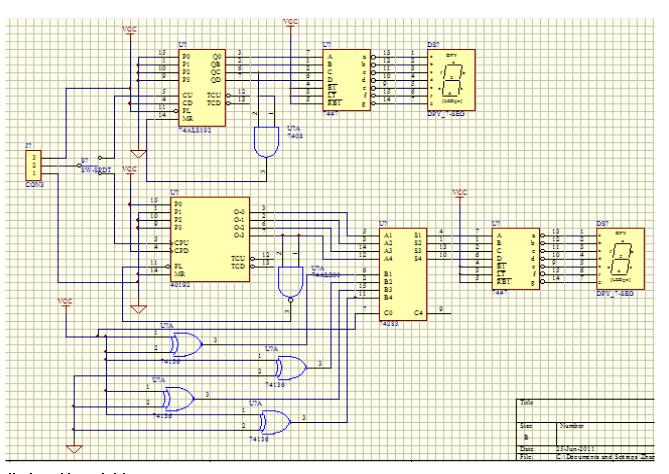

六、原理圖、仿真圖及結果分析、PCB版圖

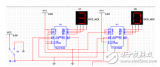

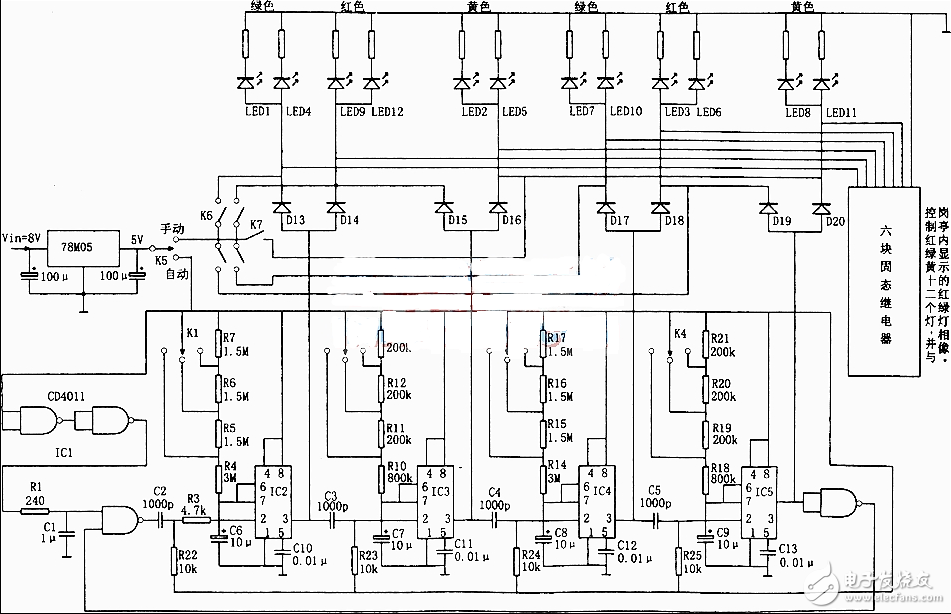

原理圖如下所示:

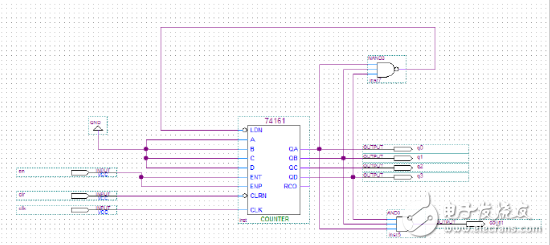

仿真及結果分析

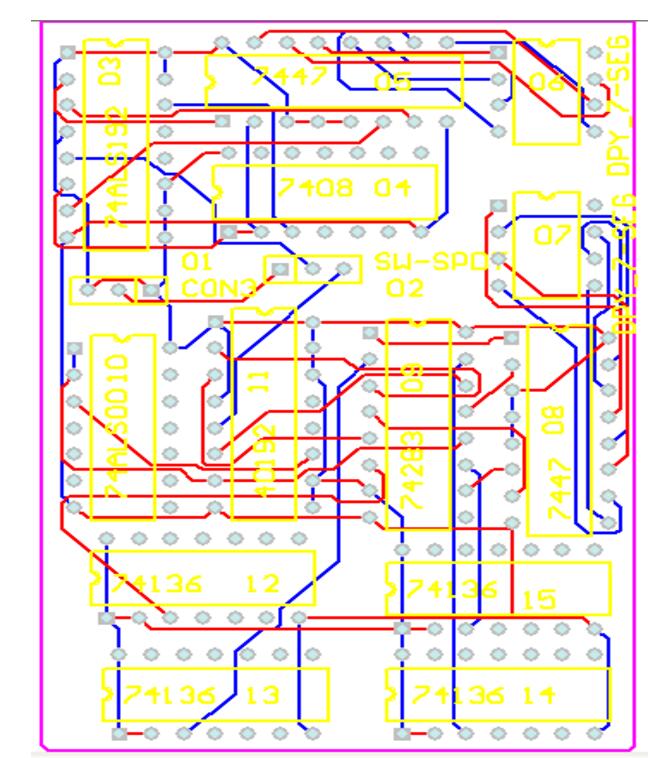

七、PCB板排布

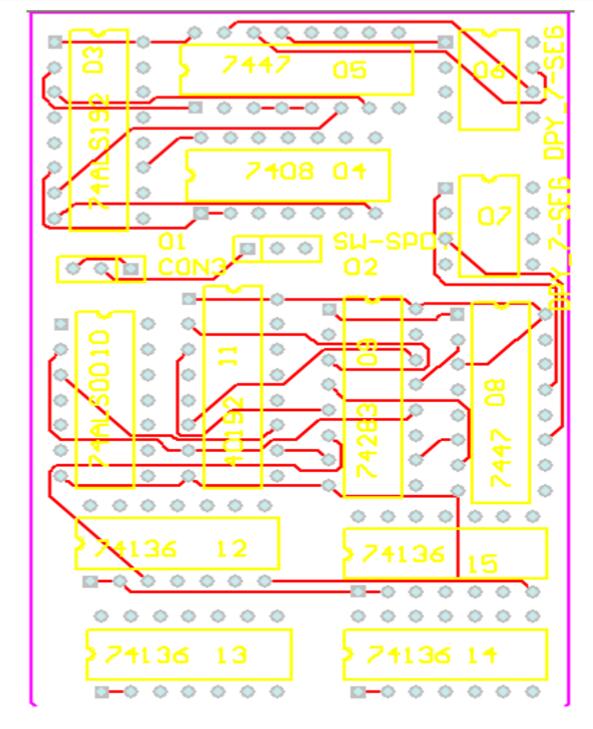

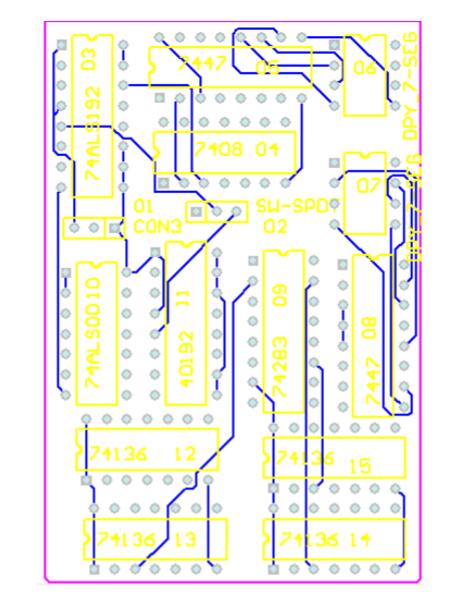

1、PCB原理圖如下

pcb板頂層

PCB板底層

電子發燒友App

電子發燒友App

評論