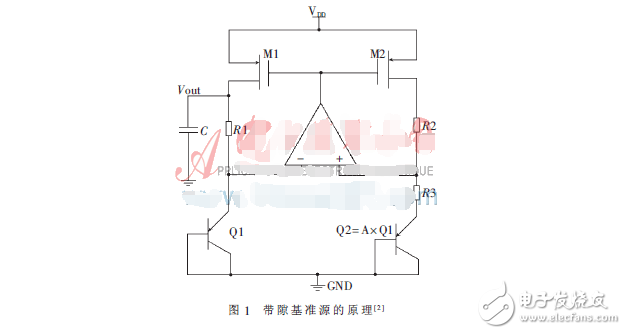

帶隙基準電壓源的目的是產生一個對溫度變化保持恒定的量,由于雙極型晶體管的基極電壓VBE,其溫度系數在室溫(300 K)時大約為-2.2 mV/K

2011-11-23 09:19:32 3218

3218

大家有誰設計過40v的電壓基準源提供點幫助吧先謝謝了在這里

2013-12-10 19:19:40

附件基準電壓源 電流檢測和電流源.rar1.0 MB

2018-10-17 15:23:22

7 顯示 ADR4312.5 V 基準電壓源的典型噪聲與頻率關系曲線圖。 圖 7. 帶補償網絡的 ADR431 噪聲曲線 ADR435 補償其內部運算放大器,驅動大容性負載并避免噪聲峰化,使其非常

2020-04-14 07:00:00

高分辨率、逐次逼近型 ADC 的整體精度取決于精度、穩定性和其基準電壓源的驅動能力。ADC基準電壓輸入端的開關電容具有動態負載,因此基準電壓源電路必須能夠處理與時間和吞吐速率相關的電流。某些ADC

2021-03-16 12:04:19

本帖最后由 laisheng 于 2016-1-25 11:14 編輯

雖然每種模擬IC類型都有必須優化的特定參數,但這里將探討基準電壓源——可產生穩定、精確直流電壓的器件,該器件決定了

2016-01-25 10:58:27

概述:REF191是一款精密帶隙基準電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調高度穩定的薄膜電阻,以實現非常低的溫度系數和較高的初始精度。REF191采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-13 06:00:16

概述:REF198是一款精密帶隙基準電壓源芯片,它采用專利的溫度漂移曲率校正電路,激光微調高度穩定的薄膜電阻,以實現非常低的溫度系數和較高的初始精度。REF198采用SOIC、TSSOP及DIP8腳封裝工藝;...

2021-04-14 07:34:35

帶隙基準是什么?帶隙基準的功能工作原理是什么?帶隙基準的結構是由哪些部分組成的?

2021-06-22 08:14:04

采用1830工藝設計預設值電流I=10uA,由公式過驅動電壓0.2V,得到PMOS寬長比12.5/1由公式過驅動電壓0.2V,得到NM8寬長比2.8/1設置K=4,NM7寬長比4×2.8/1由公式

2021-12-30 08:15:23

這是帶隙基準仿真波形。這款帶隙基準用于RFID芯片中,當整流出來為周期性波動電壓時,供給帶隙后,帶隙輸出也會發生周期性抖動。在單仿帶隙時,DC仿真和瞬態仿真都沒有問題,可以穩定輸出。但是如果瞬態加

2021-06-25 07:27:47

標準的帶隙基準,輸出電壓約為1.2V,10ppm左右。設計好,接入電路中,瞬態仿真,輸出電壓波形為以1.2V為直流,類似100MHz頻率的20mv峰值正弦波做周期等幅振蕩,可能的原因是什么。

2011-12-07 14:43:44

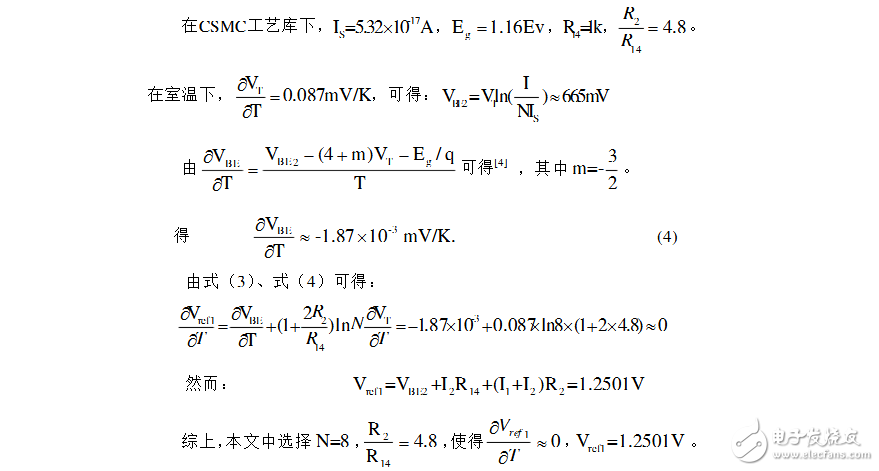

基準電壓源是工藝、電源電壓、溫度變化時能夠提供穩定輸出電壓的電路。基準電壓源廣泛應用于數據轉換器、智能傳感器、電源轉換器等電路。

基準電壓源設計的要點是精度高,溫度漂移小,帶隙基準電壓源利用硅的帶隙

2023-09-08 17:56:48

本帖最后由 萆嶶锝承鍩じ☆ve 于 2018-4-8 18:13 編輯

電壓基準芯片的分類 根據內部基準電壓產生結構不同,電壓基準分為:帶隙電壓基準和穩壓管電壓基準兩類。穩壓管電壓基準的基準

2018-04-08 17:19:22

你知道么,LT1461 和 LT1790 微功率低壓降帶隙電壓基準的過人之處不僅在于溫度系數 (TC) 和準確度,還在于長期漂移和遲滯(因為溫度的周期性變化而引起的輸出電壓漂移)。有時被其他制造商所

2019-08-02 06:36:09

操作理論 AD1580使用帶隙概念來產生一個穩定的、低溫度系數的電壓基準,適用于高精度數據采集組件和系統。該器件利用了硅晶體管基極發射極電壓在正向偏置工作區的基本物理特性。所有此類晶體管的溫度系數

2020-07-15 10:06:46

AD5676R是自帶內部基準電壓源的。但是我使用時,18腳沒有基準電壓源輸出,造成Vout都沒有輸出。

看了評估版原理圖后,在AD5676R的18腳外接+2.5V基準源后,則8路Vout才正常輸出了。

請問這是什么原因?電路連接: Vdd=+5V,Vlogic=3.3V。

2023-12-06 08:24:55

請教大家, N76E616 內部帶隙電壓的存儲參數如何讀取?

2023-06-25 11:04:36

1. 看了V1.04的芯片手冊,但是沒看到 芯片內部帶隙電壓的出廠校準值 的存儲地址, 請問如何讀出帶隙電壓值?

2. 我將芯片內存存儲器都用作APROM區,請問我將最后1K區域當做EEPROM來存儲參數,要如何操作? 這個內部APROM區域大概可以重復寫入多少次內?

2023-06-27 06:20:00

最近diy制作一個USB電源電流表,使用的N76E003單片機,液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-06-16 07:32:22

穩壓器、射頻電路、高精度A/D和D/A轉換器等多種集成電路中。隨著大規模集成電路的日益復雜和精密,亦對帶隙基準電壓的溫度穩定性提出了更高的要求。傳統的帶系基準電壓源只能產生固定的近似1.2 V的電壓

2019-07-12 07:36:42

基準電壓源有很多形式并提供不同的特性,但歸根結底,精度和穩定性是基準電壓源最重要的特性,因為其主要作用是提供一個已知輸出電壓。相對于該已知值的變化是誤差。為什么需要基準電壓源?

2019-07-30 07:40:43

什么是基準電壓源?看到了論壇有電壓源的貼子,想問下什么是基準電壓源?求大蝦指教啊

2011-12-27 13:48:15

傳統帶隙基準源有哪些基本原理?什么樣的基準源電壓才能滿足普通應用要求?

2021-04-07 06:52:08

如圖所示,

問題1中文數據手冊第一頁框圖中的Band Gap REF是指芯片的4.096V內置基準參考原嗎?

問題2.中文數據手冊第4頁,內部基準電壓源參數描述中,REFIN輸出電壓2.3V怎么理解?為什么是該電壓值,而不是4.096V呢。根據注釋6內容“內部帶隙基準電壓源的輸出”。

2023-12-04 08:26:10

看了關于能帶隙基準源的的介紹,其原理是利用了正溫度系數的電壓產生器和具有負溫度系數的電壓,從而得到具有零溫度系數的基準電壓。

第一張圖是基本原理圖,用左邊電流控制右邊電流,但是書上說左右兩個晶體管

2024-01-27 11:56:26

使用具有1.2外部帶隙基準的TC7116模數轉換器的典型應用(VIN- 與通用相連)

2019-07-26 08:35:49

具有低漂移滿量程調整的LT1021BCH-5 CMOS DAC參考的典型應用。 LT1021是一款精密基準電壓源,具有超低漂移和低噪聲特性,極佳的長期穩定性以及對輸入電壓變化的幾乎完全抗擾度。參考輸出的源電流和吸收電流均高達10mA

2020-04-02 10:00:45

M0518 ADC的內部帶隙電壓是指什么?

2018-10-16 09:53:21

大家好,我有一個問題,配置PIC18F85 J94ADC。在第22.3.2頁中,從PIC18F97 J95家庭數據表中得知,內部帶隙基準電壓可用于ADC正基準電壓。然而,在寄存器描述中沒有提到這樣

2019-01-29 06:04:01

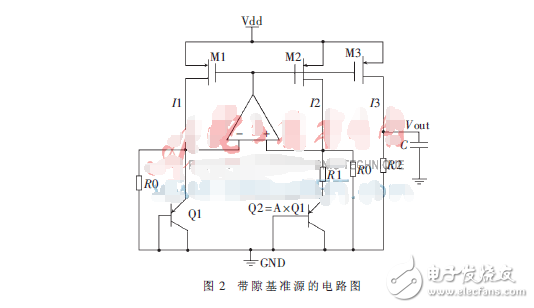

基準;LDO穩壓器;溫度系數;電源抑制比;運算放大器 CMOS帶隙基準電壓源不但能夠提供系統要求的基準電壓或電流,而且具有功耗很小、高集成度和設計簡便等優點,廣泛應用于模擬集成電路和混合集成電路中。帶隙

2018-10-09 14:42:54

帶曲率補償的帶隙基準源的原理是什么?它與傳統帶隙基準源相比有何不同?

2021-04-09 06:35:43

如果我們可以確定帶隙電壓和對應的ADC原始數據那么我們就可以通過比例運算知道VCC,因為滿量程對應的就是VCC,也就是0x0FFF對應VCC

即VCC:0xFFF=帶隙電壓:帶隙電壓ADC

2023-06-25 08:18:31

如何去選擇基準電壓源?為什么參數差的基準反而可能更好?

2021-05-08 07:39:12

最近在做帶隙基準源,用到AMP鉗位電壓,使倆點電壓一致,拉雜為沒講用到的AMP要有什么要求?但看到資料的電路基本都是單級AMP,想問下大大們,這個AMP鉗位電壓原理就是虛短虛斷么?(如果是要求增益應該很大啊),還有那些要求?第一次發帖,小弟先謝了。

2022-06-15 10:26:32

帶隙基準源原理是什么?雙極帶隙基準電路的實際電路結構是怎樣構成的?怎樣對雙極帶隙基準電路進行仿真測試?

2021-04-21 06:20:19

帶隙基準電壓源工作原理是什么?一種低溫漂輸出可調帶隙基準電壓源的設計

2021-05-08 06:38:57

1,通過MS51FB9AE帶隙電壓(Band-gap)能反推出電源電壓,2,MS51FB9AE帶隙電壓(Band-gap)比較低,1.17V ~ 1.27內3,如果我要偵測比較低的電壓(如50mV

2022-05-11 14:31:55

電源電壓變化時,帶隙基準的輸出發生跳變,怎么減小帶隙基準的過沖?謝謝

2021-06-24 06:46:07

問題。設計了兩款電路:一款是高精度CMOS帶隙基準電壓源電路;另一款為采用頻率抖動技術的RC振蕩器電路。回帖本帖查看隱藏下載地址:[hide][/hide]

2022-07-04 14:58:24

精密基準電壓源芯片中的“初始電壓精度”是什么意思?例如ADR06的初始精度:±0.1%

2023-11-23 06:13:31

噪聲貢獻。圖7顯示ADR431 2.5 V基準電壓源的典型噪聲與頻率關系曲線圖。 圖7. 帶補償網絡的ADR431噪聲曲線 ADR435補償其內部運算放大器,驅動大容性負載并避免噪聲峰化,使其

2018-09-27 10:57:26

電路的總噪聲貢獻。圖7顯示ADR431 2.5 V基準電壓源的典型噪聲與頻率關系曲線圖。 圖7. 帶補償網絡的ADR431噪聲曲線 ADR435補償其內部運算放大器,驅動大容性負載并避免噪聲峰化

2018-09-27 10:29:41

最近diy制作一個USB電源電流表,使用的N76E003單片機,液晶屏顯示部分程序,也弄好了,就差adc采樣了,想利用內部帶隙電壓計算外部電壓值,不知道怎么計算,讀取UID最后兩個字,值為1663

2023-08-30 06:43:07

什么是帶隙電壓?

2020-12-23 07:27:58

如何實現低電壓帶隙基準電壓源的設計?傳統帶隙基準電壓源的工作原理是什么?低電源帶隙基準電壓源的工作原理是什么?

2021-04-20 06:12:32

如何讀取實際N76E003帶隙電壓?

2020-12-22 06:30:34

各位大神,請問有沒有做過cadence的CMOS帶隙基準電路設計,或者CMOS四運算放大器設計(LM324),求各位幫幫忙,我快山窮水盡了

2020-05-17 23:32:07

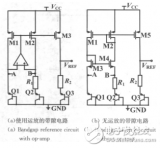

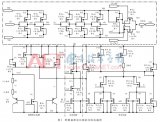

提高電源管理芯片精度和抗電磁干擾性能,結合降低電源待機功耗問題,設計了兩款電路:一款為高精度CMOS帶隙基準電壓源電路。該電路能夠為開關電源芯片提供高精度高穩定的基準電壓,設計電壓值為1.25V.仿真

2020-07-23 15:04:30

選擇最佳的電壓基準源

2012-08-14 15:02:51

公司用LM4040C25做模擬電壓采集基準源(電壓采集電路如下),在按DO-160G做CS/RS時,在200-300MHz時,電壓采集值跳動比較厲害(試驗時已測基準電源確實跳動了)。能不能換一個基準源,但換一個電壓基準源,會不會產生同樣的問題,請問大俠們有什么解決方案?

2016-12-15 14:37:00

本文通過結合LDO與Brokaw基準核心,設計出了高PSR的帶隙基準,此帶隙基準輸出的1.186 V電壓的低頻PSR為-145 dB,最高PSR為-36 dB,溫漂可以達到7.5 ppm,適用于

2018-10-10 16:52:05

,溫度穩定性和精度之間關系到整個電路的精確度和性能。 當今設計的基準電壓源大多數采用BJT帶隙基準電壓源結構,以及利用MOS晶體管的亞閾特性產生基準電壓源;然而,隨著深亞微米CMOS工藝的發展,尺寸按

2018-11-30 16:38:24

),沒有加電容,就參照上面的電路設計了。讓我們再進一步的看一下REF50XX系列bandgap基準源的內部,如下圖,芯片內部有一個1.2V的帶隙基準,和一個用于設置精確輸出電壓的放大器。這兩個就是基準

2019-06-11 06:59:08

高級基準電壓Vbandgap IC設計:在本文中,主要討論在CMOS 技術中基準產生的設計著重于公認的“帶隙”技術,即是與電壓,溫度變化無關的基準電壓。[關鍵詞]電壓基準,電流基

2009-11-01 14:35:44 34

34 本文提出了一種結構簡單高電源抑制比的CMOS 帶隙基準電壓源,供電電源3.3V。采用CSMC 0.5um CMOS 工藝。Spectre 仿真結果表明,基準輸出電壓在溫度為-40~+80℃時,溫度系數為45.53×10-6/

2010-01-11 14:20:43 27

27 LTC6655是一款完整的精密帶隙基準電壓源系列,提供出色的噪聲和漂移性能。此低噪聲和漂移特性非常適合儀器儀表和測試設備要求的高分辨率測量。此外,LTC6655的額定溫度范圍為–40°C至125°C

2023-06-25 10:41:49

ADR364分別是2.048 V、2.500 V、3.000 V、4.096 V、5.000 V和3.300 V精密帶隙基準電壓源,具有低功耗和高精度,采用緊湊的TSOT封裝。ADR360

2023-06-25 14:47:50

ADR365分別是2.048 V、2.500 V、3.000 V、4.096 V、5.000 V和3.300 V精密帶隙基準電壓源,具有低功耗和高精度,采用緊湊的TSOT封裝。ADR360

2023-06-25 14:50:33

ADR291和ADR292均為低噪聲、微功耗、精密基準電壓源,采用XFET?基準電壓源電路。與傳統的帶隙和嵌入式齊納二極管基準電壓源相比,全新的XFET架構在性能方面有明顯改進。具體包括:工作電流

2023-06-26 15:29:55

ADR291和ADR292均為低噪聲、微功耗、精密基準電壓源,采用XFET?基準電壓源電路。與傳統的帶隙和嵌入式齊納二極管基準電壓源相比,全新的XFET架構在性能方面有明顯改進。具體包括

2023-06-26 15:33:05

AD680是一款帶隙基準電壓源,可以利用4.5 V至36 V的輸入提供2.5 V輸出。它采用的架構使之能以極低的靜態電流工作,同時實現出色的直流特性和噪聲性能。通過對高度穩定的薄膜電阻調整,可獲得

2023-06-26 17:46:09

其它10 V基準電壓源。它采用工業標準引腳排列,因此許多系統都可以利用AD587迅速完成升級。基準電壓源設計采用嵌入式齊納方法,使噪聲和漂移均低于帶隙基準電壓源。

2023-06-26 17:55:20

其它5 V基準電壓源。它采用工業標準引腳排列,因此許多系統都可以利用AD586迅速完成升級。基準電壓源設計采用嵌入式齊納方法,使噪聲和漂移均低于帶隙基準電壓源。該

2023-06-27 09:15:51

本文提出了一種結構簡單高電源抑制比的CMOS帶隙基準電壓源,供電電源3.3V。采用CSMC 0.5um CMOS工藝。Spectre仿真結果表明,基準輸出電壓在溫度為-40~+80℃時,溫度系數為45.53×10-6/℃

2010-07-14 16:14:36 41

41 基于工作在亞閾值區的MOS器件,運用CMOS電流模基準對CATA和PTAT電流求和的思想,提出一種具有低溫漂系數、高電源抑制比(PSRR)的CMOS電壓基準源,該電路可同時提供多個輸出基準電

2010-12-30 10:25:53 26

26 低電壓高精度CMOS基準電流源設計

2011-01-24 15:10:17 95

95 基準電壓源是集成電路系統中一個非常重要的構成單元。結合近年來的設計經驗,首先給出了帶隙基準源曲率產生的主要原因,而后介紹了在高性能CMOS 帶隙基準電壓源中所廣泛采用的幾種

2011-05-25 14:52:44 34

34 基準電壓源是集成電路系統中一個非常重要的構成單元。結合近年來的設計經驗,首先給出了帶隙基準源曲率產生的主要原因,而后介紹了在高性能CMOS 帶隙基準電壓源中所廣泛采用的幾種

2011-09-27 14:30:52 58

58 在傳統帶隙基準電壓源電路結構的基礎上,通過在運放中引入增益提高級,實現了一種用于音頻-A/D轉換器的CMOS帶隙電壓基準源。在一階溫度補償下實現了較高的電源抑制比(PSRR)和較

2012-10-10 14:49:50 43

43 介紹一種基于CSMC0.5 m工藝的低溫漂高電源抑制比帶隙基準電路。本文在原有Banba帶隙基準電路的基礎上,通過采用共源共柵電流鏡結構和引入負反饋環路的方法,大大提高了整體電路的

2013-05-27 16:29:08 71

71 2015-08-24 19:29:33 20

20 低溫漂系數共源共柵CMOS帶隙基準電壓源_鄧玉斌

2017-01-08 10:24:07 5

5 本文為大家介紹一個cmos無運放帶隙基準源電路。

2018-01-11 16:52:50 14756

14756

本文根據基準源的精度必須好于DAC設計精度指標。利用負反饋和基本電流鏡等原理,合理設計電路的情況下得到了穩定的PTAT電流,并根據帶隙基準電壓源的設計原理得到一個高精度和快速啟動的CMOS帶隙基準

2018-03-05 10:45:23 8126

8126

電子發燒友App

電子發燒友App

評論