主要術語摘要:

* EDA(電子設計自動化):Electronic Design Automation

* ISP(在系統可編程):In System Programmable

* PAL(可編程陣列邏輯):Programmable Array Logic

* GAL(通用陣列邏輯):Generic Array Logic

* PLD(可編程邏輯器件):Programmable Logical Device

* EPLD(可擦除/電擦除PLD):Erasable/Electronic Programmable Logical

Device

* CPLD(復雜可編程邏輯器件):Complex Programmable Logical Device

* FPGA(現場可編程門陣列):Field Programmable Gates Array

* PLD(可編程邏輯器件):Programmable Logical Device

* ASIC(專用集成電路):Application Specific Integrated Circuits

* JTAG(邊界掃描測試技術):Join Test Action Group

*VHDL(硬件描述語言):Very high speed IC Hardware Description Language

* CAD(計算機輔助設計):Computer Assist Design

* CAE(計算機輔助工程設計):Computer Assist Engineering

* SOC(片上系統):System On a Chip

電子設計自動化(EDA)技術是以計算機科學和微電子技術發展為先導,它

匯集了計算機圖形學、拓撲邏輯學、微電子工藝與結構、計算數學等多種計算機

應用學科最新成果的先進技術,它是在先進的計算機工作平臺上開發出來的一整

套電子系統設計的軟件工具。

EDA 技術伴隨著計算機、集成電路、電子系統設計的發展,經歷了計算機

輔助設計CAD、計算機輔助工程設計CAE 和電子設計自動化EDA 三個發展過

程。EDA 軟件工具種類繁多,如:Smartork、Orcad、Tango、Protel、Workbench

(multsim)、Pspice 及各大可編程器件廠商提供的專用開發軟件,如:Altera 公司提供的MAX+plusⅡ、Lattice 公司提供的ispDesignExpert /PAC-Designer、Xilinx

公司提供的Foudation Series/webpack 等,本書將重點介紹Altera 公司的可編程器

件及其開發工具。

隨著電子設計自動化(EDA)技術的不斷發展,其含義也不斷發生變化,早期的

電子設計自動化多指類似Protel 電路版圖的設計自動化概念,這種概念僅限于電

路元器件與元器件之間即芯片外設計自動化,隨著微電子技術的不斷發展,當今

的EDA 技術更多的是指可編程邏輯器件的設計技術,即芯片內的電路設計自動

化。也就是說,開發人員完全可以通過自己的電路設計來定制其芯片內部的電路

功能,使之成為設計者自己的專用集成電路(即ASIC)芯片,這就是我們今天

所說的的EDA 技術——用戶可編程邏輯器件(PLD)技術。其應用也無處不在,

從簡單的邏輯電路、時序電路設計到復雜的數字系統設計均能得心應手,在通信

領域(軟件無線電),在數字信號處理(DSP)領域、在嵌入式/片上系統(SOC)

及各種IP 內核等諸多領域早已廣泛應用,如果說原來的Tango(Protel)的問世

在電子設計領域是一次革命的話,那么今天的EDA(CPLD/FPGA)技術稱得上

是電子設計領域的第二次革命。

隨著可編程器件PLD 技術的不斷發展和崛起,其功能之卓越和先進已經令當今

的電子工程師們贊嘆不已,除了它設計靈活、仿真調試方便、體積小、容量大、

I/O 口豐富、成本低廉、易編程和加密等優點外,更突出的特點是其芯片的在系

統可編程技術。也就是說它不但具有可編程和可再反復編程的能力,而且只要把

器件插在用戶自己設計的目標系統內或線路板上,可以重新構造其設計邏輯而對

器件進行編程或者反復編程,這種技術被稱為在系統可編程技術,簡稱ISP 技術。

由于ISP 技術的應用,打破了產品開發時必須先編程后裝配的慣例,而可以先裝

配后編程,成為產品后還可以在系統內反復編程和修改,ISP 技術使得系統內硬

件的功能象軟件一樣被編程配置,使系統的升級和維護變得更容易和方便。可以

說可編程器件真正做到了硬件的“軟件化”自動設計,這就是當今的EDA 電子設

計自動化技術。可以不夸張地說由于可編程器件的出現,傳統的(數字)電路設

計方法和過程得到了一次革命和飛越。

由于ISP-PLD 器件的寫入、擦除控制電路和高壓脈沖發生電路集成在PLD 芯

片內部,所以不需要編程器,直接利用器件的工作電壓,在器件安裝到系統板上后,不需要將器件從電路板上拔下來,可直接對器件進行編程,并可改變其內部

的設計邏輯,滿足其設計需要。

可編程器件PLD 可分為數字可編程器件和模擬可編程器件兩類。前者之技術發

展已經相當成熟,在大量的電子產品中早已得到了實際應用;后者相對來說發展

要晚一些,其現有的芯片功能也比較單一。數字可編程邏輯器件按其密度可分為

低密度PLD 和高密度PLD 兩種,低密度PLD 器件如早期的PAL、GAL 等,它

們的編程都需要專用的編程器,屬半定制ASIC 器件;高密度PLD 又稱復雜可

編程邏輯器件,如市場上十分流行的CPLD、FPGA 器件,它們屬于全定制ASIC

芯片,編程時僅需以JTAG 方式的下載電纜與計算機并口相連即可。此書將主要

以數字可編程邏輯器件(CPLD、FPGA)之設計與應用進行系統描述,有關模

擬可編程器件的說明請參考本公司的其他書物。

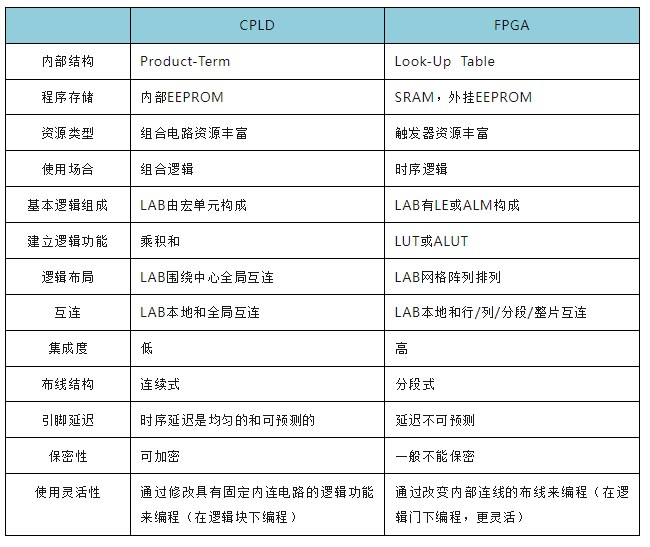

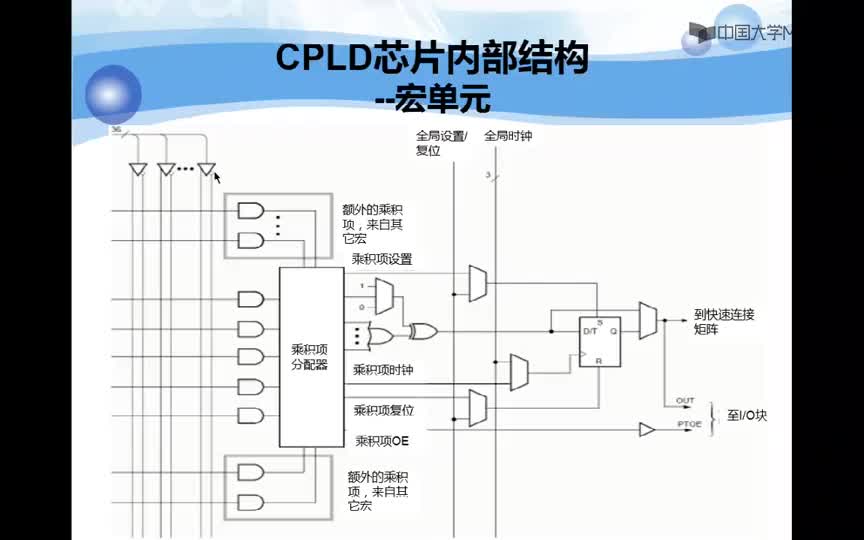

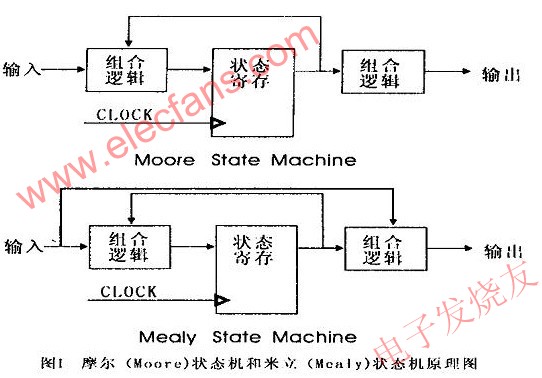

CPLD/FPGA 同屬于高密度用戶可編邏輯程器件,其芯片門數(容量)等級從幾

千門~幾萬門、幾十萬門到幾百萬門以上不等,適合于時序、組合邏輯電路應用

場合,它可以替代幾十甚至上百塊通用IC 芯片,實際上這樣的CPLD/FPGA 就

是一個子系統部件。在很大程度上他們具有類似之處,比如其電路設計方法都一

樣。相比而言,CPLD 適合于做各種算法和組合邏輯電路設計,而FPGA 更適合

完成時序比較復雜的邏輯電路。由于FPGA 芯片采用RAM 結構,失電以后其內

部程序將丟失,在形成產品時一般都和其專用程序存儲器配合使用,其芯片內部

的電路文件(程序)可放置在磁盤上、ROM 或E2PROM 中,因而可以在FPGA

芯片及其外圍保持不動的情況下,換一塊存儲器芯片就能實現一種新的功能。電

路設計人員在使用CPLD/FPGA 器件進行電路設計時不需過多的考慮它們的區

別,因為其電路設計和仿真方法都完全一樣,不同之處在于芯片編譯或適配時生

成的下載文件不一樣而已。

可編程器件CPLD/FPGA廠商比較眾多,比較知名的如Altera、Lattice、Xilinx、

Actel 公司等,本公司推出的這套實驗系統兼容這幾家廠商的CPLD 和FPGA 芯

片。上述幾家公司推出的芯片均配有功能強大的開發軟件,不僅支持多種電路設

計方法,如電原理路圖、硬件描述語言VHDL 等,而且還支持電路仿真和時序

分析等功能,為用戶開發和調試產品提供了極大的方便。有關可編程器件設計軟

件的具體使用在實驗系統例程中將詳細介紹給讀者。

CPLD/FPGA 技術發展十分迅速,不斷有新技術和新產品問世,我們和廣大讀者一樣,也處在不斷地學習和運用當中。

電子發燒友App

電子發燒友App

評論