電平信號與電壓信號的區別 不同的電平信號怎么進行“溝通”? 電平信號與電壓信號是在電子設備中使用的兩個術語,它們描述了不同類型的信號傳輸方式。電平信號和電壓信號都是將信息轉換為可傳輸的形式,但它

2023-10-24 09:58:37 32

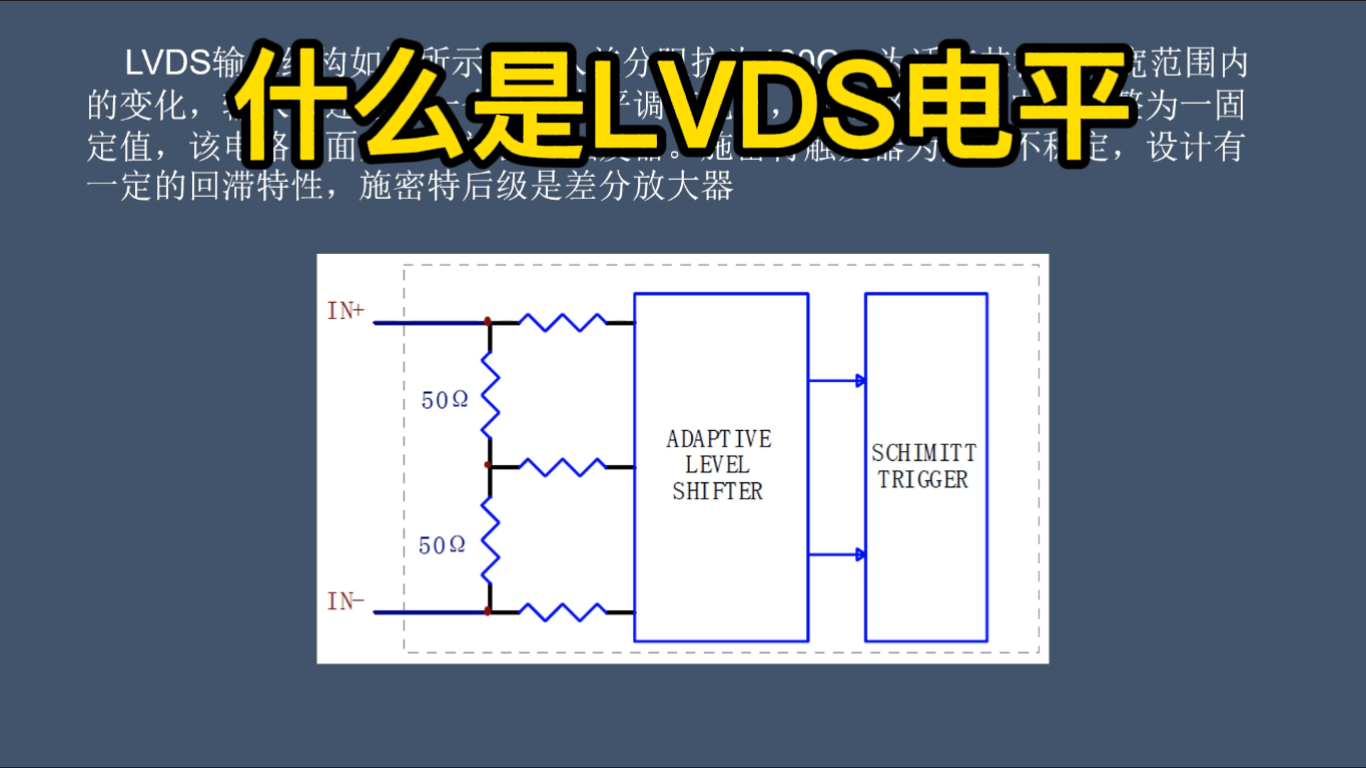

32 請教關于LVDS阻抗匹配的問題 LVDS輸出阻抗偏大會出現什么情況? LVDS(Low Voltage Differential Signaling)是差分信號傳輸技術,能夠提供較高的數據傳輸速率

2023-10-18 16:48:38 107

107 LVDS中的時鐘脈沖信號是干什么的? LVDS(Low Voltage Differential Signaling)中的時鐘脈沖信號(Clock)是用于同步數據傳輸的,是整個LVDS接口的重要

2023-10-18 15:38:20 66

66 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用差分

2023-10-18 15:38:18 70

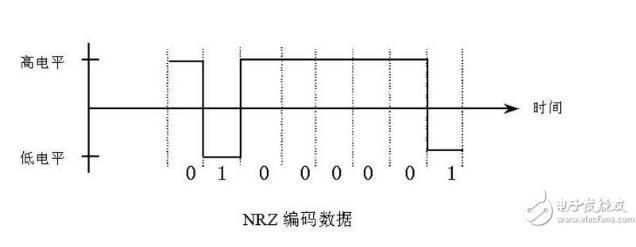

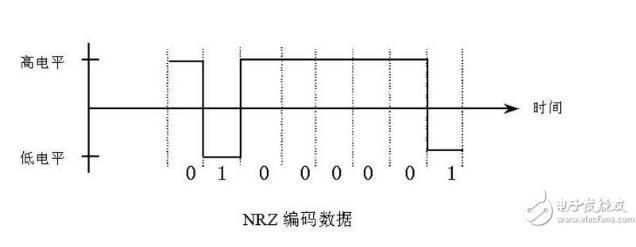

70 、降低功耗和更好的抗干擾能力。 LVDS即低壓差分信號,是一種常見的數字信號傳輸協議。在LVDS中,數據信號被編碼成高電平和低電平之間的電壓差分,以提高抗干擾能力和傳輸速度。LVDS具有較低的傳輸電壓和功耗,能夠支持高達4 Gbps的數據傳輸速度,并且傳輸距離可以達到

2023-10-18 15:38:16 189

189 LVDS傳輸的是什么信號?判斷LVDS信號正常的方法 一、LVDS傳輸的是什么信號? LVDS是一種低電壓差分信號,有兩種電壓狀態,即高電平和低電平,它類似于RS485協議。LVDS信號作為一種數字信號

2023-10-18 15:38:13 145

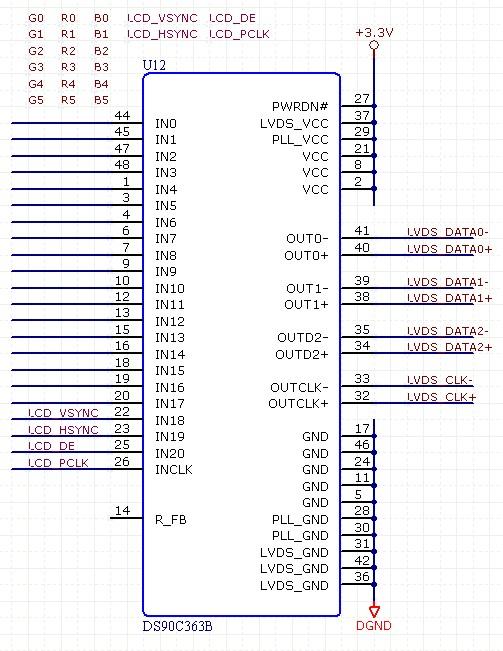

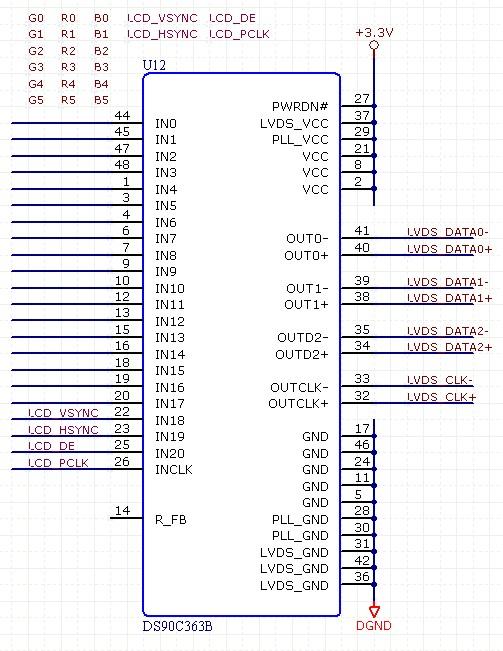

145 LVDS發送芯片的輸入信號來自主控芯片,輸入信號包含RGB數據信號、時鐘信號和控制信號三大類。

2023-10-17 17:28:13 93

93

電子發燒友網站提供《使用Pericom交換機連接LVDS信號.pdf》資料免費下載

2023-07-26 09:17:24 0

0 LVDS :低電壓差分信號(Low-Voltage Differential Signaling)是美國國家半導體(National Semiconductor, NS)于1994年提出的一種信號傳輸模式的電平標準

2023-06-25 15:02:45 1609

1609

單通道M-LVDS接收機的特性與應用 SN65MLVD2 與 SN65MLVD3 均為單通道 M-LVDS 接收機。這些器件完全符合 TIA/EIA-899 (M-LVDS

2009-10-28 14:38:59

今天聽了下公司analog designer的介紹課程,有一些LVDS在信號上的觀點非常亮,我做了點筆記,跟大家分享一下。

2023-05-25 11:28:20 865

865

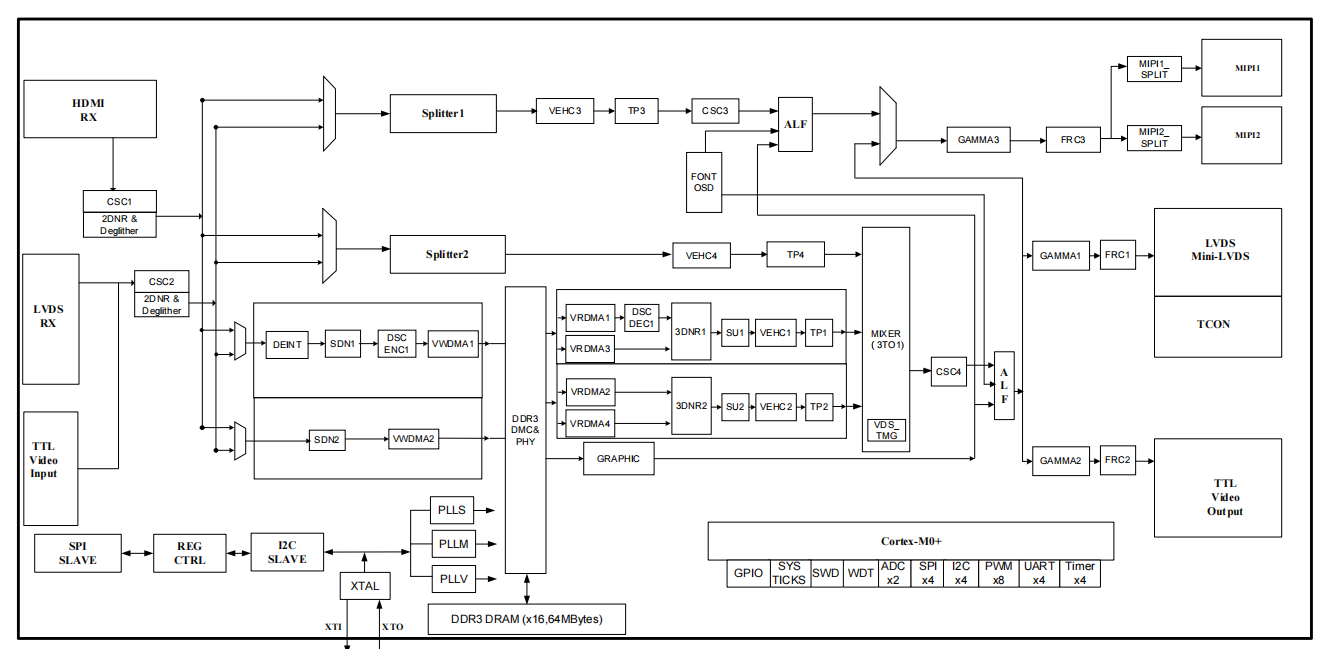

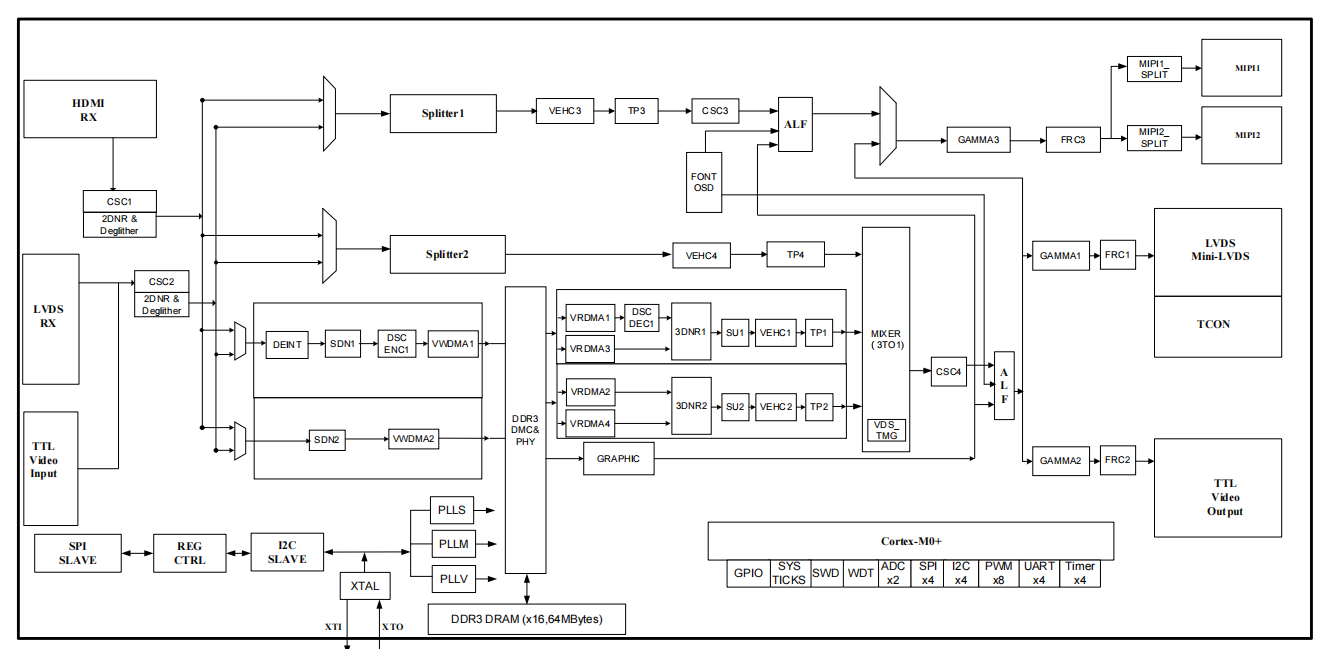

MS1861單顆芯片集成了HDMI、LVDS和數字視頻信號輸入;輸出端可以驅動MIPI(DSI-2)、

LVDS、Mini-LVDS 以及 TTL 類型 TFT-LCD 液晶顯示。可支持對輸入

2023-05-24 18:52:42 324

324

本應用筆記討論了EIA/TIA-644低壓差分信號(LVDS)標準在3G移動通信中的應用。LVDS具有低功耗和低輻射特性,非常適合WCDMA、EDGE和cdma2000?基站中的高速時鐘和信號分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中繼器和MAX9152交叉點開關。

2023-03-29 11:14:33 508

508

ANSI EIA/TIA-644 低壓差分信號 (LVDS) 標準比更傳統的 ECL、PECL 和 CML 標準提供更低的功率和更低的噪聲發射,用于高速信號分配。本應用筆記比較了這些通信標準的一些特性,并討論了LVDS標準的一些優點。

2023-03-29 11:05:07 398

398

這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數據,共18位RGB數據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 1725

1725 LVDS(Low-Voltage Differential Signaling ,低電壓差分信號)是美國國家半導體(National Semiconductor, NS,現TI)于1994年提出

2023-03-08 15:40:00 1912

1912

電平信號檢測通常可以采用比較器或者門電路實現。以下是兩種常見的方法:比較器是一種有兩個輸入端口和一個輸出端口的電路。當兩個輸入端口之間的電壓差超過比較器的閾值電壓時,輸出端口會產生一個高電平或低電平

2023-02-27 16:59:33 2750

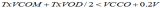

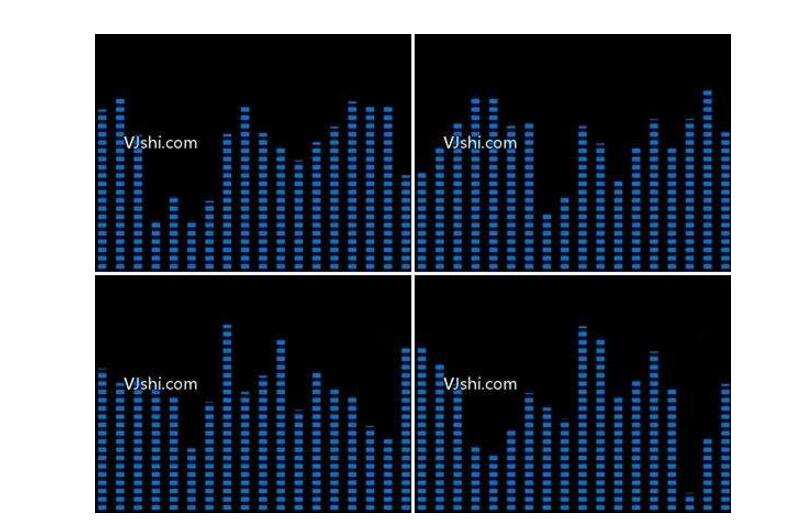

2750 很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2023-02-09 09:48:03 1149

1149 由于各種邏輯電平的輸入、輸出電平標準不一致,所需的輸入電流、輸出驅動電流也不同,為了使不同邏輯電平能夠安全、可靠地連接,邏輯電平匹配將是電路設計中必須考慮的問題。

2022-11-10 10:01:54 5794

5794 QFN64 封裝。該封裝符合 RoHS 標準,額定工作溫度范圍為 -40°C 至 +85°C。 特性: 支持 3 位最大 10dB 輸入均衡 支持 LVDS 輸出信號重驅輸入和輸出 每條數據通道 80Mb/s

2022-09-29 14:27:31 642

642 當兩個banks的I/O口作為LVDS電平時,HR banks的I/O電壓VCCO只能為2.5V,HP banks的I/O口電壓為1.8V。兩個banks支持LVDS的標準不同,HR I/O banks的I/O只能分配LVDS_25標準,HP分配為LVDS標準。

2022-06-24 11:28:04 5095

5095 GM8827C實現以7:1的壓縮比將27位CMOS/TTL信號(RGB 8位和HSYNC、VSYNC、 DE)換成串行 LVDS 輸出數據流。輸入時鐘經內部鎖相后,同頻率輸出,同時轉換為 LVDS

2021-11-30 21:06:05 7

7 很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2021-08-19 10:08:00 7290

7290

LVDS接口設計及電平轉換綜述

2021-07-31 16:34:38 14

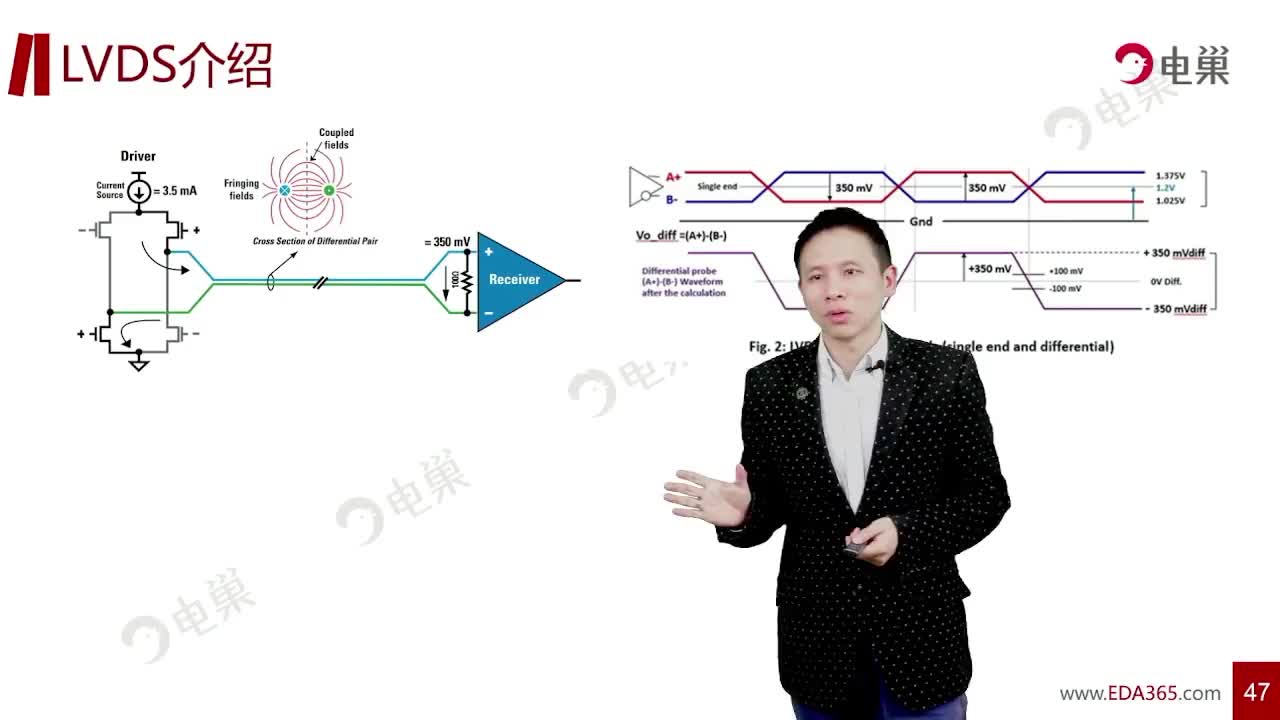

14 。這些良好特性可歸因于內部使用的電流控制或驅動器模塊的限流功能(最大3 mA)。信號差分電壓僅為 20 mV。但是,它隨后在接收器側被放大回 300 mV(差分)的邏輯電平。由此獲得的好處包括電磁干擾 (EMI) 極其低、開關速度極其快等。 LVDS接口常常與控制和調節系

2021-05-24 14:05:26 2127

2127

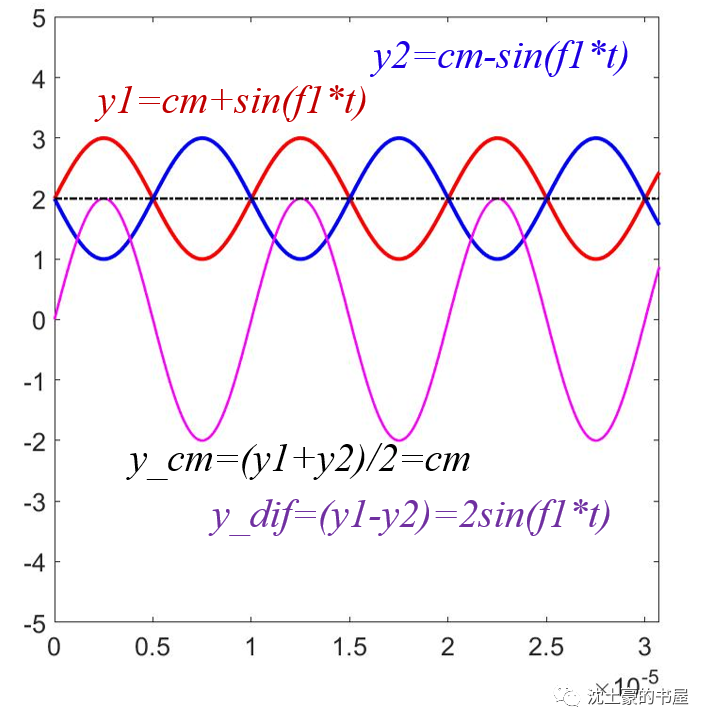

低電壓差分信號(LVDS)是一種高速點到點應用通信標準。多點LVDS( M-LVDS)則是一種面向多點應用的類似標準。LVDS和M-LVDS均使用差分信號,通過這種雙線式通信方法,接收器將根據兩個互補電信號之間的電壓差檢測數據。這樣能夠極大地改善噪聲抗擾度,并將噪聲輻射降至最低。

2021-05-24 11:46:54 18

18 電子發燒友網為你提供詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-09 08:45:44 86

86 本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。由于篇幅比較長,分為兩部分:第一部分是同種邏輯電平之間的互連,第二部分是不同種邏輯電平之間的互連。

2021-01-07 16:30:00 36

36 一般情況下,兩種不同直流電平的信號(即輸出信號的直流電平與輸入需求的直流電平相差比較大),比較提倡使用AC耦合,這樣輸出的直流電平與輸入的直流電平獨立。

2021-01-07 16:30:00 34

34 信號的邏輯電平經歷了從單端信號到差分信號、從低速信號到高速信號的發展過程。最基本的單端信號邏輯電平為CMOS、TTL,在此基礎上隨著電壓擺幅的降低,出現LVCMOS、LVTTL等邏輯電平,隨著信號速率的提升又出現ECL、PECL、LVPECL、LVDS、CML等差分信號邏輯電平。

2021-01-05 17:32:38 7

7 本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。 下面詳細介紹第二部分:不同邏輯電平之間的互連。 1、LVPECL的互連 1.1、LVPECL到CML的連接 一般情況下

2020-12-20 11:49:31 19167

19167

本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。由于篇幅比較長,分為兩部分:第一部分是同種邏輯電平之間的互連,第二部分是不同種邏輯電平之間的互連。 下面詳細介紹第一部

2020-12-20 11:39:59 34000

34000

很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電平)連接到了VCCO=2.5V或者3.3V的Bank上,于是產生了關于FPGA引腳與LVDS(以及

2020-10-10 09:25:37 9912

9912

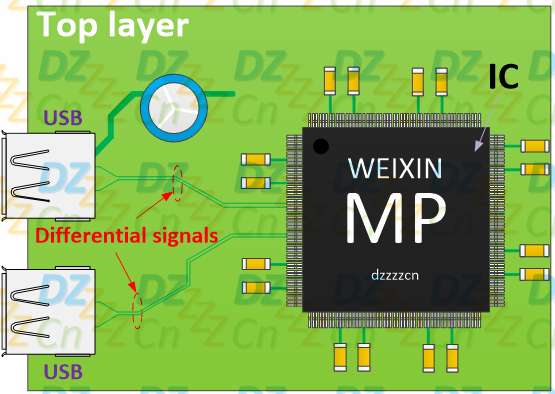

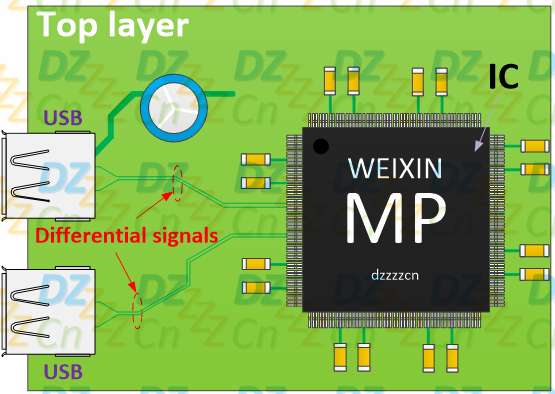

LVDS信號不僅是差分信號,而且還是高速數字信號。因此LVDS傳輸媒質不管使用的是PCB線還是電纜,都必須采取措施防止信號在媒質終端發生反射,同時應減少電磁干擾以保證信號的完整性。

2020-03-08 13:14:00 1636

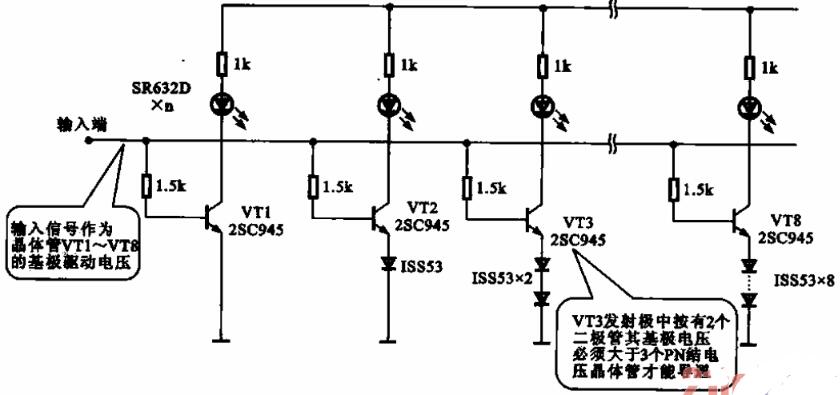

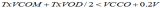

1636 所示是信號電平狀態顯示電路,例如可作音響的電平顯示,多毀發光二極管分別由多組晶體管驅動電路構成,每個驅動晶體管發射極串接的二極管數量不同,驅動晶體管對驅動信號的電平的要求不同。發射極串接的二極管越多

2020-01-24 14:47:00 4025

4025

854105是一種低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS時鐘扇出緩沖區。利用低壓差分信號(LVDS),854105提供了一種低功耗、低噪聲的解決方案,用于將時鐘信號分布在100Ω的受控阻抗上。854105接受LVCMOS/LVTTL輸入電平,并將其轉換為LVDS輸出電平。

2019-07-22 08:00:00 3

3 本文開始介紹了電平的定義與傳輸電平的分類,其次闡述了電平信號的相關概念,最后介紹了電平信號的產生。

2018-03-13 15:51:05 14891

14891

本文開始闡述了電平信號什么意思以及電平信號的產生,其次對TTL電平的相關定義進行了介紹,最后闡述了電平信號和脈沖信號區別以及闡述了電平和電壓的區別。

2018-03-13 10:02:07 65897

65897

本文主要介紹了USB轉TTL、USB轉232的區別以及各電平信號的特性分析。USB轉TTL芯片的單片機通信,直接用USB線連接即可。USB轉RS-232模塊,該模塊核心是在DB9的一端有一塊CH340或CH341電平轉換芯片,把RS-232電平轉換為USB電平。并且PC端還要安裝相應的驅動程序。

2018-01-05 14:55:29 33891

33891

本文以脈沖信號和電平信號中心,主要介紹了脈沖信號的原理以及技術標準,其次再具體的闡述了電平信號的概要。最后詳細的介紹了電平信號和脈沖信號的產生與它們兩者之間的區別。

2017-12-26 15:18:04 72370

72370 本文詳細介紹了多點LVDS特性及TI接口的選擇指南等相關知識。

2017-11-18 10:18:07 10

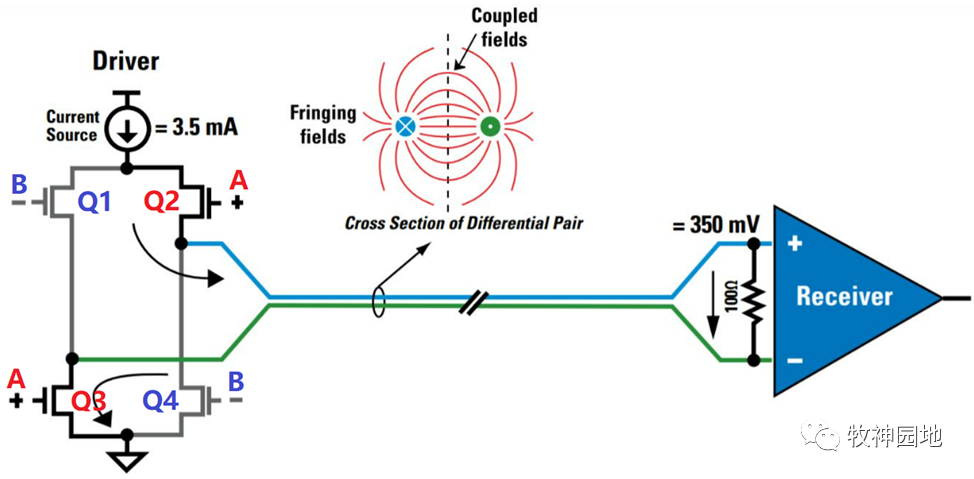

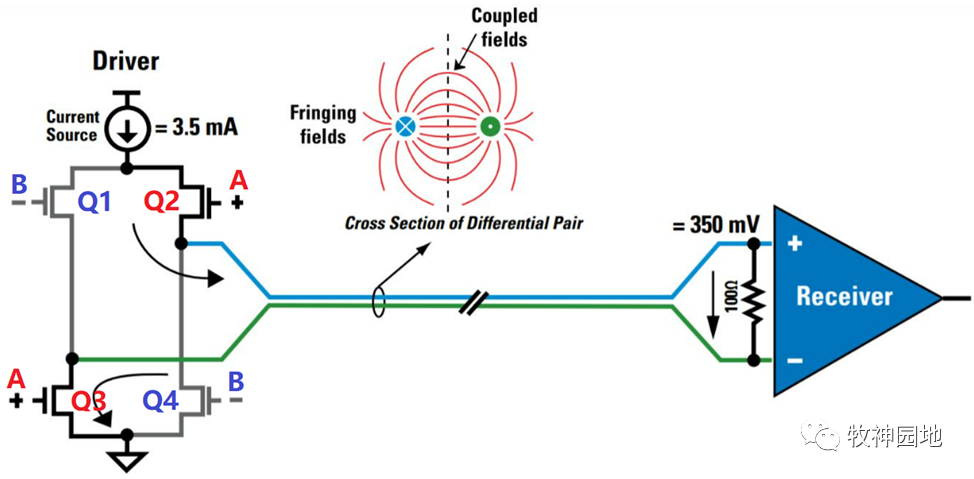

10 它差分信號標準類似,LVDS由于消除了磁場,因而比單端信號輻射的噪聲要低得多。同時外來噪聲作為共模信號耦合到兩根線上(即兩根線上的噪聲電平相同),因此它的抗噪聲能力比單端信號要強得多。另外,LVDS驅動器的輸出采用電流驅動方式(圖1),與其它差分信號標準中的電壓

2017-04-06 16:11:31 6

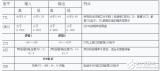

6 ECL電平、LVDS電平、TTL電平三者的簡單比較,在應用方面酌情選取

2016-08-29 16:05:01 69

69 什么是LVDS?

現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。

2016-06-17 15:42:45 16

16 低電壓差分信號(LVDS)是一種高速點到點應用通信標準。多點LVDS (M-LVDS)則是一種面向多點應用的類似標準。LVDS和M-LVDS均使用差分信號,通過這種雙線式通信方法,接收器將根據兩個互補

2013-08-22 16:09:00 92

92 LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗大、EMI電磁干擾大等缺點而研

2012-07-19 16:01:53 5074

5074

文中以基于FPGA設計的高速信號下載器為例,從LVDS的PCB設計,約束設置和信號完整性仿真等多方面研究LVDS信號的實現。

2012-04-20 10:37:02 51

51 隨著數字電路數據量的提高,數據的傳輸速率也越來越快,LVDS(低壓差分信號)標準越來越多的應用在FPGA和ASIC器 件中。文章對LVDS信號的特點進行了分析,說明了PCB設計中差分走線的注意事項并結合實際應用設計了一塊LVDS接口板。 關鍵詞: LVDS; PCB設計;接口;阻抗

2011-02-23 09:54:03 339

339 基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 38

38 MAX9376 LVDS/任意邏輯至LVPECL/LVDS、雙路電平轉換器

概述

The MAX9376 is a fully differential

2009-12-19 12:11:39 1492

1492

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1602

1602

lvds是什么意思?

摘要:與ECL、PECL和CML標準相比,ANSI EIA/TAI-644的低電壓差分信號(LVDS)標準具有低功耗、低噪聲輻射等優勢。本文主要討論LVDS的特性及

2009-05-01 11:13:29 9857

9857

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 1198

1198

摘要:與ECL、PECL和CML標準相比,ANSI EIA/TAI-644的低電壓差分信號(LVDS)標準具有低功耗、低噪聲輻射等優勢。本文主要討論LVDS的特性及其可能的應用。 最近幾年,隨著微

2009-04-24 16:04:30 862

862

LVDS與RS422/RS485的應用設計比較

公司產品中,有些時鐘傳輸使用LVDS電平,有些使用了RS422電平。其實,RS422電平也是差分形式,其電

2008-10-16 13:58:57 10752

10752 LVDS信號的PCB設計

1 LVDS信號的工作原理和特點 對于高速電路,尤其是高速數據總線,常用的器件一般有:ECL、BTL、GTL和GTL+等。這些器件的工藝成

2008-10-16 13:57:52 3248

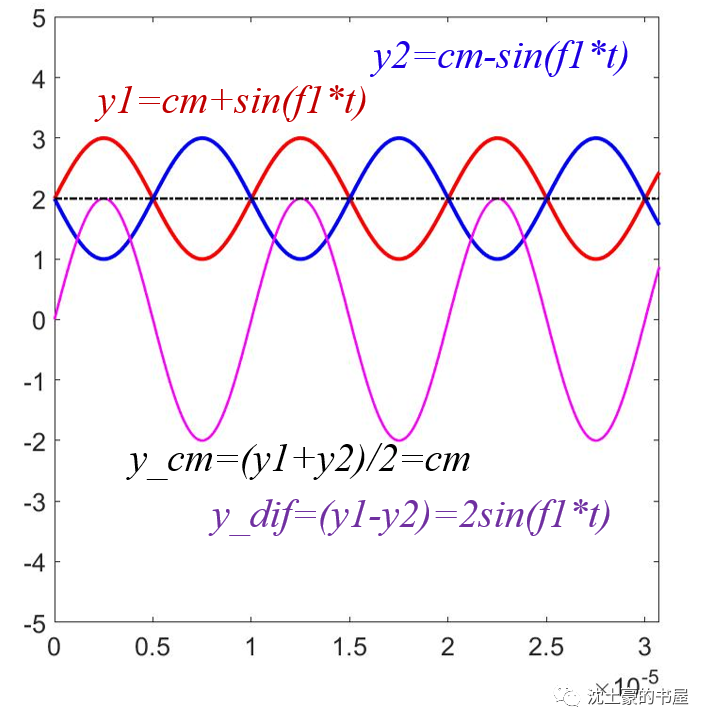

3248 LVDS差分信號抗噪特性

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,在發送側,可以形象理解為:

2008-10-16 13:53:16 1404

1404 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 7293

7293 1 LVDS信號介紹LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號技術,它使得信號能在差

2008-10-16 13:44:45 152

152 84:GTL信號的時序 31

83:GTL信號的測試 30

82:GTL信號的PCB設計 30

81:GTL器件的特點和電平 29

8、GTL器件的原理和特點29

77:LVDS器件應用舉例 28

76:LVDS

2008-06-24 10:04:11 358

358 什么是LVDS?現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應

2007-09-26 11:45:09 4838

4838

電子發燒友App

電子發燒友App

評論