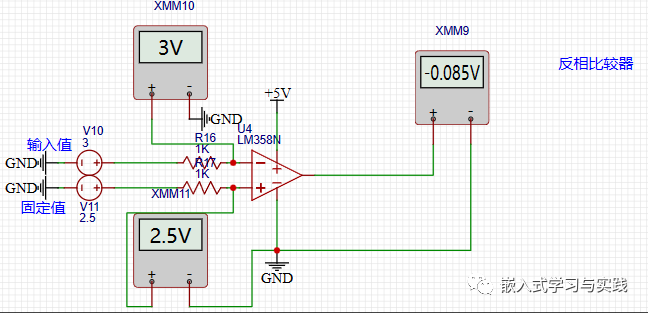

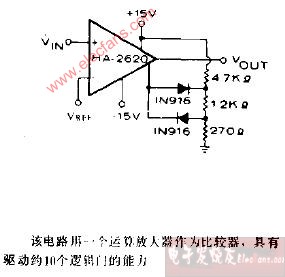

將運算放大器作為比較器使用

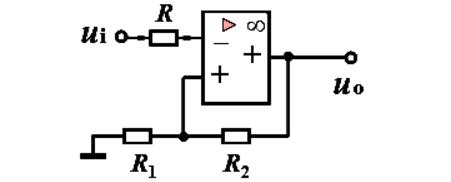

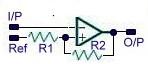

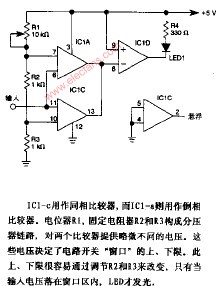

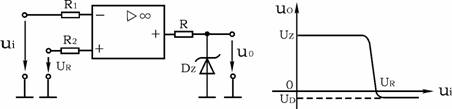

由于運算放大器一般都是雙路/四路的配置,用戶可以考慮將多出來的放大器做為比較器來用。如前所述,此時有不少地方需注意。首先,時間選擇很關(guān)鍵。當把運算放大器用作比較器時,其本身的增益帶寬乘積、群延遲和壓擺率等參數(shù)很可能會因內(nèi)部頻率補償和飽和效應(yīng)而誤產(chǎn)生變化。對于優(yōu)化的單器件來說,這種應(yīng)用不失為一種經(jīng)濟增值方案。可是,對于比較復雜和可能阻礙性能發(fā)揮的四路器件來說,這種方案不但所占的空間較多,而且需要花費更多時間測試和調(diào)試以確

保運算放大器的特性能夠配合。運放用作比較器時需要注意以下幾點:

·細閱數(shù)據(jù)表上敘述的運放拓撲和提示信息。

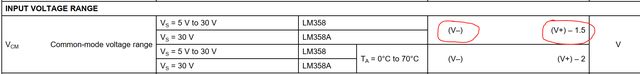

·注意源阻抗、共模輸入范圍和差分輸入范圍。

·放大器在過驅(qū)時的開關(guān)速度并計劃為這參數(shù)進行大型擴展。

·注意溫度變化帶來的影響。

·通過檢查負載阻抗、電源水平和電路的穩(wěn)定性來確保輸出已正確地連接到下一級。

·小心處理電路的設(shè)計和布局,例如即使只有很微量的輸出通過分布電容和/或高輸入阻抗被正反饋引入到輸入端,都有可能引起振蕩。

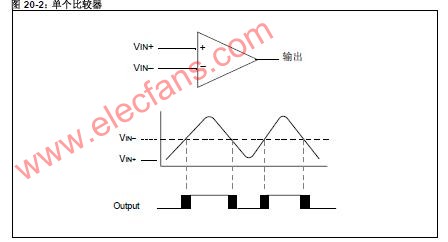

現(xiàn)代高速比較器

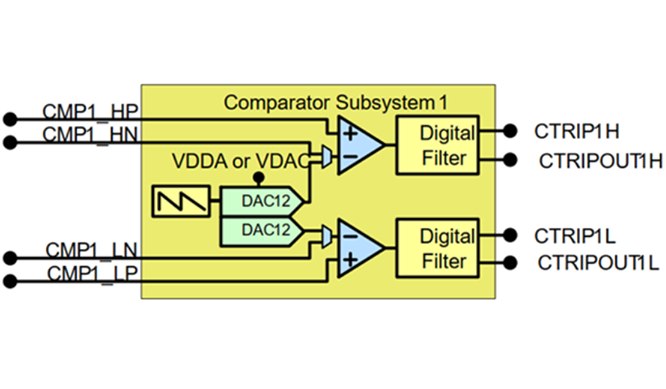

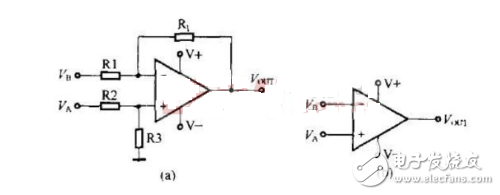

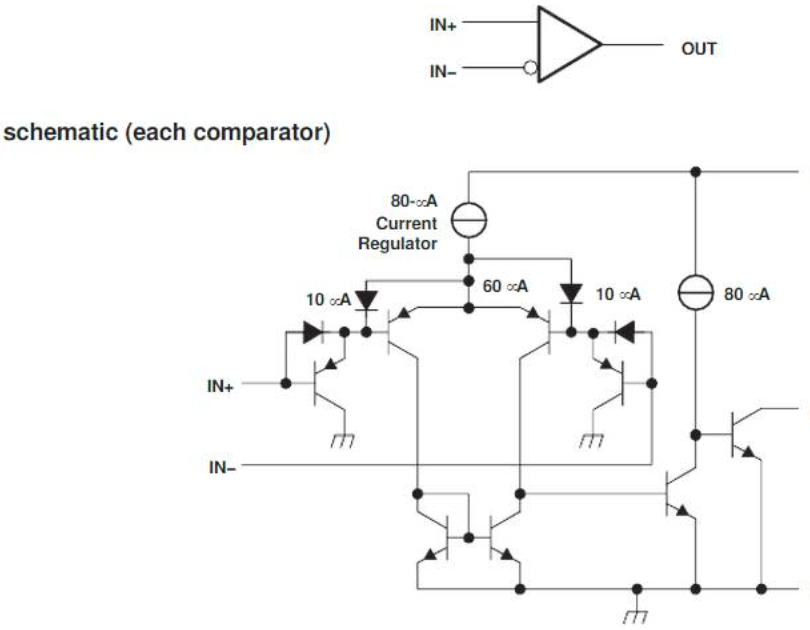

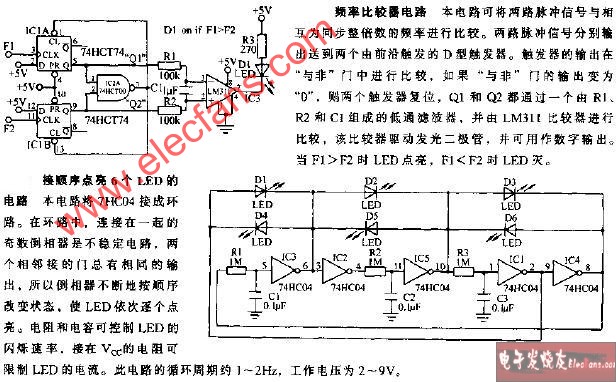

現(xiàn)今業(yè)界常用的比較器大多數(shù)是經(jīng)過優(yōu)化設(shè)計的,可為系統(tǒng)帶來增值效益。最普遍的比較器應(yīng)用類別是電平平移。現(xiàn)今,TTL和CMOS邏輯電平均已被廣泛采用。對于高速應(yīng)用而言,還可采用ECL(發(fā)射極耦合邏輯)、RSPECL(擺幅削減正發(fā)射極耦合邏輯)或LVDS(低壓差分信號)。當需要從電纜和線路連接IC和FPGA,或在背板內(nèi)的信號速度處于由每秒數(shù)百兆位至數(shù)千兆位的高速范圍時,上述方案便會成為首選。LMH7220和 LMH7322便是可用作為高速/超高速電平比較變換的高速比較器件。

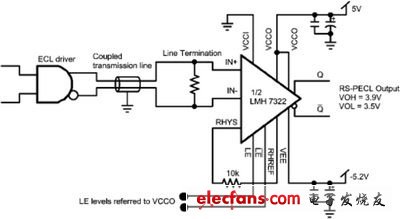

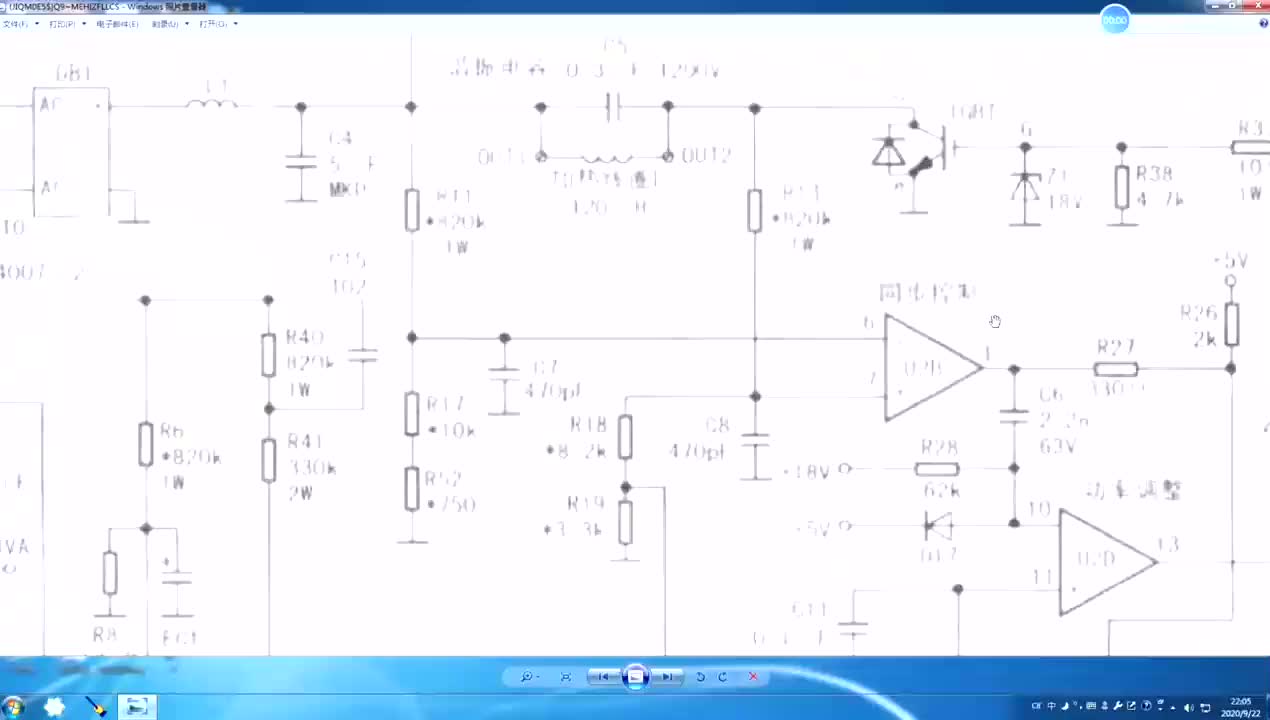

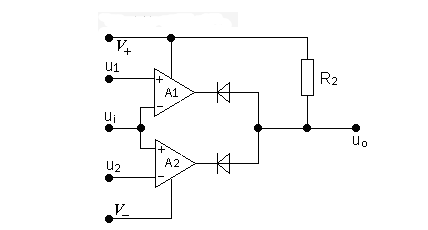

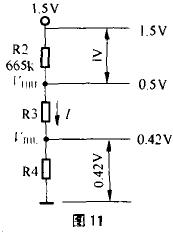

圖2表示出一個LMH7322雙高速比較器,并且以ECL變換到RSPECL的轉(zhuǎn)換器方式實現(xiàn)。ECL高速邏輯已經(jīng)沿用了很多年,尤其是供軍事或測量用以及工業(yè)用的高檔設(shè)置,而且它們屬于負電壓電平參考信號(-5.2V接地),難以連接到其它分離電源或單電源系統(tǒng)。幸而,LMH7322不單可有效解決上述的問題,與此同時比較起一般的邏輯電平移位器,它可提供給設(shè)計人員更大的自由度。該比較器在輸入和輸出電路上擁有不同的電源引腳,而其電源可以是由2.7V至12V的單一電源,又或是由±6V至±1.35V的分離電源。器件在輸入時的共模范圍可超出最低的電源電平200mV,從而令能在如此低的輸入信號電平下感測到細微的信號。在高邊上,共模范圍受到1.5V的VCCI的限制,但需配合2.7V的VCCI和VCCO,還是有可能在輸出上提供PECL邏輯電平。

圖2 ECL 到 RSPECL 的電平變換

假如典型的上升和下降時間為160ps,而典型的傳播延遲則為700ps,那便可促使該比較器為高速至每秒數(shù)千兆位的信號進行緩沖和電平平移,從而使電路適合應(yīng)用在高速數(shù)據(jù)、時移、緩沖,或是來自電纜或背板的信號恢復。一個可調(diào)節(jié)的滯后可通過HYST引腳來施行,這做法對于失真信號或DC耦合線路或移動緩慢的信號來說最為受用,因為這可避免出現(xiàn)不必要的開關(guān)和觸發(fā)。圖2中的應(yīng)用電路表示出輸入VCCI信號是處于系統(tǒng)接地電平,而VCCO電平和VEE電平則分別處于+5V和-5.2V(這便是ECL驅(qū)動器負電源電平)。此外,輸出電壓將可符合RSPECL的規(guī)格。同一個器件可以用來介接到其他的邏輯電平,只需稍為調(diào)節(jié)VCCI和VCCO及VEE電壓電平便可。加入例如是50W的適當線路端接是有可能的,圖3所示為一基本端接例子。

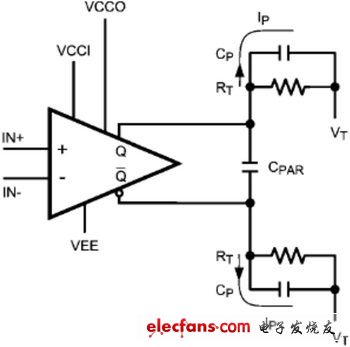

圖3中的差分輸出以一個跟隨著電源電流的發(fā)射極來實現(xiàn),并且確保兩個輸出引腳之間的擺幅差別有400mV。假如這里采用有源端接,那電壓便會低于VCCO電平2V,否則每當端接到芯片的最負電源時,便需計算出正確的負載電阻。

圖3 LMH7322的輸出線路端接例子

此外,上升/下降時間或帶有消散的傳播延遲等參數(shù)均需要慎重考慮,而且它們不是全部都被規(guī)定。消散可以因共模、過驅(qū)和壓擺率的變化而引致,從而影響傳播延遲、工作周期和抖動。以LMH7322為例,過驅(qū)消散或比較20mV至1V過驅(qū)的變化為75ps,在這情況下會大概增加本身的傳播延遲約10%。

電子發(fā)燒友App

電子發(fā)燒友App

評論