鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個專門從事電子設計自動化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導體、計算機系統、網絡工程和電信設備、消費電子產品以及其它各類型電子產品的設計。產品涵蓋了電子設計的整個流程,包括系統級設計,功能驗證,IC綜合及布局布線,模擬、混合信號及射頻IC設計,全定制集成電路設計,IC物理驗證,PCB設計和硬件仿真建模等。 其總部位于美國加州圣何塞(San Jose),在全球各地設有銷售辦事處、設計及研發中心。2016年,Cadence被《財富》雜志評為“全球年度最適宜工作的100家公司”。

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面。包括ASIC 設計,FPGA 設計和PCB 板設計。與眾所周知的EDA 軟件Synopsys相比,Cadence 的綜合工具略為遜色。然而Cadence 在仿真電路圖設計,自動布局布線,版圖設計及驗證等方面卻有著絕對的優勢.Cadence 與Synopsys的結合可以說是EDA 設計領域的黃金搭檔。此外Cadence 公司還開發了自己的編程語言skill,并為其編寫了編譯器。由于skill 語言提供編程接口甚至與C 語言的接口,所以可以以Cadence 為平臺進行擴展用戶,還可以開發自己的基于Cadence 的工具。實際上整個Cadence 軟件可以理解為一個搭建在skill語言平臺上的可執行文件集。所有的Cadence 工具都是用Skill 語言編寫的。

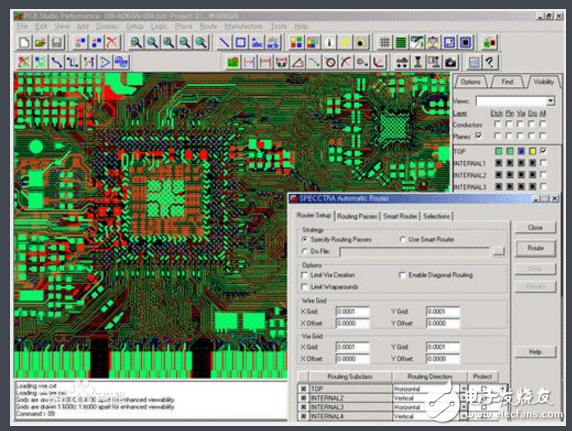

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面,包括ASIC 設計、FPGA 設計和PCB 板設計。Cadence 在仿真、電路圖設計、自動布局布線、版圖設計及驗證等方面有著絕對的優勢。Cadence 包含的工具較多幾乎包括了EDA 設計的方方面面。下面主要介紹其產品線的范圍。

1、板級電路設計系統

包括原理圖輸入、生成、模擬數字/混合電路仿真,fpga設計,pcb編輯和自動布局布線mcm電路設計、高速pcb版圖的設計仿真等等。包括:

A、Concept HDL原理圖設計輸入工具, 有for NT和for Unix的產品。

B、Check Plus HDL原理圖設計規則檢查工具。(NT & Unix)

D、Allegro Expert專家級PCB版圖編輯工具 (NT & Unix)

E、SPECTRA Expert AutoRouter 專家級pcb自動布線工具

F、SigNoise信噪分析工具

H、Synplify FPGA / CPLD綜合工具

I、HDL Analyst HDL分析器

J、Advanced Package Designer先進的MCM封裝設計工具

2、Alta系統級無線設計 這部分包括:

A、SPW (Cierto Signal Processing Work System)信號處理系統。 可以說,spw包括了matlab的很多功能,連demo都有點象。它是面向電子系統的模塊化設計、仿真和實現的環境。它的通常的應用領域包括無線和有線載波通信、多媒體和網絡設備。在進行算法設計、濾波器設計、c Code生成、軟/硬件結構聯合設計和硬件綜合的理想環境。

它里面非常有意思的就是信號計算器。

B、HDS (Hardware Design System)硬件系統設計系統

它現在是SPW的集成組件之一。包括仿真、庫和分析擴展部分。可以進行spw的定點分析行為級和rtl級的代碼生成。

C、Mutimedia多媒體 (Multimedia Design Kit)

它可以進行多媒體應用的設計,包括電視會議系統、數字電視等等以及任何種類的圖象處理系統的設計。

D、無線技術Wireless(IS-136 Verification Environment)

無線電技術標準系統級驗證工具,可以在系統級的抽象層上生成、開發和改進遵守IS-54/136 標準的信號處理算法。在完成硬件結構設計后,就可以使用hds直接生成可綜合的hdl描述和相應的標準檢測程序(testbench)。 E、IS-95無線標準系統級驗證 同上。

F、BONeS網絡協議分析和驗證的設計工具。

它是一套軟件系統,專門用來做多媒體網絡結構和協議的設計的。可以用來快速的生成和分析結構單元之間的信息流的抽象模型,并建立一個完整的無線網絡的運作模型。例如,用戶可以改進atm轉換器的算法,并建立其基于微處理器包括高速緩存和內存和總線、通信處理方法的應用模型。 G、VCC 虛擬協同設計工具包

它是用來進行基于可重用的ip核的系統級設計環境。

3、邏輯設計與驗證(LDV)

LDV包括的模塊有:

B、Leapfrog VHDL仿真器

支持混合語言的仿真,其vhdl語言的仿真是通過編譯后仿真,加快了速度。

C、Affirma NC Verilog仿真器

其主要的特點是適合于大系統的仿真。

D、Affirma NC VHDL仿真器

適用于VHDL語言的仿真。

E、Affirema 形式驗證工具--等價檢驗器

F、Verifault-XL 故障仿真器

用來測試芯片的可測性設計的。

G、VeriSure代碼覆蓋率檢查工具

H、Envisia Build Gates 綜合工具

4、時序驅動的深亞微米設計

Cadence 的底層軟件有:

A、邏輯設計規劃器。

這是用于設計早期的規劃工具。其主要用途是延時預測、生成供綜合工具使用的線路負載模型。這個工具是用來在物理設計的早期象邏輯設計者提供設計的物理信息。

B、物理設計規劃器。

物理設計的前期規劃。對于大型設計而言,物理設計的前期規劃非常重要。很多流程中,在前期的物理規劃(floorplan)結束后,就需要一次反標驗證設計的時序。

C、SE (Silicon Ensemble)布局布線器

se是一個布局布線的平臺,它可以提供多個布局布線及后期處理軟件的接口。

D、PBO Optimization基于布局的優化工具

E、CT-GEN 時鐘樹生成工具

F、RC參數提取 HyperRules規生成,HyperExtract RC提取,RC簡化,和delay計算

G、Pearl靜態時序分析

Pearl 除了界面友好的特點外,還有就是可以和spice仿真器交換數據來進行關鍵路徑的仿真。 H、Vampire驗證工具

5、全定制ic設計工具

這部分的工具包括:

A、Virtuos Schematic Composer : IC Design Entry

它是可以進行混合輸入的原理圖輸入方式。支持 vhdl/hdl語言的文本輸入。

B、Affirma Analog DEsign Environment

這是一個很好的混合信號設計環境

C、Virtuos Layout Editor版圖編輯

它支持參數化單元,應該是一個很好的特性。

D、Affirma Spectra

高級電路仿真器和hspice一類的仿真器。

E、Virtuoso Layout Synthesizer

直接的layout生成工具,小規模設計環境

F、Assura驗證環境,包括diva

G、dracula驗證和參數提取包

H、ICCragtsman 布局設計的環境。

在面向ip的設計中比較合適。

電子發燒友App

電子發燒友App

評論