加法器是如何實(shí)現(xiàn)的

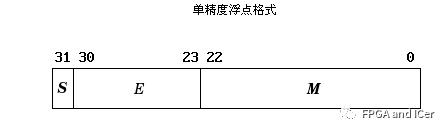

verilog實(shí)現(xiàn)加法器,從底層的門級(jí)電路級(jí)到行為級(jí),本文對(duì)其做出了相應(yīng)的闡述。

1、一位半加器

所謂半加器就是有兩個(gè)輸入,兩個(gè)輸出,不考慮進(jìn)位。其真值表如下:

?

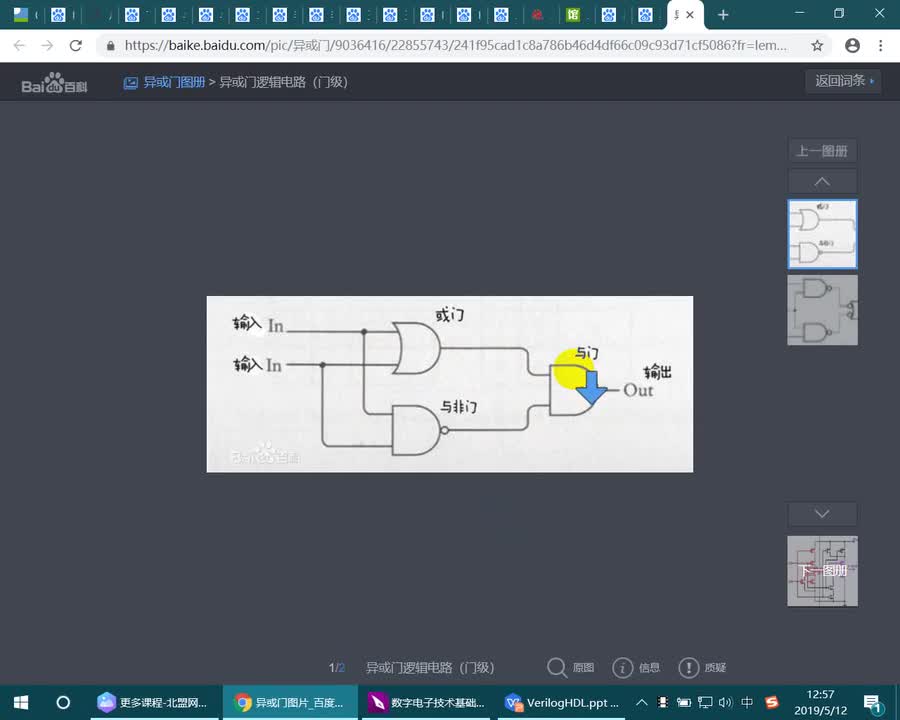

由此,我們可以得到S=A^B,C=A&B。用相應(yīng)的與門、異或門來實(shí)現(xiàn)半加器。

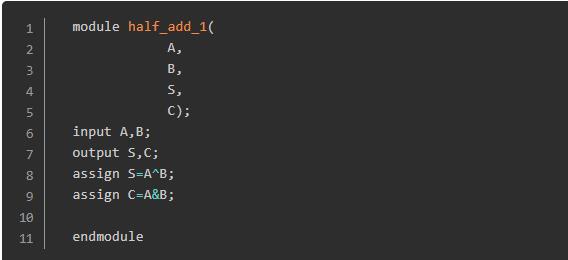

對(duì)應(yīng)的Verilog代碼如下:

?

2、一位全加器

全加器包含三個(gè)輸入,兩個(gè)輸出,其中包含一個(gè)進(jìn)位。

2.1 實(shí)現(xiàn)方式一

與半加器類似畫出其真值表,進(jìn)一步通過畫卡諾圖得到相應(yīng)的函數(shù)表達(dá)式。

S=A^ B^cin,co=(A&B)|(A&cin)|(B&cin)。

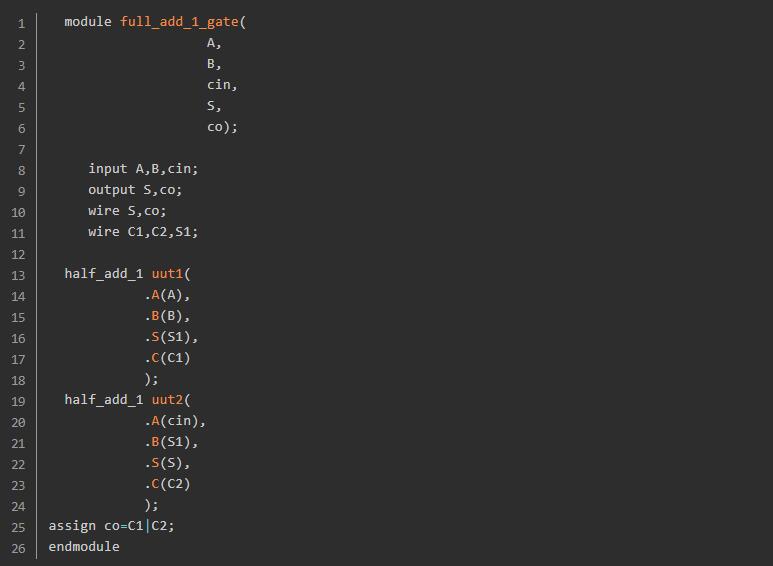

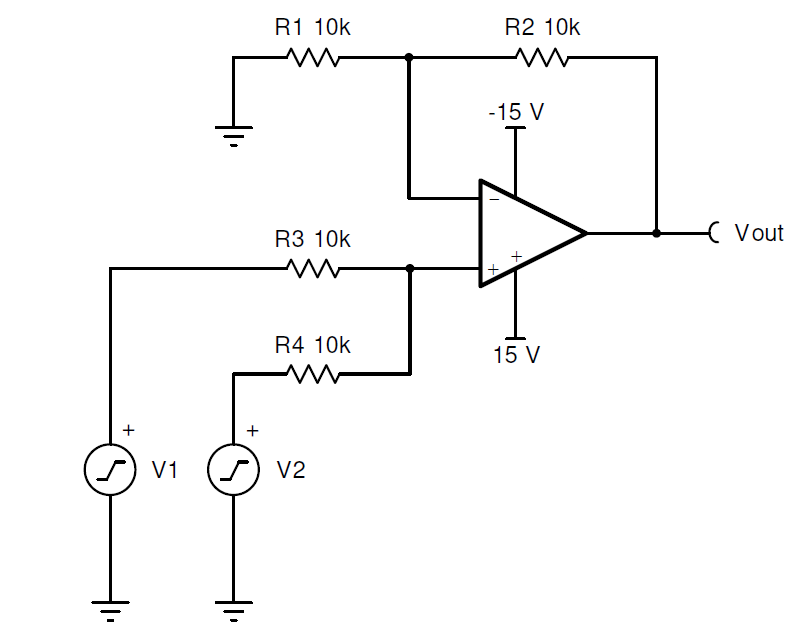

2.2 實(shí)現(xiàn)方式二

利用兩個(gè)半加器和一個(gè)或門實(shí)現(xiàn)全加器。其電路結(jié)構(gòu)圖如下:

?

?

?

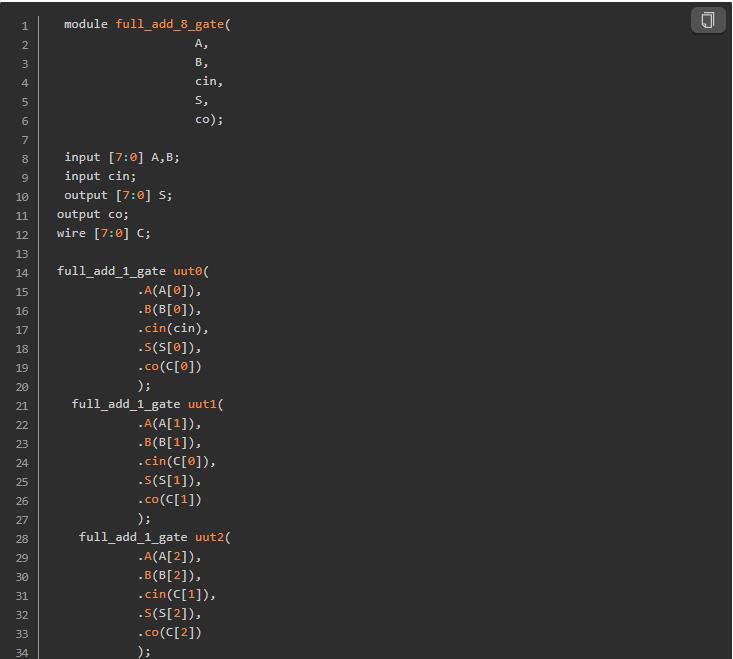

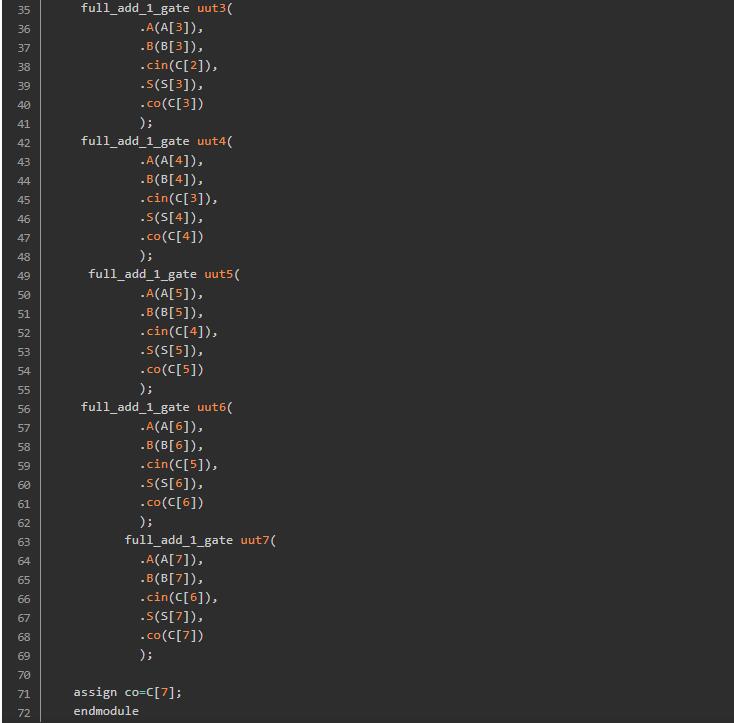

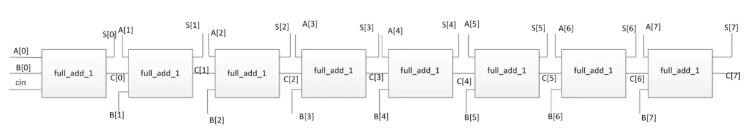

3、多位加法器的實(shí)現(xiàn)

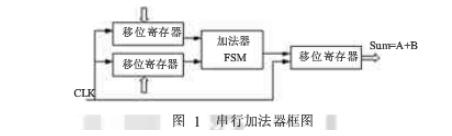

在數(shù)字信號(hào)處理的快速運(yùn)算電路中常常用到多位數(shù)字量的加法運(yùn)算,對(duì)于多位寬加法器的處理,我們以逐位進(jìn)位加法器為例。

代碼和電路結(jié)構(gòu)框圖如下:

串行加法器限制了運(yùn)行的速度,在實(shí)際應(yīng)用中,我們一般用到并行加法器。大致可以分為以下幾類:進(jìn)位旁路加法器、線性進(jìn)位選擇加法器、平方根進(jìn)位選擇加法器、超前進(jìn)位加法器、對(duì)數(shù)超前進(jìn)位加法器。并行加法器比串行加法器快得多,電路結(jié)構(gòu)也不太復(fù)雜,它的原理很容易理解。

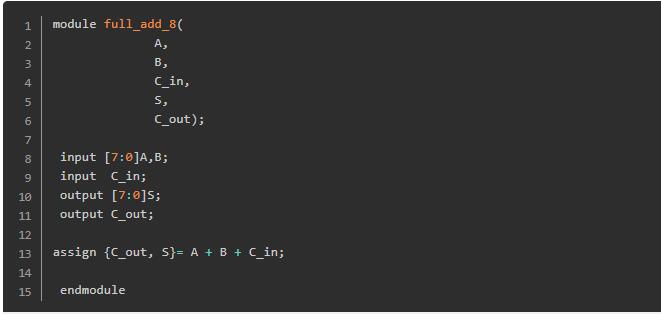

4、行為級(jí)描述加法器

用Verilog HDL來描述加法器是相當(dāng)容易的,只需要將運(yùn)算表達(dá)式寫出就可以了。

一位全加器

?

八位加法器

?

這樣設(shè)計(jì)的加法器在行為仿真時(shí)是沒有延時(shí)的。借助綜合器,可以根據(jù)以上Verilog HDL源代碼將其自動(dòng)綜合成典型的加法器電路結(jié)構(gòu)。綜合器有許多選項(xiàng)可供設(shè)計(jì)者選擇,以控制自動(dòng)生成電路的性能。設(shè)計(jì)者可以考慮提高電路的速度,也可以考慮節(jié)省電路元件以減少電路占用硅片的面積。在FPGA的庫中或某工藝的ASIC庫中,都有參數(shù)化的加法器供設(shè)計(jì)者選用。

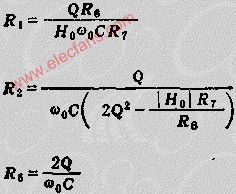

加法器的設(shè)計(jì)優(yōu)化

邏輯改造后,電路也應(yīng)該相應(yīng)地進(jìn)行優(yōu)化設(shè)計(jì),因?yàn)槿绻闷胀ǖ拈T電路來實(shí)現(xiàn)式(12)~(15)的邏輯,晶體管數(shù)目(面積)會(huì)增加。另外,在電路級(jí)也可以采用減少節(jié)點(diǎn)翻轉(zhuǎn)和寄生電容的方法來降低功耗。

式(12)~(15)中多處要用到同或門,設(shè)計(jì)中,我們用基于旁路的靜態(tài)邏輯[4]實(shí)現(xiàn)產(chǎn)生gs的同或門,如圖2。旁路邏輯通過由附加管形成的旁路,可以把“串并交錯(cuò)”的電路結(jié)構(gòu)簡(jiǎn)化為單一的串或者并的形式。它的電路和版圖都有很好的規(guī)整性,并且可以減小寄生電容。是兩種同或門N塊版圖不同部分的比較,(b)是基于旁路邏輯實(shí)現(xiàn)的,與(a)相比,少了一條金屬連線和兩個(gè)金屬接觸,使版圖變得十分規(guī)整,擴(kuò)散區(qū)不會(huì)被隔斷。在拓?fù)渖希瑑蓷l分支用公共的漏區(qū),達(dá)到最少的接觸孔和金屬互連,比“串并”和“并串”的晶體管配置方式規(guī)整,且寄生電容小。

加法器電路上的延遲值

旁路邏輯不能實(shí)現(xiàn)傳輸門,因而不能用傳輸門實(shí)現(xiàn)同或和異或,但是容易證明,三態(tài)門在速度和功耗方面都比傳輸門優(yōu)越。參照傳輸門的結(jié)合方式,我們用兩個(gè)三態(tài)反相器和一個(gè)反相器實(shí)現(xiàn)了同或門。

實(shí)現(xiàn)了式(13)括號(hào)內(nèi)的兩個(gè)同或邏輯,平均只需要1級(jí)門延時(shí),而用普通門實(shí)現(xiàn)的“與非或與非”形式的同或門需要2級(jí)或3級(jí)門延時(shí)。由上面的同或門設(shè)計(jì)得到啟發(fā),根據(jù)形如式(13)的邏輯,設(shè)計(jì)了一個(gè)10管單元utiandor2。

該單元電路實(shí)現(xiàn)s=c0CK+0CKN,只要把式(12)~(15)中的括號(hào)部分從CK和CKN輸入,輸出就相應(yīng)得到了s0~ s3 。僅當(dāng)CKN=時(shí),電路(a)兩邊均是三態(tài)反相器,構(gòu)成圖5(b)的同或門,兩個(gè)反相器交替導(dǎo)通,s=c0⊙CK ;當(dāng)CKN=CK(發(fā)生幾率比較大),左邊P管和右邊N管,或者左邊N管和右邊P管交替導(dǎo)通,輸出s=CK,從而屏蔽了c0的變化。考察第一組4位CLA中的進(jìn)位產(chǎn)生邏輯最復(fù)雜的s3,參考式(15),當(dāng)g2,g1,g0均為0,p2,p1,p0均為1時(shí),s3= gs3⊙c0,顯然這是一種特殊情況,即低位各位都不產(chǎn)生進(jìn)位,但可以傳遞進(jìn)位時(shí),直接把c0傳至高位與gs同或即可產(chǎn)生和。c0在各位和生成邏輯的最后一級(jí)才加入,可以消除過早加入帶來的不必要的翻轉(zhuǎn)。左右兩塊交替導(dǎo)通,只存在下拉或上拉延時(shí),有類似動(dòng)態(tài)電路延遲小的優(yōu)點(diǎn)。僅用了10個(gè)晶體管,比常規(guī)門實(shí)現(xiàn)的積之和節(jié)省8個(gè)。

責(zé)任編輯:YYX

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論