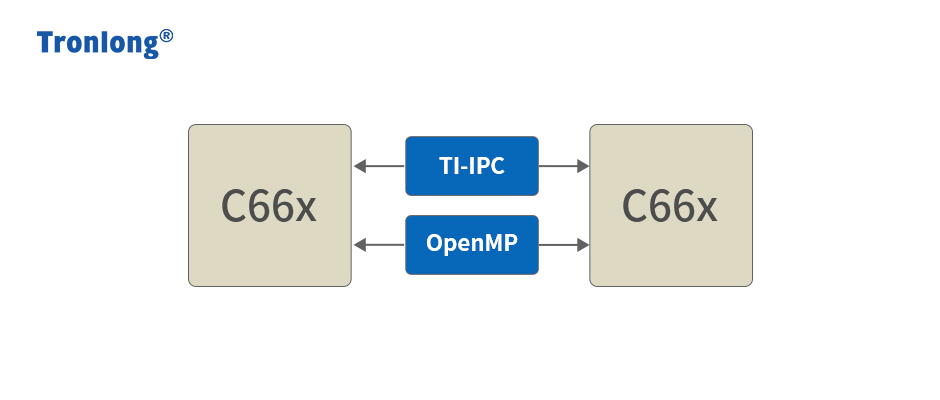

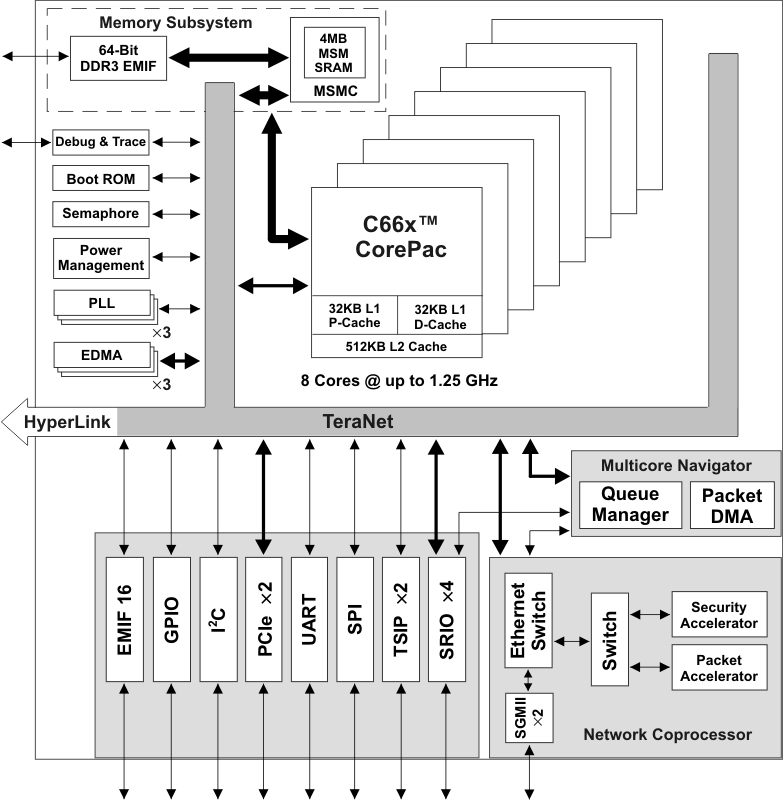

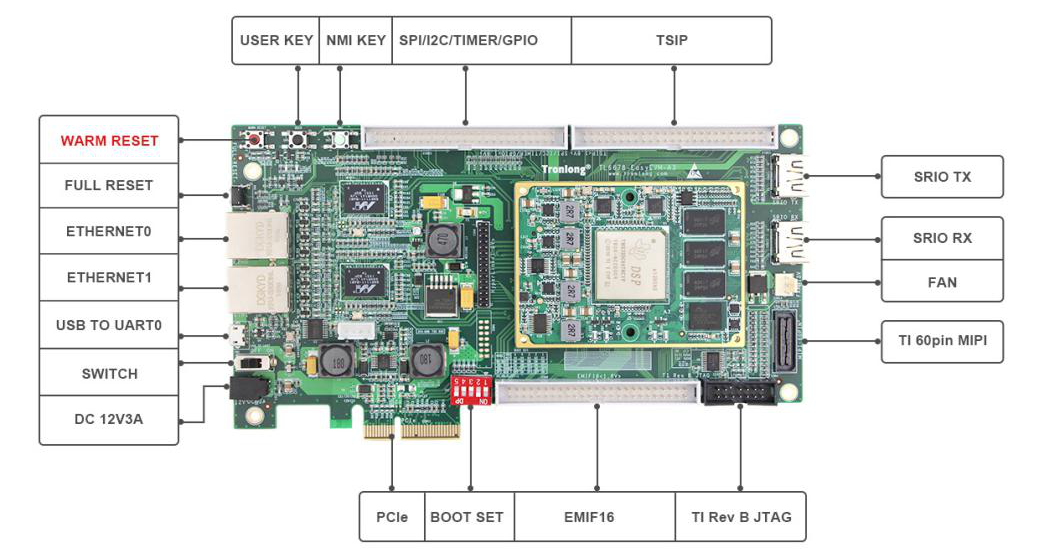

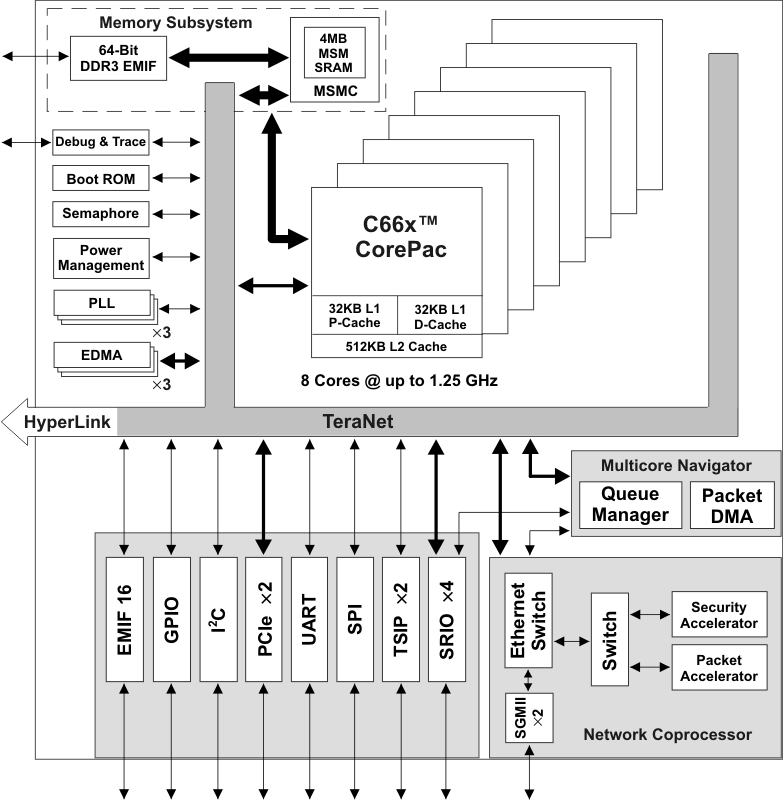

前言 ? ?? ???嵌入式領域的處理器已向多核架構迅速發展,ti公司的KeyStone架構的TMS320C6678是目前市面上性能最高的多核DSP處理器。TMS320C6678集成8核C66x DSP處理器,每個內核頻率高達1.25 GHz,提供每秒高達40 GMAC定點運算和20 GFLOP浮點運算能力;1片TMS320C6678提供等效達10 GHz的內核頻率,單精度浮點并行運算能力理論上可達160 GFLOP,是TS201S的50倍、C67x+的115.2倍,適合于諸如油氣勘探、雷達信號處理、圖像處理以及定位導航等對定浮點運算能力及實時性有較高要求的超高性能計算應用。  ? ?? ???然而,核間通信是多核處理器系統所面臨的主要難點,通信機制的優劣直接影響多核處理器的性能,高效的通信機制是發揮多核處理器高性能的重要保障。 ? ?? ???創龍科技(Tronlong)專注于DSP、ARM、FPGA多核異構技術開發,本文為您介紹TMS320C6678處理器開發中比較常用的兩種多核通信方式:TI-IPC和OpenMP,以及多核編程注意事項。 1 硬件平臺 ? ?? ???本文基于創龍科技TL6678-EasyEVM評估板進行演示。 ? ?? ???TL6678-EasyEVM是一款基于TI KeyStone架構c6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP評估板,由核心板與底板組成。核心板經過專業的PCB?Layout和高低溫測試驗證,穩定可靠,可滿足各種工業應用環境。 ? ?? ???評估板接口資源豐富,引出雙路千兆網口、SRIO、PCIe等高速通信接口,方便用戶快速進行產品方案評估與技術預研。

?

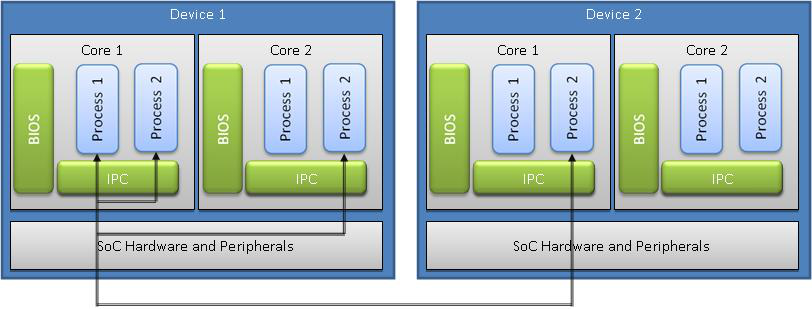

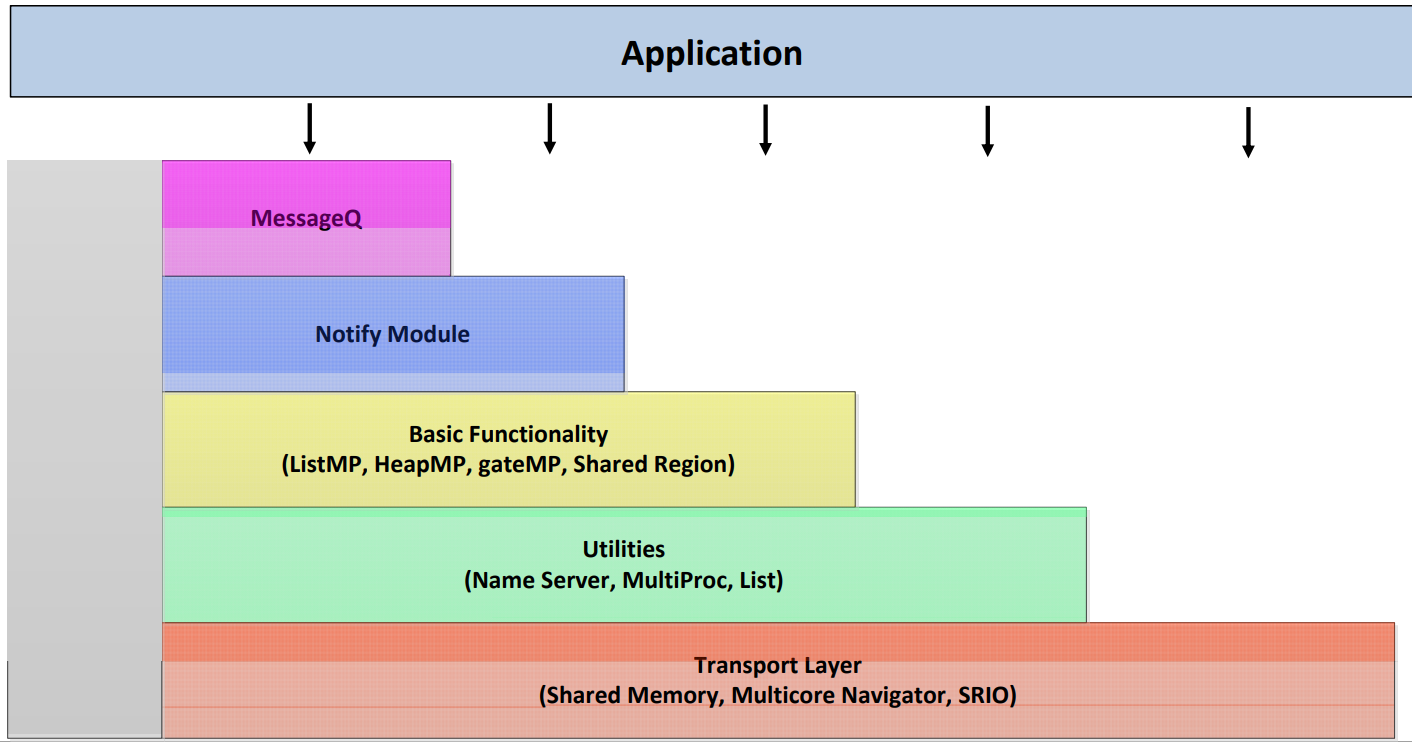

TL6678-EasyEVM評估板 開發案例主要包括: (1) 裸機開發案例 (2) RTOS(SYS/BIOS)開發案例 (3) IPC、OpenMP多核開發案例 (4) SRIO、PCIe、雙千兆網口開發案例 (5) 圖像處理開發案例 (6) DSP算法開發案例 (7) 串口、網絡遠程升級開發案例 C66x DSP視頻教程、中文手冊、產品資料(用戶手冊、核心板硬件資料、產品規格書)可點:site.tronlong.com/pfdownload 直接獲取。 2 TI-IPC 2.1 簡介 ? ?? ???TI-IPC(Inter-Processor Communication)組件提供與處理器硬件無關的API,可用于多核處理器核間通信、同一處理器進程間通信和設備間通信。API支持消息傳遞、流和鏈接列表,它們在單處理器和多處理器中配置均可兼容。 ? ?? ???TI-IPC被設計在運行SYS/BIOS應用程序的處理器上使用,一般為DSP處理器(如TMS320C6678、TMS320C6657),但在某些情況下亦可能是ARM處理器。

?

IPC常見的通信模塊如下: 表1

?

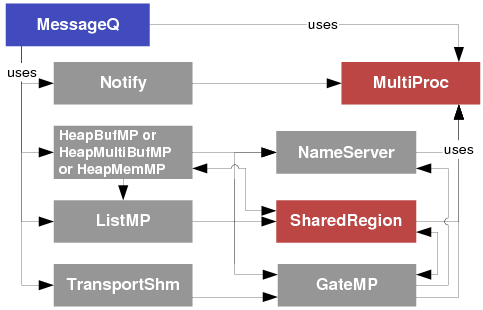

2.2 常用模塊 2.2.1 MessageQ 該模塊具有如下特點: (1) 兼容性強,可在不更改運行代碼的情況移植至另一個支持TI-IPC MessageQ的處理器或其他傳輸層(如Shared Memory、Multicore Navigator、SRIO)。 (2) 支持可變長度消息的結構化發送與接收。 (3) 單個MessageQ隊列支持單個reader和多個writer。 (4) 消息接收支持超時機制。 (5) reader可根據消息頭部信息對writer進行確認后再回復。 (6) Ipc_start()會幫助用戶完成下圖中灰色框內的功能,用戶僅需關注紅色框中的內容即可。

?

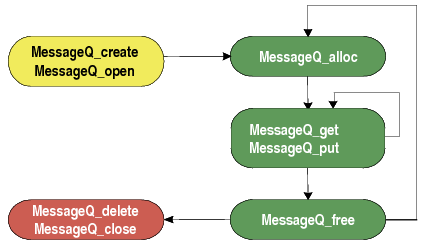

? ?? ???MessageQ通過消息隊列發送和接收消息。reader是一個從消息隊列中讀取消息的線程,writer是一個將消息寫入消息隊列的線程。每個消息隊列都有一個reader,但可有多個writer。 ■ reader:調用MessageQ_create()、MessageQ_get()、MessageQ_free()和MessageQ_delete()。 ■ writer:調用MessageQ_open()、MessageQ_alloc()、MessageQ_put()和MessageQ_close()。 ? ?? ???MessageQ常見的工作流程如下所示。

?

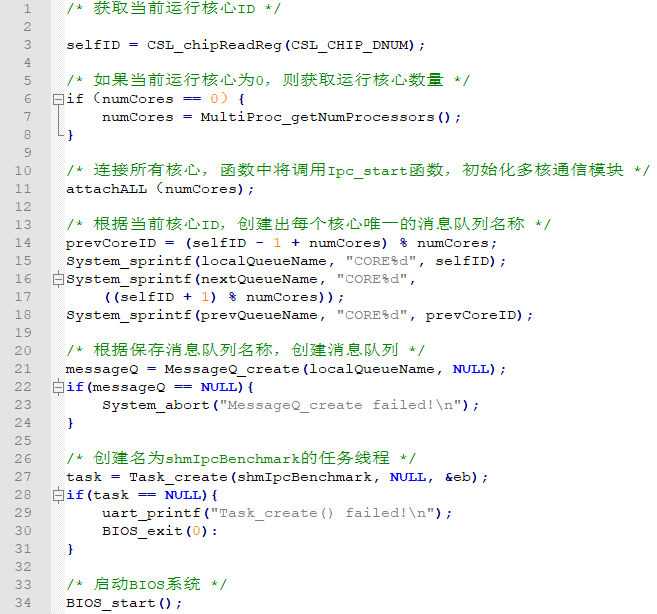

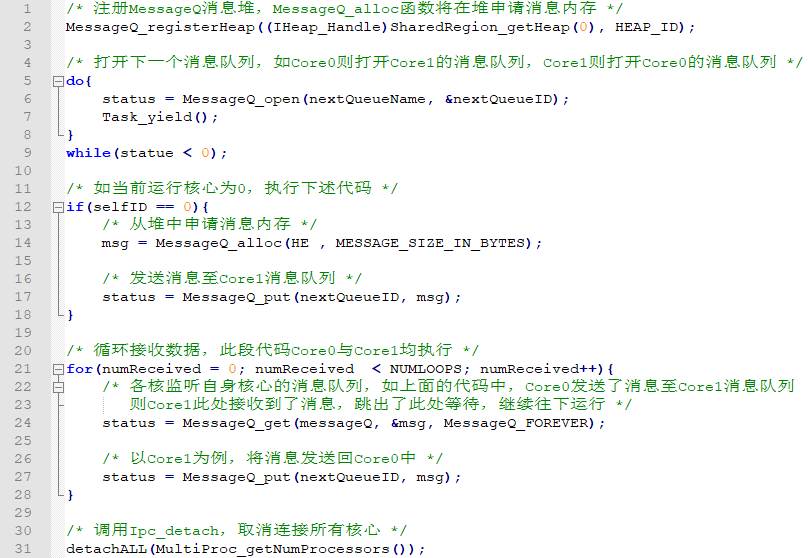

? ?? ???下面以多核IPC通信的shmIpcBenchmark案例為例,分析代碼中MessageQ的使用,見圖中注釋。

?

?

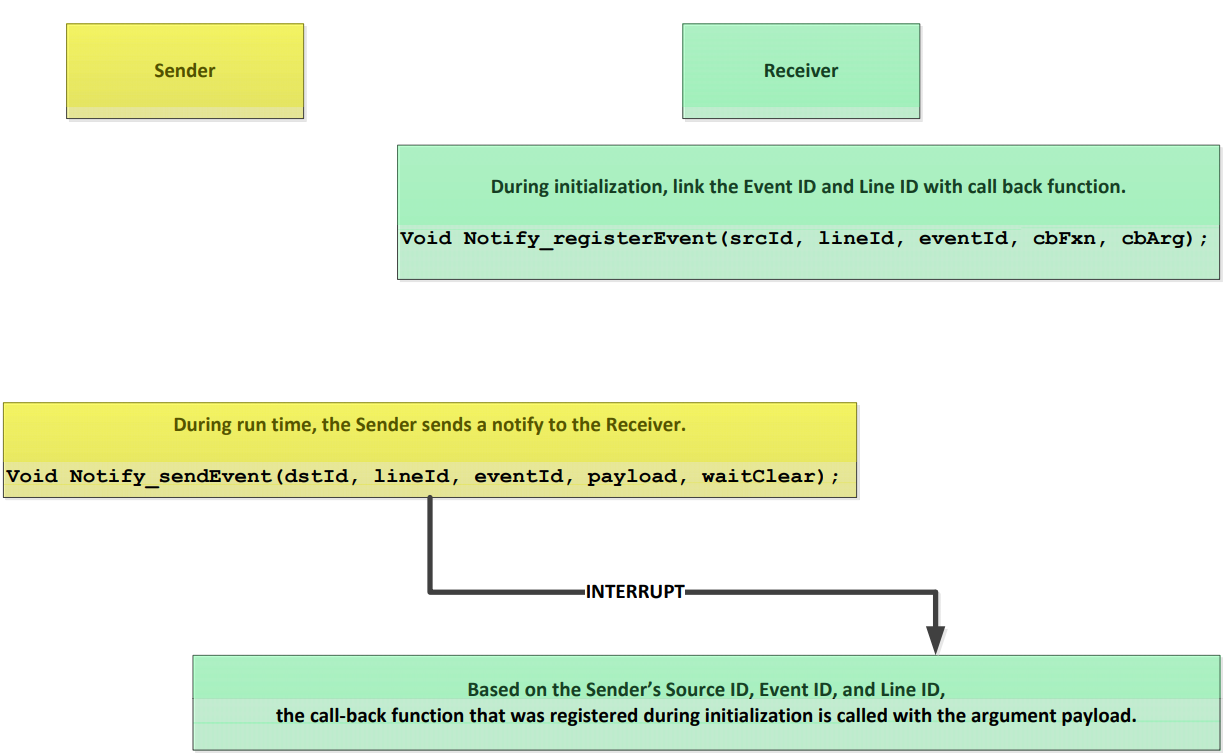

2.2.2 Notify 該模塊具有如下特點: (1) 可獨立于MessageQ模塊進行使用。 (2) 著重于多核通知功能,是更為簡單的多核通信形式。

?

(3) 僅可基于Shared Memroy方式進行使用。

?

? ?? ?Notify通過硬件中斷傳輸消息,Receiver注冊Notify事件中斷,Sender通過Notify發送事件中斷,從而實現通知并攜帶小量消息的目的。 ■ Receiver:調用Notify_registerEvent()注冊事件中斷服務函數。 ■ Sender:調用Notify_sendEvent()發送事件中斷。 ? ?? ?Notify常見的工作流程如下所示。

?

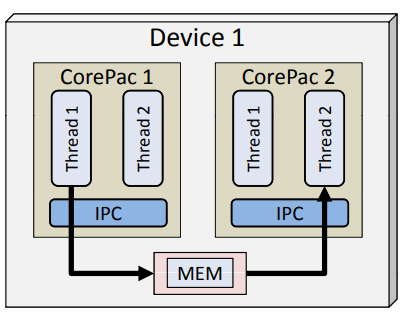

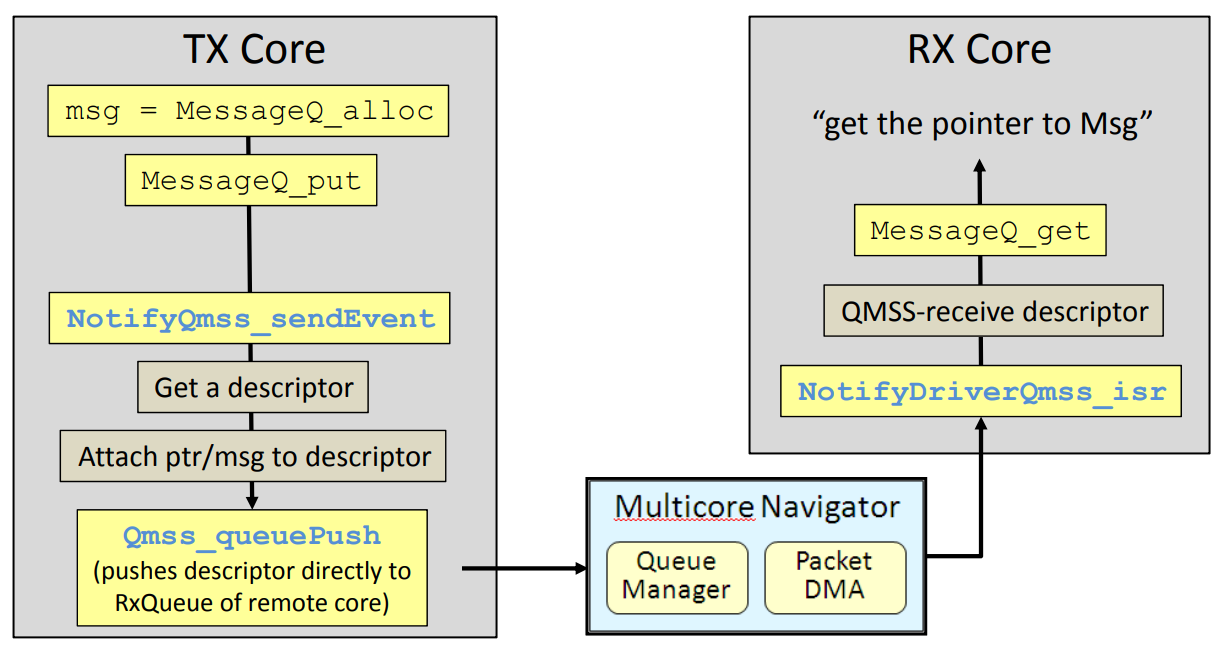

2.3 物理傳輸方式 ? ?? ?TI-IPC的數據傳輸需結合特定物理硬件與底層驅動,方可實現兩個線程在同一個設備或跨設備間進行通信。常用三種的物理傳輸方式包括Shared Memory、Multicore Navigator和SRIO,具體說明如下。 表2

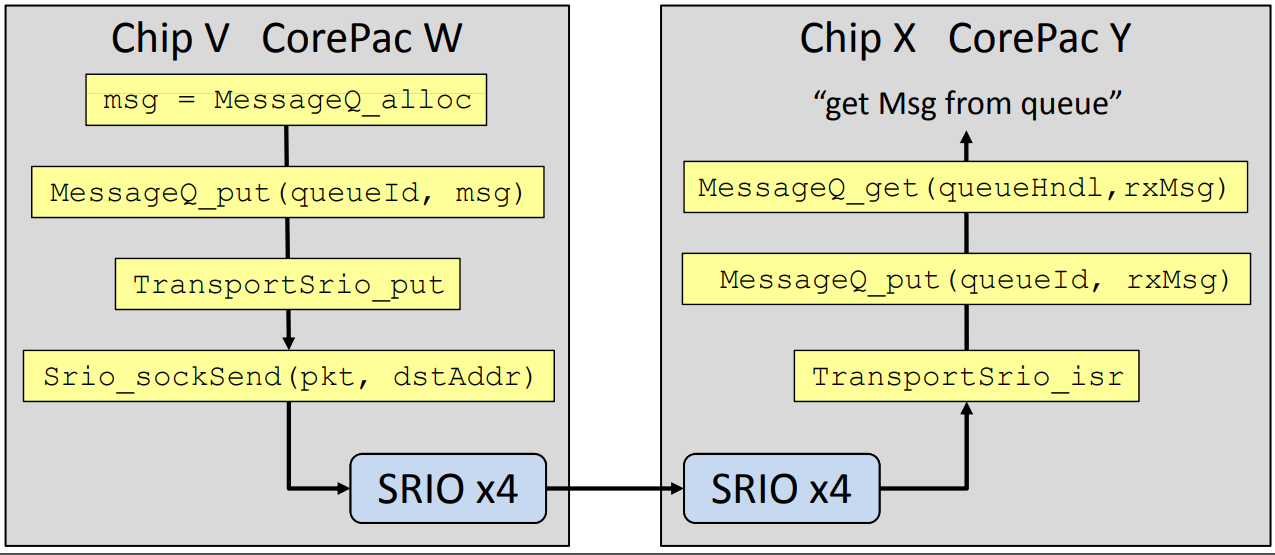

? ?? ?下圖為使用Multicore Navigator、SRIO的API調用流程,用戶僅需關注MessageQ部分操作即可,其他模塊均由系統自動調用。

?

?

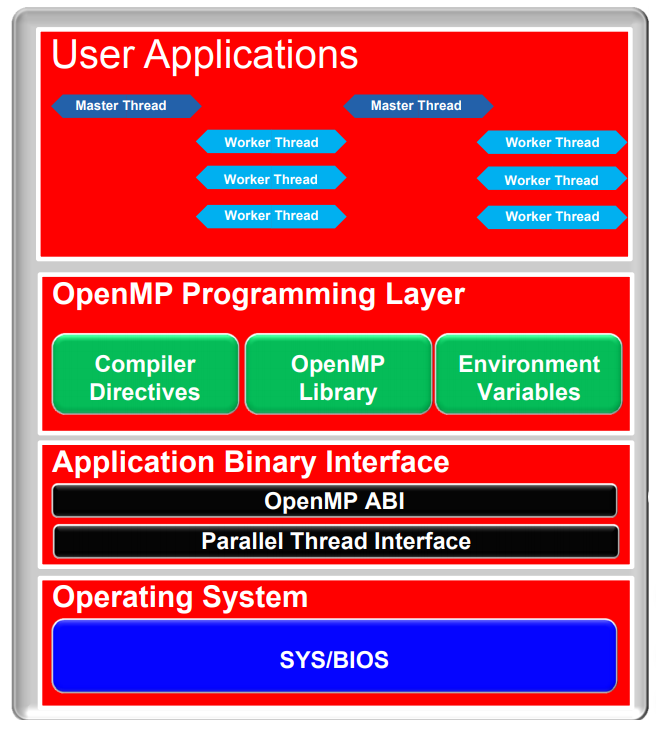

3 OpenMP 3.1 簡介OpenMP是一種多核開發軟件框架,其主要特性如下: (1) 可跨平臺使用,代碼兼容性強。 (2) 以共享內存為通信基礎。 (3) 支持C/C++以及Fortran語言。 (4) 一般基于SYS/BIOS運行。

?

3.2 基本語法 #pragma omp?指令?[子句 [ [ [,]子句 ] ... ] { ... } ? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ???表3

? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?表4

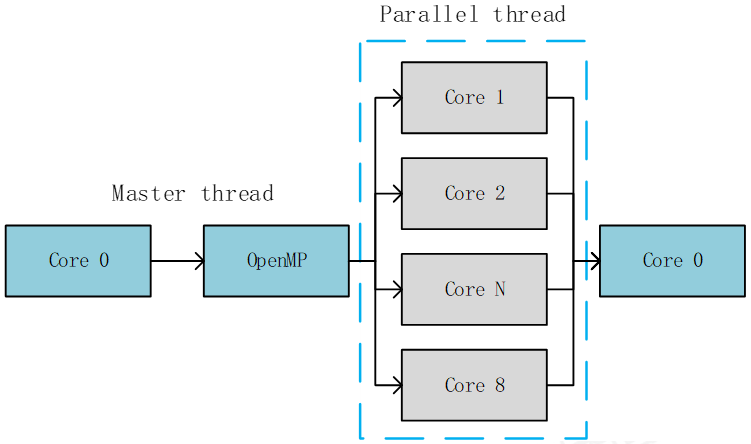

? ?? ?以裸機的omp_matavec案例為例,使用場景的概要流程圖如下。 ? ?? ?C66xx_0核心創建主線程,通過OpenMP框架加載matvec算法至C66xx_0~C66xx_7核心進行并行運算,從而減少C66xx_0核心負載,并可加快運算速度。

?

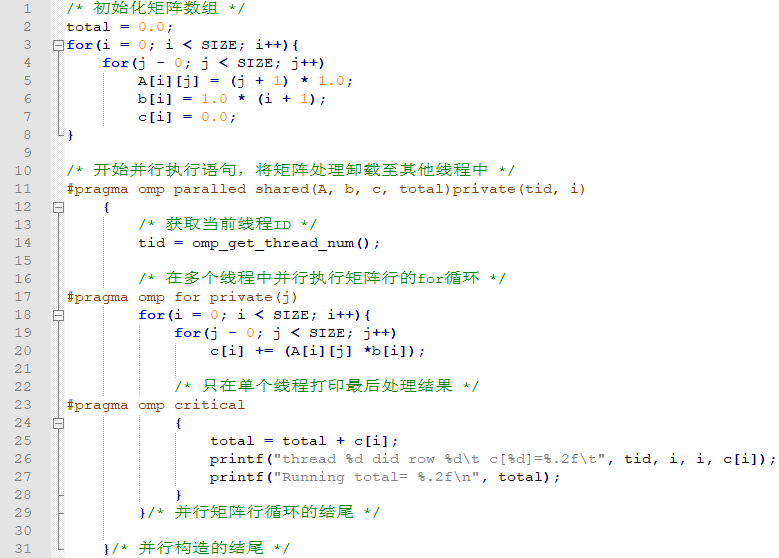

3.3 代碼分析 ? ?? ?以裸機的omp_matavec案例為例進行代碼分析,見圖中注釋。

?

4 多核編程注意事項 4.1 多核單/多鏡像 ? ?? ?在開發過程中,需將程序可執行文件分別加載至對應的核心運行。此時需了解多核單/多鏡像的優缺點,再根據實際情況進行選擇。 多核單鏡像 多核單鏡像指所有核心運行完全相同的用戶程序。 優點:僅需維護一個工程,管理便捷。 缺點:需兼容多個核心代碼,程序可執行文件較大。 多核多鏡像 多核多鏡像指不同核心運行不同的用戶程序。 優點:無需考慮各核心功能的兼容性,單個程序可執行文件較小。 缺點:需維護多個工程,管理不便。 4.2 外設訪問 ? ?? ?所有核心共享外設,如SRIO、PCIe、Ethernet、SPI、I2C、EMIF等。在對外設進行初始化后,所有核心可在任意時間對外設進行讀寫,無需再次初始化。

?

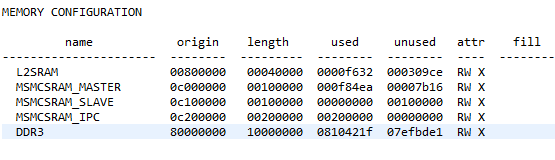

4.3 數據存儲 (1) 注意區分全局與局部地址。 ? ?? ?L1/L2SRAM有全局與局部兩個地址,全局地址可被所有核心訪問,但局部地址僅可被指定核心訪問。 ? ?? ?以C66xx_0核心的L2SRAM為例,對應的全局地址為0x10800000,局部地址為0x00800000。C66xx_0核心使用0x10800000或0x00800000,均可訪問C66xx_0核心的L2SRAM。而C66xx_1核心使用0x00800000僅可訪問C66xx_1核心的L2SRAM,使用0x10800000方可訪問C66xx_0核心的L2SRAM。 ? ?? ?L2SRAM全局與局部地址對應關系如下表: ? ?? ?? ?? ?? ?? ?? ???表5

(2)注意避免內存沖突。 如數據需存放至MSMCSRAM、ddr3共享內存設備,請將對應內存劃分為MSMCSRAM_MASTER段(主核使用)與MSMCSRAM_SLAVE段(從核使用),從而避免運行時內存沖突。

?

5 參考鏈接 -IPC https://training.ti.com/system/files/docs/keystone-intro-ipc-slides.pdf http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#ti-sdo-ipc-package http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#gatemp-support-for-uio-and-misc-driver http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#ti-sdo-utils-package https://processors.wiki.ti.com/index.php/IPC_Users_Guide/MessageQ_Module -OpenMP http://processors.wiki.ti.com/index.php/OpenMP_on_C6000 https://processors.wiki.ti.com/index.php/BIOS_MCSDK_2.0_User_Guide#OpenMP http://community.topcoder.com/tc?module=Static&d1=features&d2=091106 -Multicore Programming Guide https://www.ti.com/lit/an/sprab27b/sprab27b.pdf |

TMS320C6678無法連接?看看多核通信方式TI-IPC和OpenMP多核編程

- 處理器(221450)

- dsp(343833)

- 嵌入式(286111)

- TMS320C6678(17983)

- OpenMP(5583)

相關推薦

基于TMS320C6678的多核DSP上電加載技術

對于多核DSP應用技術來說,BootLoad技術是一個關鍵點,也是應用難點之一。針對8核高性能DSP——TMS320C6678的根配置問題進行了研究,包括上電加載過程,單核和多核的emif

2014-03-26 11:14:32 9494

9494

9494

949418-基于雙TMS320C6678 DSP的3U VPX的信號處理平臺

一、板卡概述 板卡由我公司自主研發,基于3U VPX架構,處理板包含兩片TI DSP TMS320C6678芯片;一片Xilinx公司的Spartan XC3S200AN 配置芯片;一片 IDT

2015-09-22 16:09:34

18-基于雙TMS320C6678 DSP的3U VPX的信號處理平臺

基于雙TMS320C6678 DSP的3U VPX的信號處理平臺一、板卡概述 板卡由我公司自主研發,基于3U VPX架構,處理板包含兩片TI DSP TMS320C6678芯片;一片Xilinx

2015-05-15 17:34:08

1創龍 C6678八核DSP核心板

1 核心板簡介? 處理器架構先進:基于TI KeyStone C66x多核定點/浮點TMS320C6678 DSP,集成了8個C66x核,支持高性能信號處理應用;? 運算能力強:每核心主頻1.0G

2016-03-30 15:38:59

246-基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡

`基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-17 14:38:59

246-基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡

基于TI DSP TMS320C6678、Altera FPGA的CPCI處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-11 16:55:46

6-基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-05-11 17:14:29

6-基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-14 11:56:15

6-基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發,基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-18 15:24:37

6678 多核軟件仿真Illegal opcode,請問出現這個warning的原因?

您好,我的編程環境是CCSV5,使用6678多核開發板,程序主要功能是core0向其余七個核置IPC中斷,core1~core7在ISR中執行調用不同的程序或者執行不同的代碼。程序仿真過程中

2018-08-03 07:20:14

C6678 openMP 例程 連接出錯

用的芯片是c6678,開發板是TMDSEVM6678L,開發環境ccs5.2。mcsdk2.1.2.5。openMP1.1.3.02

跑的是biosMulticore sdk 中的openMP例程

2018-06-21 00:52:01

C6678 多核 IPC通信控制問題

我們使用C6678 core0作為數據接收與控制核,其每接收64M數據后,通過IPC啟動core1,2,3,4分別對16M數據進行并行處理,

在core1,2,3,4完成各自處理后分別向core0

2018-06-21 13:17:13

C66x DSP如何實現程序遠程升級 | 基于TI TMS320C6678平臺

接口升級程序。此時,在不拆箱的前提下實現程序的遠程升級,則顯得尤為重要。基于以上考慮,為了讓嵌入式應用更簡單,創龍科技(Tronlong)基于TI TMS320C6678平臺提供了DSP程序遠程升級

2021-01-11 17:17:19

TI C6678 DSP + Xilinx Kintex-7 FPGA評估板如何進行DSP RTOS案例開發總目錄

今天小編專門以創龍科技的TL6678F-EasyEVM評估板為例為大家詳細講解一款TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP與Xilinx

2021-02-25 19:26:38

TI TMS320C6678是什么?有何功能

CPU處理器TI TMS320C6678是一款TI KeyStone C66x多核定點/浮點DSP處理器,集成了8個C66x核,每核心主頻高達1.0/1.25GHz,支持高性能信號處理應用,擁有多種

2021-12-30 06:08:50

TI CC6678數字信號處理器5個最常見的應用

與DSP的其中一位發明者,Gene Frantz一樣,對我來說,了解客戶如何將我們的處理器應用到實際環境中是再開心不過的一件事情了。然而,我發現基于KeyStone? 的TMS320C6678,一款

2018-09-10 15:16:55

TMS320C6678

TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor datasheet (Rev. E)

2022-11-04 17:22:44

TMS320C6678 連接CMOS攝像頭的接口,請問是將攝像頭連接到TMS320C6678的哪個端口?

您好!我們項目中需要使用TMS320C6678連接攝像頭進行圖像數據采集,請問是將攝像頭連接到TMS320C6678的哪個端口?是將CMOS攝像頭直接連上嗎?還是中間需要轉換器?

2018-08-03 08:33:44

TMS320C6678 CPU工作頻率是多少

我用定時器送出方波的頻率算出CPU工作頻率只有100MHZ(以Timer數據手冊中提到的CPU六分頻作為timer內部時鐘信號為例)。

請問TMS320C6678 CPU工作頻率是多少?

在什么地方可以查看CPU頻率?如何調整頻率?

2018-06-21 03:05:17

TMS320C6678 DDR3 初始化

大家好~有關于DDR3的問題請教

自己畫的TMS320C6678,在調DDR時出現下面的問題

DDR3 Memory Controller Status Register 中

read DQS

2018-06-19 04:29:46

TMS320C6678 求大神幫助

請問,有沒有哪位大神做過TMS320C6678的板子可不可以給我幾張調試板子電源和時鐘模塊時的示波器的波形圖照片板子調不出了又沒有時間了 求幫忙啊~

2014-05-17 23:25:51

TMS320C6678單核作1024點FFT用時?

本帖最后由 一只耳朵怪 于 2018-6-20 09:02 編輯

TMS320C6678單核作1024點FFT用時?(注:是官方標稱的用時)

2018-06-20 01:39:50

TMS320C6678處理器的VLFFT該怎么演示?

本白皮書探討了TMS320C6678處理器的VLFFT演示。通過內置8個固定和浮點DSP內核的TMS320C6678處理器來執行16K-1024K的一維單精度浮點FFT算法樣本,檢測其分別在采用1,2,4或8核時各自的運行時間。

2019-09-29 10:05:23

TMS320C6678學習問題

買了ti的TMDSEVM6678L Rev.3B的板子,也在網上下載了一些學習資料。有些問題想問一下:?

1. ?K1_STK_v1.1 文件夾與K2_STK_DSP_v1.1文件夾的區別,看兩個

2018-06-21 01:20:21

TMS320C6678開發環境搭建1:如何進行USB轉串口驅動安裝?

10 64bit。TMS320C6678評估板簡介創龍TL6678-EasyEVM是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核

2020-11-18 16:06:59

TMS320C6678開發環境搭建3:CCS5.5.0安裝

,上手容易;(3) 提供豐富的Demo程序,包含多核DSP架構通信教程,完美解決多核開發瓶頸。開發例程主要包括:?基于SYS/BIOS的開發例程?基于IPC、OpenMP的多核開發例程?SRIO、PCIe

2020-11-19 12:24:23

TMS320C6678電源方案

您好!

? ? ? ? ? TI對于TMS320C6678這個多核DSP推薦的電源方案是什么?除了Hardware Design guide上面說的UCD9222和UCD7242外還有其他

2018-06-21 07:15:12

TMS320C6678的相關資料推薦

CPU處理器TI TMS320C6678是一款TI KeyStone C66x多核定點/浮點DSP處理器,集成了8個C66x核,每核心主頻高達1.0/1.25GHz,支持高性能信號處理應用,擁有多種

2022-01-03 06:07:08

TMS320C6678系統設計中PCIECLK問題

請問在設計基于TMS320C6678系統板時,如果不用PCIE模塊,是不是可以懸空PCIECLKP和PCIECLKN引腳,還是是分別接高電平和低電平。

2018-06-21 04:10:42

TMS320C6678芯片硬件信號量的應用介紹

實現核間中斷的原理,最后以實例介紹兩個核之間利用硬件信號量交互信息的方法和流程。1 多核DSP及其結構TMS320C6678(C6678)是TI公司多核處理器中的一款8核浮點型DSP,最高工作頻率達到

2022-04-19 10:04:11

TMS320C6678裸機案例測試1:led_flash案例

TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP評估板裸機案例測試:led_flash案例?圖 1?圖 2TMS320C6678案例說明案例功能:通過控制GPIO Output的方式

2020-12-31 21:06:38

c6678多核boot的問題

ti的工程師你好,

? ? ? a最近研究c6678的boot問題,遇到一些疑問,麻煩指點一下:

1,文檔中說到,多核啟動,一般是core0先執行初始化,其他core執行IDEL,等到core0把

2018-06-21 13:32:28

tms320跑linux操作系統時如何實現多核通訊

硬件環境:tms320c6678EVM

軟件環境:CCS5.5.0

tms320跑linux操作系統時如何實現多核通訊,從論壇一些帖子知道它不支持SMP,我的理解是不能由操作系統自動分配調度多個核完成一個復雜任務。那么如何實現多核通訊呢?OMP等等可以嗎?

2018-06-21 06:55:36

多核DSP的多路同步時鐘信號設計

TI公司的C66系列以及AK2系列多核DSP可以實現無縫連接。3硬件設計 根據TMS320C6678的應用,所需要的時鐘如圖3所示。 其主要時鐘包括:①內核運行時鐘,該時鐘輸入是100MHz,DSP

2016-11-28 23:47:01

多核DSP的多路同步時鐘信號設計

TI公司的C66系列以及AK2系列多核DSP可以實現無縫連接。3硬件設計 根據TMS320C6678的應用,所需要的時鐘如圖3所示。 其主要時鐘包括:①內核運行時鐘,該時鐘輸入是100MHz,DSP

2016-10-15 22:43:53

CCS5.5 ,tms320c6678的開發

各位前輩,初學CCS5.5,tms320c6678我現在有個問題,安裝了CCS5.5還要安裝什么插件或者配套標準文件嗎?新建工程時網上說可以用CCS的.cmd文件,但是我根本找不到那個文件,是因為沒有安裝什么配套文件嗎?另外,哪里有6678的例子可以參考一下。謝謝大家

2015-08-14 14:38:30

DSP C66x多核開發|TMS320C6678多核通信方式TI-IPC和OpenMP多核編程注意事項

TMS320C6678處理器開發中比較常用的兩種多核通信方式:TI-IPC和OpenMP,以及多核編程注意事項。1 硬件平臺本文基于創龍科技TL6678-EasyEVM評估板進行演示

2021-01-14 17:31:12

SOM-TL665x是TI系列多核架構的定點/浮點TMS320C665x高端DSP核心板

1.核心板簡介基于TI KeyStone C66x多核定點/浮點DSP TMS320C665x,單核TMS320C6655和雙核TMS320C6657管腳pin to pin兼容,同等頻率下具有四倍

2020-09-17 11:21:40

SOM-TL6678是基于TI 八核C66x定點/浮點高性能處理器設計的DSP工業級核心板

核心板簡介創龍SOM-TL6678是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP工業級核心板,處理器每核心主頻可高達

2020-09-14 16:03:13

TL6678-EasyEVM高端多核DSP評估板

評估板簡介創龍TL6678-EasyEVM是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點高性能處理器設計的高端多核DSP評估板,由核心板與底板組成

2020-09-16 14:49:27

TMDSEVM6678LE評估模塊

XDS560V2 仿真的 C6678/C6674/C6672 多核 DSP 著手開發。TMDSEVM6678LXE - TMS320C6678 Lite 評估模塊,帶加密保護和 XDS560V2已啟用

2021-10-21 15:12:25

seedxds560v2plus和TMS320C6678

高手們:

??? 我在用seedxds560v2plus對TMS320C6678 用USB進行硬件仿真時,*.xxcml的配置文件界面testconnection 是灰色的,不能進行連接測試

2018-06-21 00:50:17

【創龍TMS320C6678開發板】關于多核間通信

codec engine機制來完成DSP核AEM核之間的通信,完成高效率的圖像采集處理。 對于TMS320C6678芯片,TI提供了IPC中斷和共享內存的方式來完成多內核之間的通信。IPC通信提供了通知

2018-12-05 14:06:03

【經驗分享】TI KeyStone I DSP[C665x與C6678] |創龍視頻教程

- OpenMP [上]6-2-2- 多核開發 - OpenMP [下]6.3 - 多核 TI IPC 組件 視頻觀看地址: “地瓜派視頻網”首頁---選擇“課程分類>DSP>TMS320C66x王斌

2019-05-24 16:39:07

【經驗分享】TMS320C6678處理器如何進行OpenMP多核通信案例

本文主要介紹TMS320C6678處理器開發中比較常用的多核通信方式:OpenMP,主要基于創龍科技TL6678-EasyEVM評估板進行演示。?圖1 TL6678-EasyEVM評估板

2021-01-28 20:14:28

兩片TMS320C6678 DSP的供電需求怎么滿足?

TMS320C6678 DSP是TI最新發布的一款基于KeyStone架構的DSP,芯片內有8個內核,工作速度可達10 GHz.隨著這款產品各方面的性能指標增加,對電源供應也提出了很高的要求,普通

2020-03-02 11:06:02

使用sy***ios對6678進行多核軟件仿真,請問DK_C6678_1_1_2_6開發包提供了一些什么?

在使用sy***ios對6678進行多核軟件仿真,做的是圖像處理算法,想知道PDK_C6678_1_1_2_6開發包提供了一些什么,在做純軟件多核仿真的時候需要用到嗎?(多核通訊用的是IPC里的messageQ)

2018-07-24 07:55:56

免費供應TMS320C6678/TMS320C665x+Kintex-7/Artix-7、TMS320C6748+Spartan-6開發板試用

)TL665x-EasyEVM + TL-A7HSAD模塊:(1)TL288AP CameraLink視頻采集卡(2)CameraLink工業相機應用領域:工業檢測,機器視覺,目標追蹤現在可以免費供應TMS320C6678

2019-07-16 14:57:55

八核浮點型DSP雙千兆網接口設計方案

DSP芯片可以連接多個千兆網口,使得其可以應用到高速數據傳輸場合。本文介紹一種基于多核數字信號處理器TMS320C6678的嵌入式雙千兆網絡接口,實現單個芯片連接兩個千兆網口,這兩個網口可以各自獨立

2019-06-20 05:00:03

創龍TI KeyStone C66x八核 TMS320C6678 DSP開發板

TI KeyStone C66x八核 TMS320C6678 DSP開發板1 開發板簡介?處理器架構先進:基于TI KeyStone C66x多核定點/浮點TMS320C6678 DSP,集成了8個

2016-08-14 15:57:04

創龍TI KeyStone TMS320C665x 多核 DSP開發板特點

TI KeyStone TMS320C665x 多核 DSP開發板簡介1 開發板簡介?處理器架構先進:基于TI KeyStoneC66x多核定點/浮點DSP TMS320C665x,單核

2016-08-15 17:23:24

創龍TMS320C6678開發板免費試用

TL6678-EasyEVM 是一款基于廣州創龍 TI KeyStone C66x 多核定點/浮點 TMS320C6678 核心板 SOM-TL6678 設計的高端 DSP 開發板,底板采用沉金無鉛

2018-10-15 10:57:23

基于TMS320C6678處理器的節能型可擴展H.265/HEVC解決方案

測試,包含硬件參考 (EVM)、軟件和用戶指南。TMDSEVM6678 EVM 采用了基于 TI 的 C66x Keystone 多核架構的 TMS320C6678 高性能 DSP,可實現高性能

2019-01-02 15:59:32

基于多核數字信號處理器TMS320C6678的嵌入式雙千兆網絡接口

本文介紹一種基于多核數字信號處理器TMS320C6678的嵌入式雙千兆網絡接口,實現單個芯片連接兩個千兆網口,這兩個網口可以各自獨立傳輸數據,也可以聯合傳輸數據,提高了實際的數據傳輸速率。

2021-02-01 06:29:16

基于CDCM6208多核DSP的多路同步時鐘信號設計

性能較高的TMS320C66系列為例,其中TMS320C6678(以下簡稱C6678)含有8個處理器。這些處理器可以獨立工作,也可以并行聯合工作。當它們聯合工作時,相互之間通信和握手就非常重要,尤其是

2021-02-02 07:53:47

如何用TI DSP TMS320C6678處理器進行TI-IPC多核通信案例

如何用TMS320C6678處理器進行TI-IPC多核通信案例本文基于創龍科技TL6678-EasyEVM評估板進行演示。?圖1TL6678-EasyEVM評估板TL6678-EasyEVM是一款

2021-01-25 19:49:47

廣州創龍基于TI TMS320C6678芯片,研發了一款DSP高性能信號處理應用開發板

其產品基于TI KeyStone C66x多核定點/浮點TMS320C6678 DSP,集成了8個C66x核,擁有支持高性能信號處理應用,每核心主頻1.0/1.25GHz,單核可高達40GMACS

2018-03-06 17:29:18

廣州創龍基于TI TMS320C6678芯片,研發的一款DSP+FPGA高速大數據采集開發板

這款DSP+FPGA的廣州創龍TL6678F-EasyEVM開發板,擁有TI KeyStone C66x多核定點/浮點DSP TMS320C6678 + Xilinx Kintex-7 FPGA

2018-03-06 17:35:26

想建立一個TMS320C6678的工程,但是DEVICE選擇的時候沒有TMS320C6678的選項,能指點一下嗎?

本帖最后由 一只耳朵怪 于 2018-6-19 14:37 編輯

我想建立一個TMS320C6678的工程,但是DEVICE選擇的時候沒有TMS320C6678的選項,能指點一下嗎?如下圖:?

2018-06-19 00:31:18

神板卡,TL6678ZH-EVM(C6678+ZYNQ)評估板|多核DSP+多核ARM+FPGA架構,成為了科研機構、高校實驗室的新寵!

Cortex-A9 + PL端Kintex-7架構28nm可編程邏輯資源,ARM主頻800MHz。?核心板硬件框圖?評估板硬件框圖? TI TMS320C6678處理器功能框圖?Xilinx Zynq-7000處理器

2021-03-16 17:35:46

請教6678多核硬件調試的問題

)() at copy_decompress_rle.c(_TI_decompress_rle_core does not contain frame information)請幫忙解釋下這是什么情況三、請問有沒有現成的多核例程代碼,可以給我們參考借鑒下嗎?剛接觸6678,多核的問題困擾了我很久了,請幫忙答疑解惑下,謝謝大家!

2018-08-03 07:12:14

請問TMS320C6678選擇CLASS0,是否意味著可以用一款普通的開關電源(ltm4616)來代替呢?如果可以,該電壓值如何確定?

壓為一確定值。但是我沒有在TMS320C6678數據手冊中找到相關信息。如果TMS320C6678選擇CLASS0,是否意味著可以用一款普通的開關電源(ltm4616)來代替呢?如果可以,該電壓值

2018-06-25 07:19:23

請問c6678使用gateMP如何進行多核共享保護?

本帖最后由 一只耳朵怪 于 2018-6-19 10:51 編輯

大家好,最近研究6678,需要多核對相同地址的數據進行操作,因此需要增加保護,讓同一時間只有一個核可以訪問。從IPC的文檔中發

2018-06-19 04:09:26

請問tms320c6678在CPCI板卡上如何設計

我想用tms320c6678作為處理器設計一款CPCI的板卡,可是6678上只有PCIE,沒有PCI,我應該怎么做才能實現6678與上位機之間通信,謝謝!!!

2018-12-28 11:05:42

請問tms320c6678引腳圖在哪里?

本帖最后由 一只耳朵怪 于 2018-6-19 15:33 編輯

我現在正學著畫tms320c6678的原理圖,可找不到它的引腳圖,我該怎么么辦呢

2018-06-19 06:20:43

德州儀器與德州大學奧斯汀分校聯合推出基于多核DSP的線性代數庫

日前,德州儀器與德州大學奧斯汀分校成功將該校科學計算高密度線性代數庫移植至TI TMS320C6678多核數字信號處理器,成為多內核創新的又一里程碑。

2011-11-22 10:25:40 631

631

631

631TI推出適合高性能計算的8核DSP產品TMS320C6678/TMS320TCI6609

德州儀器 (TI) 宣布推出 TMS320C66x系列最新產品TMS320C6678 與 TMS320TCI6609 數字信號處理器 (DSP),為開發人員帶來業界性能最高、功耗最低的DSP

2011-11-22 10:40:50 2936

2936

2936

2936德州儀器(TI)推出TMS320C66x多核DSP新品

德州儀器 (TI) 宣布推出 TMS320C66x 系列最新產品TMS320C6678 與 TMS320TCI6609 數字信號處理器 (DSP),為開發人員帶來業界性能最高、功耗最低的DSP,這預示著全新高性能計算 (HPC) 時代的到來

2011-11-22 11:53:54 960

960

960

960TI與UT Austin推基于TI多核DSP的線性代數庫

日前,德州儀器 (TI) 與德州大學奧斯汀分校 (UT Austin) 成功將該校科學計算高密度線性代數庫(libflame 庫)移植至 TI TMS320C6678 多核數字信號處理器 (DSP),成為多內核創新的又一里程碑

2011-11-22 11:55:42 911

911

911

911基于多核DSP的SDIF雷達信號分選算法實現

針對實際應用中電子戰設備對雷達信號分選的實時性要求,在分析了序列差直方圖算法和多核DSP任務并行模式的基礎上,設計了基于TMS320C6678的八核DSP雷達信號分選電路,對密集的雷達

2013-07-26 11:47:05 54

54

54

54TMS320C6678視頻編解碼實現

TI 提供了包含有綜合而全面的視頻、音頻和語音編解碼組合的全新多媒體解決方案。TMS320C6678可以幫助實現系統級的低成本、低功耗和高密度媒體解決方案,適用于多媒體網關、IMS 媒體服務器、視頻會議服務器以及視頻廣播設備等應用領域。

2016-01-20 15:52:26 15

15

15

15基于TMS320C6678的合成語音檢測算法

針對合成語音檢測系統在大規模電信網應用中的實時性需求,在分析合成語音檢測原理和多核DSP任務并行的基礎上,提出了一種基于TMS320C6678的合成語音檢測算法并行實現方法,該方法實現了任務級并行

2017-11-14 14:47:38 15

15

15

15TMS320C6678處理器的VLFFT演示探討與研究

1,2,4或8核時各自的運行時間。演示的結果證明了C66X DSP內核的優異性能,以及TMS320C6678處理器跨多核平行化執行性能與內核數量成正比的特性。 本文的演示采用FFT算法,該算法在諸如醫學成像、通信、軍事和商業雷達以及電子戰(干擾器、抗干擾器)等領域中被頻繁應用。

2018-01-31 22:58:02 3921

3921

3921

3921

TMS320C6678多核定點和浮點數字信號處理器的詳細資料概述

本文的主要內容介紹的是TI的產品TMS320C6678多核定點和浮點數字信號處理器的詳細資料概述

2018-04-28 16:32:41 21

21

21

21TMS320C6678 多核定點和浮點數字信號處理器

電子發燒友網為你提供TI(ti)TMS320C6678相關產品參數、數據手冊,更有TMS320C6678的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TMS320C6678真值表,TMS320C6678管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-11-02 19:35:06

基于IPC、OpenMP的C66x多核開發視頻教程

本文為您分享基于IPC、OpenMP的C66x多核開發視頻教程,適用于TI TMS320C6678、TMS320C665x平臺。

2020-07-29 15:35:26 969

969

969

969創龍結合TI KeyStone系列多核架構TMS320C6678 DSP以及Xilinx Kintex-7 FPGA評估板電源接口和撥碼開關

CPU處理器基于TI KeyStone C66x多核定點/浮點DSPTMS320C6678+ Xilinx Kintex-7FPGA的高性能信號處理器,TI TMS320C6678集成8核C66x

2022-01-06 11:22:19 1

1

1

1基于TI KeyStone C66x系列多核架構定點/浮點TMS320C6678設計的評估板電源接口和撥碼開關

CPU處理器 TI TMS320C6678是一款TI KeyStone C66x多核定點/浮點DSP處理器,集成了8個C66x核,每核心主頻高達1.0/1.25GHz,支持高性能信號處理

2022-01-10 11:03:29 3

3

3

3創龍TI KeyStone C66x多核定點/浮點TMS320C6678的散熱風扇接口、電源接口和撥碼開關

CPU處理器TI TMS320C6678是一款TI KeyStone C66x多核定點/浮點DSP處理器,集成了8個C66x核,每核心主頻高達1.0/1.25GHz,支持高性能信號處理應用,擁有多種

2022-01-11 13:43:08 1

1

1

1C6678+Zynq-7045的DSP多核IPC通信案例開發

導讀

創龍科技TL6678ZH-EVM是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP,以及Xilinx Zynq-7000系列XC7Z045

2021-09-14 09:54:15 16

16

16

16C6678的ZYNQ OpenAMP雙核ARM通信案例

導讀

創龍科技TL6678ZH-EVM是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP,以及Xilinx Zynq-7000系列XC7Z045

2021-09-14 11:17:14 27

27

27

27TMS320C6678的ZYNQ PS PL異構多核案例開發

導讀

創龍科技TL6678ZH-EVM是一款基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP,以及Xilinx Zynq-7000系列XC7Z045

2021-09-14 14:09:10 15

15

15

15ZYNQ+Linux多核通信案例-開發環境搭建

/XC7Z100SoC處理器設計的高端異構多核評估板,由核心板與底板組成。TMS320C6678每核心主頻可高達1.25GHz,XC7Z045/XC7Z100集成PS端雙核ARMCortex-A9+PL端Kint

2021-12-28 09:25:56 15

15

15

15TI TMS320C6678 DSP多核通信開發說明手冊

前言本文主要介紹TMS320C6678處理器開發中比較常用的兩種多核通信方式:TI-IPC和OpenMP,以及多核編程注意事項。OpenMP依賴于BIOS-MCSDK多核軟件開發包

2022-01-06 09:37:27 29

29

29

29 電子發燒友App

電子發燒友App

評論