從 Vivado 2019.1 版本開(kāi)始,Vivado 綜合引擎就已經(jīng)可以支持增量流程了。這使用戶能夠在設(shè)計(jì)變化較小時(shí)減少總的綜合運(yùn)行時(shí)間。

Vivado IDE 和 Tcl 命令批處理模式都可以啟用此流程。如需了解有關(guān)此流程的詳情,請(qǐng)參閱《Vivado Design Suite 用戶指南:綜合》 (UG901)。

在我們開(kāi)始討論增量綜合之前,我們先來(lái)討論一下一些重要的概念,以便能夠更好地理解該流程。

1. 并行綜合

為了縮短總運(yùn)行時(shí)間,如果設(shè)計(jì)足夠大,并且可以獲益于并行流程,Vivado 綜合即會(huì)啟動(dòng)并行流程。

并行流程會(huì)將設(shè)計(jì)劃分為更小的、由并行進(jìn)程獨(dú)立處理的“RTL 分區(qū)”。

只有當(dāng)設(shè)計(jì)規(guī)模足夠大時(shí),Vivado 綜合才會(huì)決定使用并行流程。設(shè)計(jì)規(guī)模應(yīng)該至少有 5 個(gè) RTL 分區(qū)是大于 10K 實(shí)例大小才行。

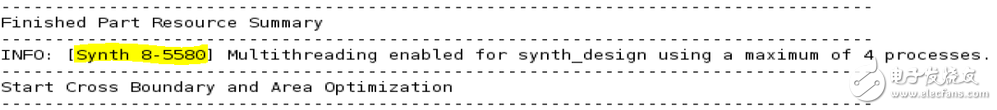

要檢查該工具是否已使用并行流程,您可以在綜合日志中查找“Multithreading enabled for synth_design…”消息。

以下消息確認(rèn)已使用并行流程完成了“Synthesis”,且設(shè)計(jì)與增量綜合運(yùn)行兼容:

"INFO: [Synth 8-5580] Multithreading enabled for synth_design using a maximum of 4 processes." (INFO:[Synth 8-5580] 為 synth_design 啟用多線程,最多使用 4 個(gè)進(jìn)程。)

2. RTL 分區(qū)

Vivado 綜合會(huì)基于實(shí)例將大型設(shè)計(jì)劃分為多個(gè)分區(qū),以便啟用并行流程進(jìn)行綜合。

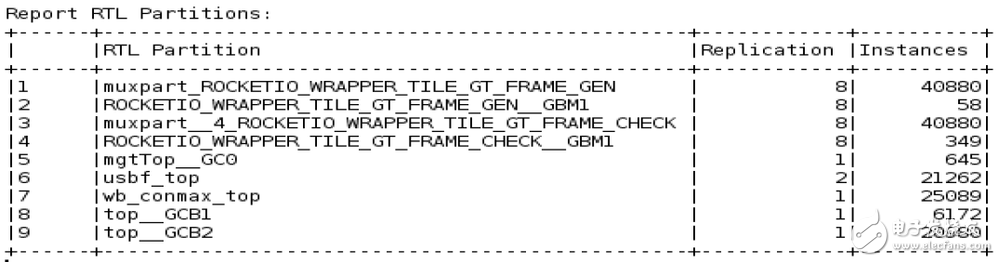

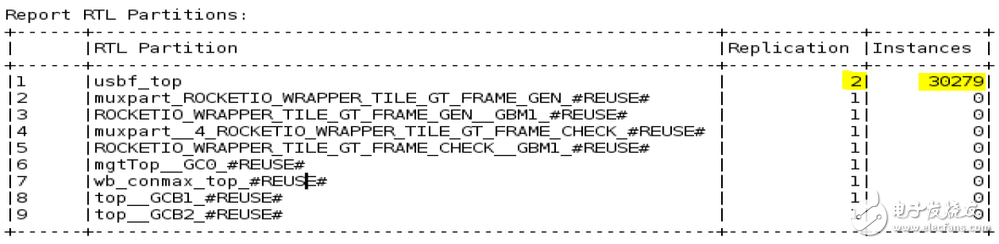

以下快照示出的是工具如何在“Vivado 綜合”日志文件中報(bào)告分區(qū)情況:

RTL 分區(qū)報(bào)告:

+------+----------------------------+------------+----------+

| |RTL Partition |Replication |Instances |

+------+----------------------------+------------+----------+

|1 |Partition_name1 | 1| 31536|

|2 |Partition_name2 | 1| 21130|

|3 |Partition_name3 | 1| 18061|

……..

……..

如果設(shè)計(jì)符合并行綜合的要求,工具就會(huì)將所有分區(qū)寫(xiě)入.runs/synth_1/runme.log 文件。

如果使用的是增量運(yùn)行,這些分區(qū)可以幫助工具識(shí)別哪些分區(qū)已更改并需要重新綜合,并跟蹤哪些分區(qū)是完整的(以保留這些分區(qū))。

注意:作為參考的運(yùn)行結(jié)果中使用并行綜合是進(jìn)行增量綜合的必要條件。如果 50% 或更多的分區(qū)已被更改,這個(gè)工具即會(huì)使用默認(rèn)流程,而不使用增量流程。

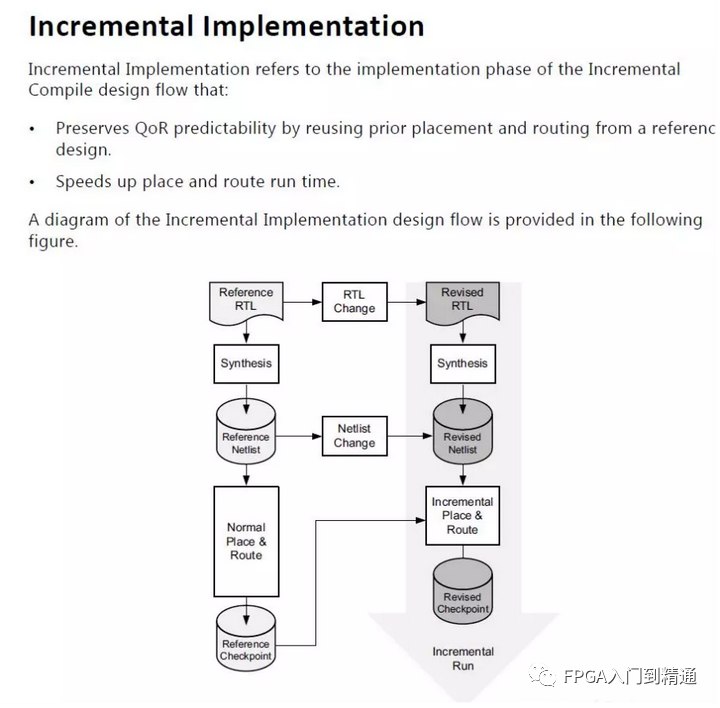

下圖顯示的是增量綜合的流程描述:左側(cè)顯示的是增量流程的輸入集及生成的輸出文件,右側(cè)顯示的是相應(yīng)的命令。

如需了解有關(guān)工程級(jí)和非工程級(jí)流程的詳情,請(qǐng)參閱《Vivado Design Suite 用戶指南:綜合》 (UG901)。

修訂后的設(shè)計(jì)要點(diǎn):

修訂后的設(shè)計(jì)在頂層不應(yīng)有變化。

修訂后的流程與初始“synth_design”命令使用的“Global Synthesis Settings”應(yīng)完全相同。

如需對(duì)較低層級(jí)模塊進(jìn)行工具選項(xiàng)或?qū)傩缘母膭?dòng),則需對(duì)該層級(jí)使用 BLOCK_SYNTH 屬性。如需了解有關(guān) BLOCK_SYNTH 流程的詳情,請(qǐng)參閱《Vivado Design Suite 用戶指南:綜合》 (UG901)。

如果 50% 以上的設(shè)計(jì)已更改(分區(qū)被更改),則該工具會(huì)使用默認(rèn)綜合,而不會(huì)使用增量綜合。

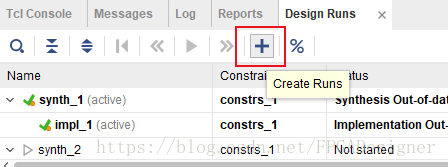

工程流程的增量綜合運(yùn)行示例:

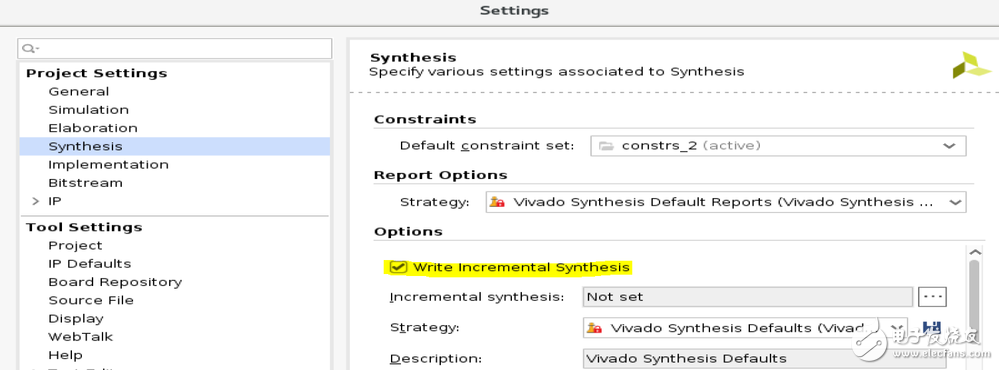

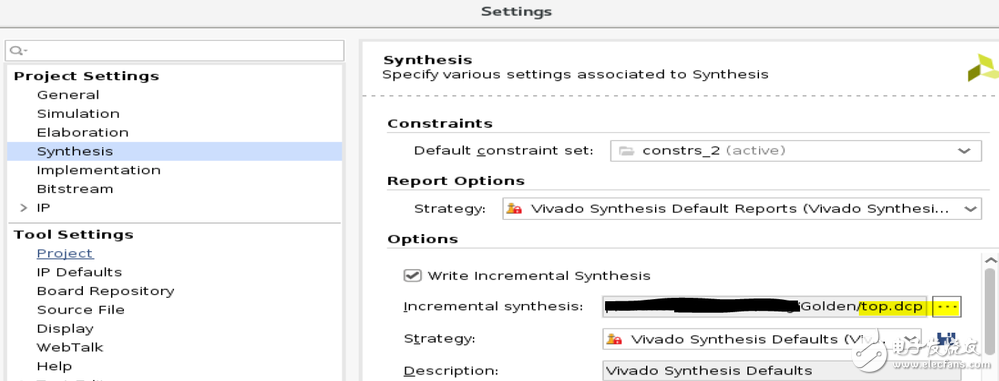

要開(kāi)啟增量綜合流程,在最初對(duì)設(shè)計(jì)進(jìn)行綜合時(shí),請(qǐng)確保選中“Write Incremental Synthesis”選項(xiàng)以便為增量運(yùn)行生成增量 checkpoint。

請(qǐng)通過(guò)“Synthesis Settings”窗口來(lái)設(shè)置此選項(xiàng):

啟動(dòng)綜合后,請(qǐng)查看日志文件以確認(rèn)是否使用了并行綜合。

在綜合日志文件中查找 INFO:Synth 8-5580。

此外,您可以在日志文件中查看打印的“RTL 分區(qū)”詳情,如下所示:

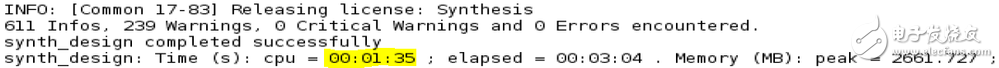

在日志文件的末尾,您可以查看到綜合運(yùn)行所花費(fèi)的總時(shí)間。

完成綜合后,您可以保存生成的、將用于增量流程的 checkpoint 文件,也可以使用工具選項(xiàng)“Automatically use the checkpoint from the previous run”(自動(dòng)使用上一次運(yùn)行的檢查點(diǎn))。

您現(xiàn)在就可以修改設(shè)計(jì)或 RTL 了。

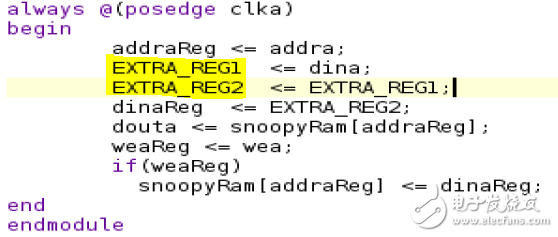

現(xiàn)在我們一起來(lái)看一下一個(gè)簡(jiǎn)單的例子。在這個(gè)示例中,我在數(shù)據(jù)路徑中添加了兩個(gè)寄存器。

下面的屏幕截圖示出的是為增量綜合設(shè)置增量 checkpoint 的示例。

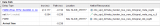

要確認(rèn)該工具是否讀取了增量 checkpoint,請(qǐng)?jiān)谏傻木C合日志文件中查看“Command: read_checkpoint -incremental ./top.dcp”的消息。

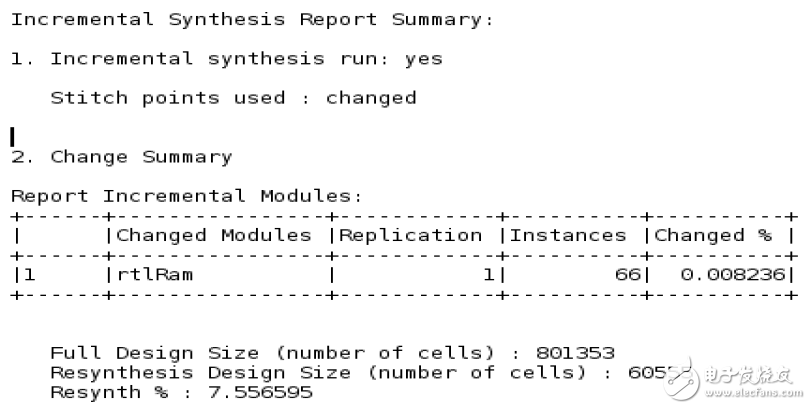

該工具會(huì)分析已更改和未更改的設(shè)計(jì),并報(bào)告摘要(該摘要可幫助用戶了解設(shè)計(jì)改動(dòng)和所需的重新綜合的部分)。

以下是一個(gè)“增量綜合摘要報(bào)告”示例:

變更摘要詳情:

模塊名稱:在設(shè)計(jì)分區(qū)內(nèi) RTL 被更改的模塊。請(qǐng)注意,一個(gè)分區(qū)下可能包含不止一個(gè)模塊。

復(fù)制:所提到模塊的實(shí)例化總數(shù)(在本例中為“rtlRam”)。復(fù)制數(shù)取決于直接實(shí)例化的數(shù)量。

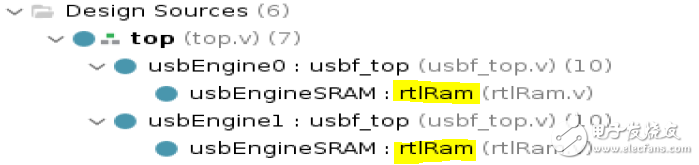

例如(參見(jiàn)下面的屏幕截圖),“rtlRam”僅由“usbf_top”實(shí)例化一次(因此 Replication = 1),即使 usbf_top 被調(diào)用兩次也是如此。

1. 實(shí)例:在 elaboration 階段之前“rtlRam”下的單元/原語(yǔ)數(shù)。在 elaboration 和綜合階段之后,這個(gè)數(shù)字可能會(huì)有所變更。

2. 變更百分比:RTL 變更 (66)/未變更設(shè)計(jì)總數(shù) (801353) * 100 = 0.008%

3. 整個(gè)設(shè)計(jì)的大小:整個(gè)設(shè)計(jì)中的單元總數(shù)(包括已更改和未更改的設(shè)計(jì))

4. 再綜合設(shè)計(jì)的大小:請(qǐng)注意,如果屬于分區(qū)的某一個(gè)模塊中有任何更改,工具即會(huì)重新綜合整個(gè)分區(qū)。在這個(gè)例子中,更改的分區(qū)大小為 30279,在設(shè)計(jì)中被調(diào)用了兩次,因此“Resynthesis Design Size”數(shù)為 ~60555。

此外,工具將重新綜合那些被傳遞了最優(yōu)化的分區(qū),并且“Resynthesis Design Size”的數(shù)量可能會(huì)相應(yīng)地有所變化。

5. 重新綜合設(shè)計(jì)的大小:重新綜合的單元數(shù)= 60555/801353 * 100 = 7.55%

正如您在下面的綜合日志快照中所看到的那樣,與之前 3 分 28 秒的默認(rèn)綜合運(yùn)行時(shí)間相比,增量流程后的運(yùn)行時(shí)間僅為 1 分 35 秒。 7. 重新綜合設(shè)計(jì)的大小:重新綜合的單元數(shù)= 60555/801353 * 100 = 7.55%

設(shè)計(jì)變化較小時(shí),增量綜合是一個(gè)非常強(qiáng)大的功能。請(qǐng)隨時(shí)使用此功能并與我們分享您的反饋。謝謝閱讀!

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論