簡(jiǎn)化采用BPSK(二進(jìn)制相移鍵控)和差分BPSK調(diào)制(也稱為PRK,相位反轉(zhuǎn)鍵控或2PSK)的傳輸(transmit-only)解決方案設(shè)計(jì)。

2019-09-21 08:46:00 6029

6029

鎖相環(huán)英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現(xiàn)在簡(jiǎn)單介紹一下鎖相環(huán)的工作原理。

2023-04-28 09:57:31 4377

4377

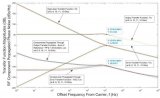

本文是關(guān)于相位噪聲建模、仿真和傳播在鎖相環(huán)中的應(yīng)用的第三部分。文章介紹了相位噪聲的理論和測(cè)量方法,并探討了相位噪聲的分析與建模過程。

2023-10-27 11:42:47 569

569

PLL(鎖相環(huán))電路原理是什么?

2022-01-21 07:03:37

設(shè)計(jì)并調(diào)試鎖相環(huán)(PLL)電路可能會(huì)很復(fù)雜,除非工程師深入了解PLL 理論以及邏輯開發(fā)過程。本文介紹PLL設(shè)計(jì)的簡(jiǎn)易 方法,并提供有效、符合邏輯的方法調(diào)試PLL 問題。 仿真如果不在特定條件下進(jìn)行

2018-10-22 09:45:08

圖解實(shí)用電子技術(shù)叢書,介紹鎖相環(huán)(PLL)電路設(shè)計(jì)與應(yīng)用,供大家參考

2016-06-21 22:51:39

電荷泵鎖相環(huán)的基本原理是什么?電荷泵鎖相環(huán)的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環(huán)的相位噪聲與環(huán)路帶寬關(guān)系是什么?

2021-06-07 06:57:53

概述:LTC6946是一款全集成型 VCO 的高性能、低噪聲、6.39GHz 鎖相環(huán) (PLL),它包括一個(gè)基準(zhǔn)分頻器、具鎖相指示器的相位-頻率檢測(cè)器 (PFD)、超低噪聲充電泵、整數(shù)反饋分頻器和 VCO 輸出...

2021-04-13 06:31:10

鎖相環(huán),而他們都是屬于軟件鎖環(huán)的范疇。在電力仿真軟件中,一般都有PLL模塊,只需要將該模塊應(yīng)用一下即可實(shí)現(xiàn)鎖相環(huán)的功能,即該模塊可輸出系統(tǒng)相角。其實(shí),所謂的PLL模塊就是實(shí)現(xiàn)上面說的這么一團(tuán)東西的,在

2015-01-04 22:57:15

ADI是高性能模擬器件供應(yīng)商,在鎖相環(huán)領(lǐng)域已有十多的的設(shè)計(jì)經(jīng)驗(yàn)。到目前為止,ADI的ADF系列鎖相環(huán)產(chǎn)品所能綜合的頻率可達(dá)8GHz,幾乎能夠涵蓋目前所有無線通信系統(tǒng)的頻段。ADF系列PLL頻率合成器

2018-10-31 15:08:45

ADI是高性能模擬器件供應(yīng)商,在鎖相環(huán)領(lǐng)域已有十多的的設(shè)計(jì)經(jīng)驗(yàn)。到目前為止,ADI的ADF系列鎖相環(huán)產(chǎn)品所能綜合的頻率可達(dá)8GHz,幾乎能夠涵蓋目前所有無線通信系統(tǒng)的頻段。ADF系列PLL頻率合成器

2018-11-06 09:03:16

鎖相環(huán)控制頻率的原理鎖相環(huán)頻率自動(dòng)跟蹤-------用鎖相環(huán)可以確保工作在想要的頻率點(diǎn)上如何理解以下兩段話?鑒相器是相位比較裝置, 它把輸入信號(hào)和壓控振蕩器的輸出信號(hào)的相位進(jìn)行比較, 產(chǎn)生對(duì)應(yīng)

2022-06-22 19:16:46

對(duì)于鎖相環(huán)部分一直有個(gè)疑問:1)鑒相器是根據(jù)輸入信號(hào)和輸出信號(hào)的相位差來輸出一個(gè)電壓,通過LP后,控制壓控振蕩器的頻率輸出2)假如輸入鑒相器的頻率不同,那么電路是如何根據(jù)相位差來判斷頻率之間的差值呢?也就是相位差與頻率差之間的關(guān)系是怎樣的? 有木有相關(guān)的資料可以參考?或是請(qǐng)大牛們解釋下,多謝啦

2017-07-27 09:03:46

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環(huán)的原理,特性與分析所謂鎖相環(huán)路,實(shí)際是指自動(dòng)相位控制電路(APC),它是利用兩個(gè)電信號(hào)的相位誤差,通過環(huán)路自身調(diào)整作用,實(shí)現(xiàn)頻率準(zhǔn)確跟蹤的系統(tǒng),稱該系統(tǒng)為鎖相環(huán)路,簡(jiǎn)稱環(huán)路,通常用PLL 表示。

2008-08-15 13:18:46

第十七章IP核之PLL實(shí)驗(yàn)PLL的英文全稱是Phase Locked Loop,即鎖相環(huán),是一種反饋控制電路。PLL對(duì)時(shí)鐘網(wǎng)絡(luò)進(jìn)行系統(tǒng)級(jí)的時(shí)鐘管理和偏移控制,具有時(shí)鐘倍頻、分頻、相位偏移和可編程

2022-01-18 09:23:55

鎖相環(huán)的頻率與反饋的頻率相等,但是有相位差,譬如輸入與反饋都是15Mhz,但相位差30°,怎么調(diào)節(jié)相位呢?

2015-06-18 08:09:01

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環(huán)PLL原理與應(yīng)用 第一部分:鎖相環(huán)基本原理 一、鎖相環(huán)基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點(diǎn)是:利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位。因鎖相環(huán)可以實(shí)現(xiàn)輸出信號(hào)頻率對(duì)輸入信號(hào)

2022-01-11 06:34:28

鎖相環(huán)使兩個(gè)波型相位相同, 當(dāng)上電時(shí)有時(shí)兩個(gè)波相位相同,有時(shí)不同是什么原因?急需要答案

2016-03-16 20:57:29

如題,AD9957的鎖相環(huán)一直失鎖,不用鎖相環(huán)輸出點(diǎn)頻信號(hào)時(shí)正常的,用了鎖相環(huán)后,PLL_LOCK信號(hào)一直為低,sync_clk輸出信號(hào)也不是穩(wěn)定的周期信號(hào),環(huán)路濾波器的值有點(diǎn)誤差,因?yàn)楝F(xiàn)有的器件沒有那么精確的電容電阻值,問下鎖相環(huán)的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

Actel FPGA PLL鎖相環(huán)的最大能達(dá)到幾倍頻幾分頻?我在網(wǎng)上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊(cè)里面找到資料,想要確認(rèn)一下。

2014-12-04 11:25:15

在我們?cè)O(shè)計(jì)工程中我們會(huì)用到100M,500M等時(shí)鐘,如果我們的晶振達(dá)不到我們就需要倍頻,再上一個(gè)文檔中我們了解到了分頻,可是倍頻我們改怎么做了,這里我們就用了altera的IP核鎖相環(huán)。今天我們將去

2019-06-17 08:30:00

說,上貨。

鎖相環(huán)使用教程

鎖相環(huán)是我們比較常用的IP核之一。PLL的英文全稱是Phase locked loop即鎖相環(huán),是一種反饋電路。具有分頻、倍頻、相位偏移和占空比可調(diào)的功能。在XILINX

2023-06-14 18:09:08

LabVIEW鎖相環(huán)(PLL) 鎖相環(huán)是一種反饋電路,其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。PLL通過比較外部信號(hào)的相位和由壓控晶振(VCXO)的相位來實(shí)現(xiàn)同步的,在比較的過程中,鎖相環(huán)

2022-05-31 19:58:27

原理實(shí)現(xiàn)的頻率及相位的同步技術(shù),其作用是將電路輸出的時(shí)鐘與其外部的參考時(shí)鐘保持同步。當(dāng)參考時(shí)鐘的頻率或相位發(fā)生改變時(shí),鎖相環(huán)會(huì)檢測(cè)到這種變化,并且通過其內(nèi)部的反饋系統(tǒng)來調(diào)節(jié)輸出頻率,直到兩者

2021-11-04 08:57:18

的步長。 PLL系列產(chǎn)品有幾種不同尺寸可供選擇從0.866英寸x 0.63英寸到小至0.5英寸x 0.5英寸。整數(shù)N和分?jǐn)?shù)N低相位噪聲緊湊的尺寸RFS4300A-LF鎖相環(huán)RFS4500A-LF鎖相環(huán)

2021-04-03 17:00:58

概述:SC9256是SILAN半導(dǎo)體公司生產(chǎn)的一款鎖相環(huán)(PLL),大規(guī)模集成電路數(shù)字調(diào)諧系統(tǒng)(DTS),內(nèi)置2個(gè)預(yù)分頻系數(shù)。所有功能都通過3根串行總線控制。這些大規(guī)模集成電路,用于配置高性能的數(shù)字調(diào)諧系統(tǒng)。它采用貼片16腳封裝和雙列16腳封裝。

2021-05-18 06:51:23

概述:SC9257是杭州士蘭微電子生產(chǎn)的一款數(shù)字調(diào)諧系統(tǒng)鎖相環(huán)(PLL FOR DTS)。該SC9257是鎖相環(huán)(PLL)的LSI數(shù)字調(diào)諧系統(tǒng)(DTS)與內(nèi)置的2模數(shù)預(yù)分頻器。所有功能都通過3根串行

2021-05-18 07:27:48

信號(hào)源的任何應(yīng)用的理想選擇,并且利用微帶或陶瓷諧振器拓?fù)浣Y(jié)構(gòu)可提供出色的相位噪聲性能。測(cè)試儀器雷達(dá)系統(tǒng)SFS10500H-LF鎖相環(huán)SFS10625H-LF鎖相環(huán)SFS10640H-LF鎖相環(huán)

2021-04-03 17:05:46

實(shí)驗(yàn)原理:1.PLL概念 PLL的完整英文拼寫為Phase-Locked Loop。即相位鎖定的環(huán)路,也就是常說的鎖相環(huán)。鎖相環(huán)在模擬電路和數(shù)字電路系統(tǒng)中均有廣泛的使用,很多的MCU芯片如STM32

2017-01-05 00:00:52

(ADI公司內(nèi)部PLL電路仿真器)來演示不同電路性能參數(shù)。基本配置:時(shí)鐘凈化電路鎖相環(huán)的最基本配置是將參考信號(hào)(FREF)的相位與可調(diào)反饋信號(hào)(RFIN)F0的相位進(jìn)行比較,如圖1所示。圖2中有一個(gè)在

2019-10-02 08:30:00

什么是鎖相環(huán) (PLL)?一個(gè)鎖相環(huán)PLL電路通常由哪些模塊組成?

2022-01-17 06:01:54

使用ADIsimPLL(ADI公司內(nèi)部PLL電路仿真器)來演示不同電路性能參數(shù)。基本配置:時(shí)鐘凈化電路鎖相環(huán)的最基本配置是將參考信號(hào)(FREF)的相位與可調(diào)反饋信號(hào)(RFIN)F0的相位進(jìn)行比較,如圖1所示

2019-01-28 16:02:54

本文設(shè)計(jì)了一種寬頻率范圍的CMOS鎖相環(huán)(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關(guān)噪聲抵消電路,有效地改善了傳統(tǒng)電路中由于電流失配、電荷共享、時(shí)鐘饋通等導(dǎo)致的相位偏差問題。設(shè)計(jì)了

2019-07-08 07:37:37

需要從哪幾方面去分析電荷泵鎖相環(huán)系統(tǒng)的相位噪聲特性? 才能得出系統(tǒng)噪聲特性的分布特點(diǎn)以及與環(huán)路帶寬的關(guān)系。

2021-04-07 07:11:48

你好,下面提供的是模擬鎖相環(huán)(PLLYSCM)的自定義實(shí)現(xiàn)。器件采用相位頻率檢測(cè)器(PFD)作為相位比較器和基于開關(guān)電容Δ∑調(diào)制器的壓控振蕩器。低通濾波器只需要很少的外部電容器和電阻器

2018-11-07 17:06:05

全數(shù)字鎖相環(huán)的設(shè)計(jì)及分析 1 引 言 鎖相環(huán)是一種能使輸出信號(hào)在頻率和相位上與輸入信號(hào)同步的電路,即系統(tǒng)進(jìn)入鎖定狀態(tài)(或同步狀態(tài))后,震蕩器的輸出信號(hào)與系統(tǒng)輸入信號(hào)之間相差為零,或者保持為常數(shù)

2010-03-16 10:56:10

=rgb(0, 66, 118) !important] 鎖相環(huán)是個(gè)相位誤差控制系統(tǒng)。它比較輸入信號(hào)和壓控振蕩器輸出信號(hào)之間的相位差,從而產(chǎn)生誤差控制電壓來調(diào)整壓控振蕩器的頻率,以達(dá)到與輸入信號(hào)同頻

2019-03-17 06:00:00

,它們的貢獻(xiàn)是控制環(huán)路以及任何頻率轉(zhuǎn)換的函數(shù)。這會(huì)在嘗試評(píng)估組合相位噪聲輸出時(shí)增加復(fù)雜性。本文基于已知的鎖相環(huán)建模方法,以及對(duì)相關(guān)和不相關(guān)貢獻(xiàn)因素的評(píng)估,提出了跟蹤不同頻率偏移下的分布式PLL貢獻(xiàn)的方法。

2019-08-02 08:35:04

、鎖相環(huán)頻率合成器的基本工作原理鎖相環(huán)(PLL)是一個(gè)相位誤差控制系統(tǒng),通過將輸入信號(hào)與壓控振蕩器(VCO)輸出信號(hào)之間的相位進(jìn)行比較,產(chǎn)生相位誤差電壓經(jīng)處理后去調(diào)整壓控振蕩器的相位。當(dāng)環(huán)路鎖定時(shí),輸入信號(hào)

2018-09-06 14:32:13

簡(jiǎn)介設(shè)計(jì)并調(diào)試鎖相環(huán)(PLL)電路可能會(huì)很復(fù)雜,除非工程師深入了解PLL理論以及邏輯開發(fā)過程。本文介紹PLL設(shè)計(jì)的簡(jiǎn)易方法,并提供有效、符合邏輯的方法調(diào)試PLL問題。仿真如果不在特定條件下進(jìn)行仿真

2017-03-17 16:25:46

控制用微處理器的主要性能有哪些?處理器在調(diào)頻(FM)調(diào)諧器中的應(yīng)用是什么?數(shù)字調(diào)諧系統(tǒng)有哪些性質(zhì)?怎樣去設(shè)計(jì)一種基于PLL(鎖相環(huán))合成器的數(shù)字調(diào)諧系統(tǒng)?

2021-08-17 07:03:36

堆疊著鑒相、同相積分、中相積分、濾波等專用名詞。這些概念距離硬件設(shè)計(jì)實(shí)現(xiàn)數(shù)字鎖相環(huán)較遠(yuǎn)。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

數(shù)字鎖相環(huán)設(shè)計(jì)源程序PLL是數(shù)字鎖相環(huán)設(shè)計(jì)源程序, 其中, Fi是輸入頻率(接收數(shù)據(jù)), Fo(Q5)是本地輸出頻率.目的是從輸入數(shù)據(jù)中提取時(shí)鐘信號(hào)(Q5), 其頻率與數(shù)據(jù)速率一致, 時(shí)鐘上升沿鎖定在數(shù)據(jù)的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

最全面最權(quán)威的鎖相環(huán)PLL原理與應(yīng)用資料非常經(jīng)典的資料

2022-12-02 22:39:56

有沒有人用過頻率能達(dá)到300M以上的集成鎖相環(huán)PLL,急求推薦!!

2015-07-30 17:09:19

求助PLL 鎖相環(huán)器件選型指導(dǎo):1) output: Single End clock2) Work Clock: 1Ghz

2018-09-03 11:49:29

大家好,我的課題是要用FPGA做一個(gè)高精度鎖相環(huán)。這個(gè)數(shù)字鎖相環(huán)的工作原理為:正弦模擬信號(hào)通過低通濾波器后,經(jīng)過模數(shù)轉(zhuǎn)換器(ADC)轉(zhuǎn)化為數(shù)字信號(hào),與NCO(數(shù)控振蕩器) 的輸出信號(hào)相乘后濾波,從而

2016-08-15 11:31:56

頻率源可以說是一個(gè)通信系統(tǒng)的心臟,心臟的好壞很大程度上決定著一個(gè)機(jī)體的健康狀況,而鎖相環(huán)又是頻率源的主要組成部分,因此性能優(yōu)異的鎖相環(huán)芯片對(duì)于通信系統(tǒng)來說是非常重要的。鎖相環(huán)的相位噪聲對(duì)電子設(shè)備

2019-06-25 06:22:21

詳細(xì)介紹了具有外部VCO的完整12GHz,超低相位噪聲分?jǐn)?shù)N鎖相環(huán)(PLL)的設(shè)計(jì)。它由高性能小數(shù)N分頻PLL(MAX2880),基于運(yùn)算放大器的有源環(huán)路濾波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

。本文就將為大家介紹在DSP系統(tǒng)中如何有效避免噪聲和EMI產(chǎn)生,對(duì)其中的電源隔離和鎖相環(huán)進(jìn)行介紹。 電源隔離和鎖相環(huán) 如何實(shí)現(xiàn)最佳供電是控制噪聲和輻射的最大挑戰(zhàn)。動(dòng)態(tài)負(fù)載開關(guān)環(huán)境很復(fù)雜,包括的因素

2018-11-30 17:14:11

本文介紹了電荷泵鎖相環(huán)電路鎖定檢測(cè)的基本原理,通過分析影響鎖相環(huán)數(shù)字鎖定電路的關(guān)鍵因子,推導(dǎo)出相位誤差的計(jì)算公式。并以CDCE72010 為例子,通過實(shí)驗(yàn)驗(yàn)證了不合理的電路設(shè)計(jì)或外圍電路參數(shù)是如何影響電荷泵鎖相環(huán)芯片數(shù)字鎖定指示的準(zhǔn)確性。

2021-04-20 06:00:37

您好,我們目前在做一個(gè)調(diào)頻連續(xù)波的雷達(dá),DDS輸出50~60MHz,使用ADI的鎖相環(huán)ADF4108 96倍頻至4.8GHz~5.8GHz,掃頻周期4ms,點(diǎn)頻測(cè)試時(shí)鎖相環(huán)的相位噪聲還可

2018-08-16 07:18:19

您好! 請(qǐng)問ADI是否這樣的鎖相環(huán)芯片,在外參考輸入時(shí)鐘不關(guān)的情況下,開關(guān)鎖相環(huán)芯片,鎖相環(huán)輸出時(shí)鐘相位保持一致,也就是說只要輸入?yún)⒖疾蛔儯_關(guān)鎖相環(huán)芯片,輸出時(shí)鐘相位保持不變,若變,變化范圍是多大, 若無此類鎖相環(huán)芯片,請(qǐng)問ADI是否有此類問題的解決方案。 十分感謝!!

2018-08-31 11:00:43

所謂鎖相環(huán)路,實(shí)際是指自動(dòng)相位控制電路(APC),它是利用兩個(gè)電信號(hào)的相位誤差,通過環(huán)路自身調(diào)整作用,實(shí)現(xiàn)頻率準(zhǔn)確跟蹤的系統(tǒng),稱該系統(tǒng)為鎖相環(huán)路,簡(jiǎn)稱

2008-08-15 12:41:05 332

332 鎖相環(huán)常見問題解答:1 AD公司鎖相環(huán)產(chǎn)品概述2 PLL主要技術(shù)指標(biāo)21 相位噪聲22 參考雜散23 鎖定時(shí)間3 應(yīng)用中常見問題31 PLL芯片接口相關(guān)問題311 參考晶振有哪些要求

2009-09-27 15:43:34 95

95 Skyworks Solutions 的 SKY72302-21 是一款鎖相環(huán),頻率為 400-6100 MHz,相位噪聲 -80

2023-06-12 17:22:25

Skyworks Solutions 的 SKY74038-21 是一款鎖相環(huán),頻率為 100-2600 MHz

2023-06-12 17:24:47

Skyworks Solutions 的 SKY72301-22 是一款鎖相環(huán),頻率為 100-1000 MHz,相位噪聲 -96

2023-06-12 17:29:24

Skyworks Solutions 的 SKY72300-362 是一款鎖相環(huán),頻率為 100-2100 MHz,相位噪聲 -91

2023-06-12 17:30:57

--- 現(xiàn)代電子系統(tǒng)和設(shè)備都離不開相位噪聲測(cè)試的要求,因?yàn)楸菊?b class="flag-6" style="color: red">相位噪聲影響著調(diào)頻、調(diào)相系統(tǒng)的最終信噪比,惡化某些調(diào)幅檢波器的性能;限制頻移鍵控(FSK) 和相移鍵控(PSK)

2010-10-08 15:44:48 25

25 鎖相環(huán)原理

鎖相環(huán)路是一種反饋電路,鎖相環(huán)的英文全稱是Phase-Locked Loop,簡(jiǎn)稱PLL。其作用是使得電路上的時(shí)鐘和某一外部時(shí)鐘的相位同步。因鎖相環(huán)可以

2007-08-21 14:46:04 4879

4879 鎖相環(huán)CD4046應(yīng)用

鎖相的意義是相位同步的自動(dòng)控制,能夠完成兩個(gè)電信號(hào)相位同步的自動(dòng)控制閉環(huán)系統(tǒng)叫做鎖相環(huán),簡(jiǎn)稱PLL。它廣泛應(yīng)用于廣播通信、

2009-03-18 15:11:18 2024

2024

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

PLL的概念

我們所說的PLL。其

2010-03-23 10:47:48 6005

6005 頻移鍵控 (FSK)和相移鍵控 (PSK) 調(diào)制方案廣泛用于數(shù)字通信、雷達(dá)、RFID以及多種其他應(yīng)用。

2012-11-02 11:02:49 5837

5837 利用鎖相環(huán)的等效噪聲模型,重點(diǎn)分析電荷泵鎖相環(huán)系統(tǒng)的相位噪聲特性,得出系統(tǒng)噪聲特性的分布特點(diǎn)以及與環(huán)路帶寬的關(guān)系。

2012-11-22 10:44:47 16470

16470 如何設(shè)計(jì)并調(diào)試鎖相環(huán)(PLL)電路 pdf

2016-01-07 16:20:08 0

0 也許你也會(huì)跟我一樣認(rèn)為典型數(shù)據(jù)表中的某些規(guī)格難以理解,這是因?yàn)槠渲泻w了一些你不太熟悉的隱含慣例。對(duì)許多RF系統(tǒng)工程師而言,其中一種規(guī)格便是鎖相環(huán)(PLL)中的相位噪聲。當(dāng)信號(hào)源被用作本機(jī)振蕩器(LO)或高速時(shí)鐘時(shí),相位噪聲性能對(duì)滿足系統(tǒng)要求起到了重要作用。

2017-04-08 08:08:01 6632

6632

PLL(Phase Locked Loop),也稱為鎖相環(huán)路(PLL)或鎖相環(huán),它能使受控振蕩器的頻率和相位均與輸入?yún)⒖夹盘?hào)保持同步,稱為相位鎖定,簡(jiǎn)稱鎖相。

2017-05-22 10:11:40 8672

8672

利用相移鍵控(PSK)與頻移鍵控(FSK)的調(diào)頻傳輸方案 以節(jié)省電力,并保持氣道清晰,F(xiàn)M廣播芯片可以用作載體上,載波關(guān)閉來傳輸數(shù)據(jù)。就像一個(gè)框UART數(shù)據(jù)包,由于沒有信號(hào)的無效狀態(tài)和信號(hào)的存在開始

2017-09-12 19:32:45 4

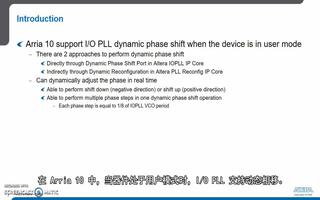

4 如何在 Arria 10 中實(shí)現(xiàn) I/O 鎖相環(huán) (PLL) 動(dòng)態(tài)相移

2018-06-20 04:56:00 3156

3156

通過演示簡(jiǎn)要介紹鎖相環(huán)(PLL)中可實(shí)現(xiàn)的領(lǐng)先相位噪聲和雜散性能。

2019-05-21 06:23:00 5321

5321 的相位變換,提出了一種基于鎖相環(huán)(PLL)的QPSK調(diào)制器。由于采用了三輸入異或門和求和電路,該系統(tǒng)中的鎖相環(huán)電路不同于傳統(tǒng)的鎖相環(huán)電路。利用這些附加組件,所提出的PLL在QPSK信號(hào)中提供連續(xù)的相位變化。因此,當(dāng)使用所述電路時(shí),傳輸QPSK信號(hào)所需的帶寬

2020-05-15 08:00:00 3

3 基于FPGA的二進(jìn)制相移鍵控設(shè)計(jì)方案

2021-05-28 09:36:50 11

11 鎖相環(huán)路是一種反饋控制電路,簡(jiǎn)稱鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點(diǎn)是:利用外部輸入的參考信號(hào)控制環(huán)路內(nèi)部振蕩信號(hào)的頻率和相位。

2022-03-29 09:54:55 11472

11472 PLL是指鎖相環(huán),是一種用于控制頻率和相位的電路,它可以將一個(gè)輸入信號(hào)的頻率和相位轉(zhuǎn)換成另一個(gè)輸出信號(hào)的頻率和相位,從而實(shí)現(xiàn)頻率和相位的控制。

2023-02-14 17:19:51 6947

6947 鎖相環(huán) (PLL) 在當(dāng)今的高科技世界中無處不在。幾乎所有商業(yè)和軍用產(chǎn)品都在其運(yùn)行中使用它們,相位(或 PM)噪聲是一個(gè)主要問題。

2023-02-21 17:44:39 913

913 pll鎖相環(huán)倍頻的原理? PLL鎖相環(huán)倍頻是一種重要的時(shí)鐘信號(hào)處理技術(shù),廣泛應(yīng)用于數(shù)字系統(tǒng)、通信系統(tǒng)、計(jì)算機(jī)等領(lǐng)域,具有高可靠性、高精度、快速跟蹤等優(yōu)點(diǎn)。PLL鎖相環(huán)倍頻的原理涉及到鎖相環(huán),倍頻器

2023-09-02 14:59:24 1508

1508 PLL和DLL都是鎖相環(huán),區(qū)別在哪里?? PLL和DLL都是常用的鎖相環(huán)(Phase Locked Loop)結(jié)構(gòu),在電路設(shè)計(jì)中具有廣泛的應(yīng)用。它們的共同作用是將輸入信號(hào)和參考信號(hào)的相位差控制在一定

2023-09-02 15:06:31 1532

1532 pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個(gè)特定頻率的輸入信號(hào)轉(zhuǎn)換為固定頻率的輸出信號(hào)。PLL鎖相環(huán)的三種配置模式分別為

2023-10-13 17:39:48 1102

1102 什么是鎖相環(huán)?PLL和DLL都是鎖相環(huán)區(qū)別在哪里? 鎖相環(huán)(Phase Locked Loop,PLL)是一種基于反饋的控制系統(tǒng),用于提供穩(wěn)定的時(shí)鐘信號(hào)。它可以將參考信號(hào)的相位與輸出信號(hào)的相位進(jìn)行

2023-10-13 17:39:53 667

667 )常作為電力系統(tǒng)中的一種重要控制策略。三相鎖相環(huán)(PLL)是一種基于鎖相環(huán)原理的控制系統(tǒng),它能夠?qū)⑤斎氲娜嚯妷盒盘?hào)轉(zhuǎn)化成可用于控制其他系統(tǒng)的數(shù)字信號(hào)。 三相鎖相環(huán)(PLL)的作用是使得輸出電壓與輸入電壓之間保持恒定的相位差,這樣可以得到一個(gè)相對(duì)穩(wěn)定的輸出電壓。

2023-10-13 17:39:56 482

482 鎖相環(huán)(PLL)基本原理 當(dāng)鎖相環(huán)無法鎖定時(shí)該怎么處理的呢? 鎖相環(huán)(Phase Locked Loop, PLL)是一種電路系統(tǒng),它可以將輸入信號(hào)的相位鎖定到參考信號(hào)的相位。在鎖相環(huán)中,反饋回路

2023-10-23 10:10:15 1353

1353 鎖相環(huán)在相位檢測(cè)中的應(yīng)用? 鎖相環(huán)(PLL)是一種電子技術(shù)中廣泛應(yīng)用的電路,用于調(diào)整一個(gè)輸出信號(hào)的相位來精確匹配一個(gè)參考信號(hào)。鎖相環(huán)在各種不同的應(yīng)用領(lǐng)域都有著廣泛的應(yīng)用,例如通信系統(tǒng)、控制系統(tǒng)、測(cè)量

2023-10-29 11:35:19 356

356 如何用鎖相環(huán)恢復(fù)載波同步信號(hào)? 鎖相環(huán)(PLL)是一種電路,可用于恢復(fù)和跟蹤輸入信號(hào)的頻率和相位。PLL常用于電信、通訊和控制系統(tǒng)中,以恢復(fù)和跟蹤載波同步信號(hào)。本文將介紹鎖相環(huán)如何恢復(fù)載波同步信號(hào)

2023-10-30 10:56:38 356

356 鎖相環(huán)是保證相位一致,還是相位差一致?鎖相環(huán)的輸入輸出相位一致嗎? 鎖相環(huán)(PLL)是一種回路控制系統(tǒng),用于保持輸出信號(hào)的相位與參考信號(hào)的相位之間的恒定關(guān)系。簡(jiǎn)單來說,鎖相環(huán)的目的是保證相位一致

2024-01-31 15:45:48 202

202

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論