對(duì)于FPGA開發(fā)而言,仿真是開發(fā)流程中必不可少的一步,也是非常重要的一步,仿真是將RTL代碼模擬運(yùn)行,得到module中信號(hào)波形,再進(jìn)行功能分析的過(guò)程。強(qiáng)大的功能與速度兼具的modelsim仿真就是

2020-09-30 13:52:33 8686

8686

我們?cè)赪indows系統(tǒng)下使用Vivado的默認(rèn)設(shè)置調(diào)用第三方仿真器比如ModelSim進(jìn)行仿真時(shí),一開始仿真軟件都會(huì)默認(rèn)在波形界面中加載testbench頂層的信號(hào)波形

2023-09-13 09:23:49 712

712

直接在modelsim軟件內(nèi)執(zhí)行.do文件進(jìn)行仿真,不通過(guò)vivado調(diào)用modelsim,vivado僅用于生成IP核。

2023-12-04 18:26:34 477

477

寫了個(gè)程序里面調(diào)用了幾個(gè)模塊,quartus11.0編譯時(shí)沒(méi)有報(bào)錯(cuò),但在modelsim仿真時(shí)提示一些信號(hào)already declared in this scope ,看了下程序,這些信號(hào)是子模塊的一些輸入輸出信號(hào),但在主程序中沒(méi)有重復(fù)定義啊,只是對(duì)其做了必要的變量申明而已。希望能幫忙看下。

2013-05-09 18:49:21

ModelSim 電子系統(tǒng)分析及仿真ModelSim是優(yōu)秀的HDL仿真軟件之一,支持VHDL 和Verilog混合仿真的仿真器。這篇文章是以ModelSim6.1f軟件為例的,包括基礎(chǔ)知識(shí)、菜單命令

2018-09-11 15:10:27

ModelSim軟件概述本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt提到FPGA的仿真驗(yàn)證,雖然有眾多

2019-04-11 06:35:22

在使用 ISE 軟件進(jìn)行仿真,仿真工具是 Modelsim,提示錯(cuò)誤,錯(cuò)誤詳情如下: > unisim (ERROR: Library path "d:/Xilinx/14.3

2015-01-19 14:12:08

Modelsim庫(kù)的概念,分析一下Quartus II自動(dòng)完成仿真的代碼,最后能自己寫一些簡(jiǎn)單的do文件利用我們添加的仿真庫(kù)自動(dòng)進(jìn)行時(shí)序仿真。前兩個(gè)部分是簡(jiǎn)單的操作,掌握其中一個(gè)部分即可進(jìn)行時(shí)序仿真。最后

2012-02-01 11:37:40

各位,小弟最近遇到一個(gè)很奇怪的問(wèn)題。我在使用modelsim進(jìn)行仿真時(shí),無(wú)論是通過(guò)quartus調(diào)用還是直接運(yùn)行modelsim,都會(huì)遇到提示:“error loading design“,從而仿真

2015-08-30 22:14:39

在Modelsim里將庫(kù)和工程文件都添加進(jìn)來(lái),仿真的時(shí)候發(fā)現(xiàn),只能看到testbench里的變量值,無(wú)法看到各個(gè)功能模塊的輸入輸出信號(hào)的值,請(qǐng)問(wèn)大家是怎么做的呢?

2015-10-12 10:41:08

求助:有人用過(guò)modelsim仿真軟件嗎?有這方面的書籍或資料嗎?[em65]

2008-10-22 16:36:55

虛心請(qǐng)假大家了———— modelsim SE啟動(dòng)仿真后,軟件就會(huì)自動(dòng)關(guān)閉,單獨(dú)運(yùn)行的時(shí)候就沒(méi)有什么問(wèn)題。卸載重裝過(guò)還是一樣的問(wèn)題,同樣的操作在別人的軟件上不會(huì)出現(xiàn),應(yīng)該不是代碼的問(wèn)題。淚奔呢。。。。。。請(qǐng)求高人指出解決辦法,先謝謝謝謝~~~~~~

2013-06-21 19:49:48

我在用quartus調(diào)用modelsim仿真波形時(shí)出現(xiàn)波形窗口,但沒(méi)有信號(hào)名也沒(méi)有波形,求高手給指點(diǎn)下

2013-08-27 11:12:03

請(qǐng)問(wèn)一下在ISE14.6中編譯完modelsim10.0a,在用modelsim進(jìn)行仿真時(shí)會(huì)閃退是怎么回事,有什么解決辦法?期待熱心的你給以指教!

2016-05-19 21:10:18

modelsim仿真軟件下載鏈接親測(cè)能用

2018-07-10 14:36:18

modelsim仿真fftip核方法:重點(diǎn)有3:1,添加庫(kù)文件方式正確2,添加編譯文件,要包括.vo文件3,仿真時(shí)要重新再添加一下庫(kù)文件

2013-05-12 14:05:12

驅(qū)動(dòng)的影子(只是 system_tb.v 里面添加的仿真條件有作用,C驅(qū)動(dòng)完全沒(méi)起作用),感覺(jué)可能是elf文件沒(méi)有關(guān)聯(lián)上,但是我從編譯仿真庫(kù)到關(guān)聯(lián)仿真庫(kù)再到最后的modelsim仿真,都是按照網(wǎng)上諸多的教程貼來(lái)的啊,別人都能成功了,為什么我的就是不行呢?請(qǐng)論壇的各位大神帶我走出苦海,萬(wàn)分感謝!

2015-04-20 12:02:09

如題,最近看很多modelsim的資料,很多時(shí)候仿真要添加仿真原型文件,比較困擾的是怎么選擇仿真原型文件,不同功能怎么對(duì)應(yīng)相應(yīng)的仿真原型文件呢,我發(fā)現(xiàn)很多資料都沒(méi)講清楚。

2014-03-09 22:31:36

最近用modelsim軟件時(shí),程序編譯成功,但是仿真時(shí)候總會(huì)彈出vsimk.exe停止工作,接著軟件卡死。求助各位高手指導(dǎo)

2012-10-15 19:03:39

我要手動(dòng)添加輸入信號(hào),但是右鍵點(diǎn)要設(shè)置的輸入信號(hào),為什么沒(méi)有create那個(gè)選項(xiàng)

2018-04-07 10:32:22

請(qǐng)問(wèn) modelsim一仿真就自動(dòng)關(guān)閉是怎么回事?使用的是 從ALTERA官網(wǎng)下載的Quartus II 網(wǎng)絡(luò)版軟件 ,安裝之后就包含了modelsim10.1d(Quartus Ⅱ13.0),按照

2013-05-28 22:06:35

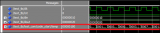

items in region”,添加觀測(cè)信號(hào)給波形窗口,如下圖所示: 7.選擇軟件左下方“wave”,運(yùn)行仿真,如下圖所示: 以上就是GUI界面的仿真步驟了。二.腳本方式的仿真步驟我個(gè)人是不喜歡

2018-03-29 11:01:27

Altera和Xilinx Modelsim仿真庫(kù)Altera和Xilinx Modelsim仿真庫(kù) 我們通常使用modelsim軟件作為仿真工具,不同階段的仿真使用不同的庫(kù)文件,在開始仿真前將庫(kù)

2012-08-10 18:31:02

FPGA 中的Block Diagram能直接聯(lián)合Modelsim仿真嗎?如果不使用Block Diagram,是能夠正常聯(lián)合Modelsim仿真的,但是使用了Block Diagram模式后,配置一樣,但是總是報(bào)錯(cuò)

2016-10-08 17:12:26

,通常用modelsim仿真(雖然這個(gè)軟件的bug層出不出)。這一次主要介紹一下modelsim軟件常見(jiàn)的幾個(gè)問(wèn)題。1.常有人問(wèn)如何查看中間變量的的仿真結(jié)果?有人說(shuō)直接把中間變量設(shè)為一個(gè)輸出端口,當(dāng)然

2017-04-15 21:46:29

ModelSim軟件概述本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 提到FPGA的仿真驗(yàn)證,雖然有眾多

2015-08-31 18:31:56

在我們用ModelSim仿真的時(shí)候經(jīng)常是修改一點(diǎn)一點(diǎn)修改代碼,這樣會(huì)造成一個(gè)無(wú)奈的操作循環(huán):修改代碼--->編譯代碼--->仿真設(shè)置--->進(jìn)入仿真頁(yè)面--->添加需要觀察

2019-06-03 09:11:11

Labview中while循環(huán)的移位寄存器怎么能只添加框架左邊的,右邊不添加。我的是2013版本,在框架上添加移位寄存器就左右成對(duì)出現(xiàn)了。右側(cè)的只需要一個(gè),剩下的不需要。

2018-03-07 10:46:20

,目前支持ModelSim和QuestaSim,本教程選擇ModelSim;

【Language】:仿真庫(kù)用的語(yǔ)言; 【Library】:選擇 usim 則是 GTP 前仿庫(kù),vsim 則是 VOP 后

2023-06-26 10:45:30

目的:使用ISE調(diào)用modelsim進(jìn)行仿真,并使用debussy查看仿真波形準(zhǔn)備:安裝ISE、Modelsim和Debussy軟件將C:\modeltech_6.5a\modelsim.ini設(shè)置

2012-03-08 15:27:01

.mif 和 .hex。.mif文件是用來(lái)給Quautus綜合網(wǎng)表用的,而.hex可以被用來(lái)作為modelsim仿真的數(shù)據(jù)輸入。換句話說(shuō)modelisim對(duì).mif文件不支持,而只對(duì).hex文件支持

2014-03-06 16:22:21

PDS 和仿真軟件 Modelsim 放在 B 盤),文件列 表如下圖所示:使用 Modelsim 軟件需要添加 License,請(qǐng)多多支持正版。至此,Modelsim 安裝完成。學(xué)習(xí)中,可以自動(dòng)查找

2023-04-30 17:24:03

前言 Modelsim是最常用的HDL語(yǔ)言仿真軟件,一般fpga開發(fā)環(huán)境都會(huì)集成modelsim或者可以聯(lián)合modelsim進(jìn)行仿真。PDS也可以聯(lián)合modelsim進(jìn)行仿真,這也說(shuō)明PDS是一款

2023-02-06 22:36:13

Mentor公司的ModelSim是業(yè)界最優(yōu)秀的HDL語(yǔ)言仿真軟件,它能提供友好的仿真環(huán)境,是業(yè)界唯一的單內(nèi)核支持VHDL和Verilog混合仿真的仿真器。它采用直接優(yōu)化的編譯技術(shù)、Tcl/Tk技術(shù)

2016-09-05 21:29:19

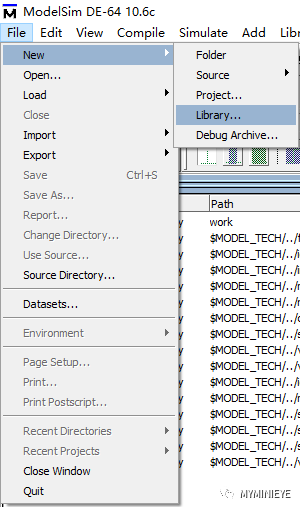

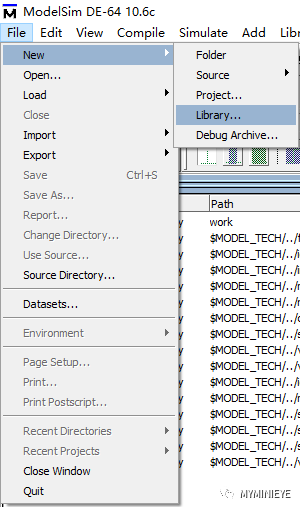

中新建一個(gè)工程,要用到兩個(gè)文件,Verilog仿真文件與Testbench仿真文件。新建一個(gè)文件夾,將兩個(gè)文件復(fù)制到其中。打開ModelSim軟件,菜單欄:File à New à Project輸入

2016-09-06 21:06:57

再來(lái)使用一下ModelSim仿真工具吧。在Assignments --> Settings -->EDA Tool Settings中設(shè)置仿真軟件為ModelSim-Altera ,語(yǔ)言

2016-10-02 14:34:41

基于流水燈的ModelSIm軟件仿真為例子在工程文件sim下新建一個(gè)文件夾用來(lái)存放仿真文件代碼然后新建Modelsim文件存放在工程文件sim下 然后把在quartus II 寫的代碼從rtl文件夾

2020-01-13 16:34:57

,只需要在modelism的“Transcript”命令行中輸入“doxxx_tb_simulate.do”命令回車執(zhí)行即可完成已修改程序的編譯,從此修改完源程序之后就無(wú)需關(guān)閉modelsim軟件重新打開。

2018-10-16 19:43:20

我在使用ISE軟件里面cordic算法ip核,想產(chǎn)生一個(gè)正弦波。在modelsim仿真波形時(shí),仿真結(jié)果如下圖1,我想找到波形鏈接的點(diǎn),我的tb程序里面是module cordic_tb

2015-05-28 20:54:41

我已經(jīng)照網(wǎng)上的教程添加了convert_hex2ver.dll文件到WIN32目錄下,并且修改了modelsin.ini文件, 修改格式如下,但是用modelsim仿真出來(lái)的波形還是一條紅線請(qǐng)問(wèn)一下是我設(shè)置出錯(cuò)了 還是別的地方搞錯(cuò)了,為什么一直仿真不出來(lái)ROM的數(shù)據(jù)?謝謝了!

2014-10-30 18:02:24

時(shí)就能看到像在功能仿真的工程文件層次結(jié)構(gòu),可以找到定義的內(nèi)部信號(hào)。因?yàn)樵谧龊蠓聲r(shí),源文件中的信號(hào)名稱已經(jīng)沒(méi)有了,被映射為軟件綜合后自己生成的信號(hào)名,觀察起來(lái)很不方便。這個(gè)設(shè)置與ISE里綜合右鍵屬性

2012-03-01 11:46:29

在ModelSim中添加xilinx仿真庫(kù)的具體步驟

2018-09-12 14:58:15

,Modelsim還能夠與c語(yǔ)言一起對(duì)HDL設(shè)計(jì)文件實(shí)現(xiàn)協(xié)同仿真。同時(shí),相對(duì)于大多數(shù)的HDL仿真軟件來(lái)說(shuō),Modelsim在仿真速度上也有明顯優(yōu)勢(shì)。這些特點(diǎn)使Modelsim越來(lái)越受到EDA設(shè)計(jì)者、尤其是FPGA

2019-06-06 05:00:38

延遲,能較好地反映芯片的實(shí)際工作情況。選定了器件分配引腳后在做后仿真。二.仿真前的準(zhǔn)備工作:這里將使用Quartus II13.1和Modelsim Ae進(jìn)行功能仿真(Modelsim Ase 版本

2015-11-29 21:35:23

ModelSim中新建項(xiàng)目,建立work庫(kù),在庫(kù)中添加需要仿真的文件和Altera的系統(tǒng)庫(kù)文件altera_mf.v和220model.v,一起編譯。編譯成功后即可添加波形仿真了

2012-02-29 10:43:17

` 本帖最后由 eehome 于 2013-1-5 09:54 編輯

ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見(jiàn)

2012-02-24 21:51:12

本帖最后由 diangongshi 于 2012-2-24 21:42 編輯

蓋住了版本號(hào),為的是告訴大家,這個(gè)各個(gè)版本通用。在使用ModelSim軟件對(duì)Xilinx ISE進(jìn)行后仿真時(shí),需要

2012-02-24 21:40:17

仿真波形不對(duì),可能需要查看中間信號(hào)以便定位錯(cuò)誤,這時(shí)用add wave命令添加中間信號(hào)后,需要重新run一次,才能看到這些中間信號(hào)的值。而采用Debussy查看ModelSim生成的.fsdb文件的話

2012-03-01 11:24:11

關(guān)于I2C總線,I2C總線從機(jī)的應(yīng)答信號(hào)是不是不能用modelsim直接仿真出哦?所謂從機(jī)將SDA拉低的應(yīng)答信號(hào),是不是要在實(shí)際的電路里才有,要么就用軟件編程模擬從機(jī)?反正我直接用編I2C總線寫時(shí)序

2014-04-15 13:04:11

繼續(xù)添加其他輸入波形,出現(xiàn)下面的結(jié)果。前面出現(xiàn)的紅點(diǎn)表示該波形是可編輯的。后面的操作與用testbench文本仿真的方法相同 。

圖25 仿真波形

4.2 觀察特定信號(hào)波形

如果設(shè)計(jì)者只想查看

2024-03-19 16:40:15

Modelsim不報(bào)錯(cuò)了,但仿真信號(hào)依舊出不來(lái)。初學(xué)者,,跪求高人指點(diǎn),是Quartus中哪里未設(shè)置好,還是生成.vo文件過(guò)程不正確?先在這里謝謝大家了!

2018-01-22 21:51:35

Edition,就無(wú)需許可證文件。接下來(lái)選擇安裝目錄,注意不要出現(xiàn)中文。安裝完成后就可以正常使用Modelsim軟件進(jìn)行仿真,進(jìn)入Modelsim時(shí)正常的界面如下:原作者:語(yǔ)雀

2022-06-28 17:15:19

MODELsim是MODEL Technology(Mentor Graphics的子公司)的HDL硬件描述語(yǔ)言仿真軟件,可以實(shí)現(xiàn)VHDL、Verilog以及VHDL-Verilog混合設(shè)計(jì)的仿真。除此之外

2019-05-15 07:00:10

在Modelsim SE中如何指定altera仿真庫(kù)

2008-09-09 17:50:04 44

44 本文主要描述了如何在 QUARTUS II 中輸入程序文件,生成網(wǎng)表及標(biāo)準(zhǔn)延時(shí)文件,然后通過(guò)MODELSIM 進(jìn)行功能仿真與后仿真的過(guò)程,主要為圖解,含全部代碼及仿真波形。

2009-07-22 15:44:53 0

0 我把我用到的軟件說(shuō)明一下。如果你發(fā)現(xiàn)根據(jù)我的操作,你還是解決不了ModelSim后仿真的問(wèn)題,那就可能是軟件版本的問(wèn)題。

2009-07-22 15:46:27 0

0 當(dāng)我們使用QuartusII,但是大多數(shù)朋友都習(xí)慣用Modelsim SE來(lái)做仿真,由于Quaruts有很多本身器件的特色,所以造成了在仿真上的麻煩,當(dāng)然網(wǎng)路上也有一些講解,但是都是不太系統(tǒng),特

2010-06-24 17:57:18 216

216 1 前言 協(xié)同仿真就是利用仿真工具提供的外部接口,用其它程序設(shè)計(jì)語(yǔ)言(非HDL語(yǔ)言,如c語(yǔ)言等)編程,用輔助仿真工具進(jìn)行仿真。Modelsim提供了與c語(yǔ)言的協(xié)同

2010-06-07 08:33:59 1124

1124

ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但推薦大家只對(duì)一種語(yǔ)言

2011-04-19 20:52:46 151

151 第一章 1、 關(guān)于 Modelsim中庫(kù)的編譯 2、 如何在modelsim中指定Altera的仿真庫(kù) 3、 Modelsim波形文件 4、 后仿真時(shí),是不是要對(duì)復(fù)位信號(hào)GSR/GTR做特別特殊處理?為什么? 5、 功能仿真加STA能不

2011-05-26 15:48:05 0

0 ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但推薦大家只對(duì)一種語(yǔ)言

2011-05-27 16:41:59 132

132 Altera ModelSim 6.5仿真入門教程,需要的可自行下載。 平臺(tái) 軟件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 內(nèi)容 1 設(shè)計(jì)流程 使用ModelSim仿真的基本流程為: 圖1.1 使用 ModelSim仿真的基本

2012-08-15 15:40:24 255

255 用ModelSim 進(jìn)行功能仿真,進(jìn)行功能仿真首先要檢查設(shè)計(jì)的語(yǔ)法是否正確;其次檢查代碼是否達(dá)到設(shè)計(jì)的功能要求。下文主要介紹仿真步驟和測(cè)試激勵(lì)的加載。

2012-11-13 15:35:59 8536

8536 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 本章為ModelSim的初級(jí)教程,讀者讀完本章可以較為熟練的使用ModelSim進(jìn)行設(shè)計(jì)仿真,本章沒(méi)有也不可能涉及ModelSim的各個(gè)方面,要想全面的掌握ModelSim可以參閱軟件文檔。

2015-12-24 18:29:37 0

0 在我們用ModelSim仿真的時(shí)候經(jīng)常是修改一點(diǎn)一點(diǎn)修改代碼,這樣會(huì)造成一個(gè)無(wú)奈的操作循環(huán):修改代碼--->編譯代碼--->仿真設(shè)置--->進(jìn)入仿真頁(yè)面--->添加需要觀察的波形--->運(yùn)行仿真

2017-02-11 15:25:07 10138

10138

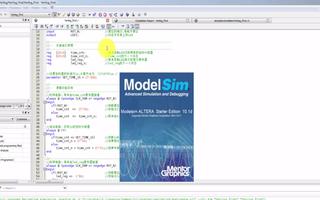

modelsim仿真詳細(xì)過(guò)程(功能仿真與時(shí)序仿真).ModelSim不僅可以用于數(shù)字電路系統(tǒng)設(shè)計(jì)的功能仿真,還可以應(yīng)用于數(shù)字電路系統(tǒng)設(shè)計(jì)的時(shí)序仿真。 ModelSim的使用中,最基本的步驟包括創(chuàng)建工程、編寫源代碼、編譯、啟動(dòng)仿真器和運(yùn)行仿真五個(gè)步驟。

2017-12-19 11:14:11 63885

63885

1、 運(yùn)行ModelSim,如果上一次使用ModelSim建立過(guò)工程,這時(shí)候會(huì)自動(dòng)打開 上一次所建立的工程; 2、 點(diǎn)擊File-New-Project,在Project Name中我們輸入建立

2018-06-22 10:13:00 3122

3122 ModelSim PE Student Edition 是在由ModelSim PE Student Edition 6.3a開發(fā)類別 Education Shareware 軟件。 最新版

2018-04-17 18:03:46 257

257 ModelSim不僅可以用于數(shù)字電路系統(tǒng)設(shè)計(jì)的功能仿真,還可以應(yīng)用于數(shù)字電路系統(tǒng)設(shè)計(jì)的時(shí)序仿真。 ModelSim的使用中,最基本的步驟包括創(chuàng)建工程、編寫源代碼、編譯、啟動(dòng)仿真器和運(yùn)行仿真五個(gè)步驟,仿真流程如圖1所示:

2018-12-29 11:35:14 9227

9227 本文檔的主要內(nèi)容詳細(xì)介紹的是modelsim仿真使用教程資料免費(fèi)下載。

2019-04-02 08:00:00 6

6 筆者一直以來(lái)都在糾結(jié),自己是否要為仿真編輯相關(guān)的教程呢?一般而言,Modelsim等價(jià)仿真已經(jīng)成為大眾的常識(shí),但是學(xué)習(xí)仿真是否學(xué)習(xí)Modelsim,筆者則是一直保持保留的態(tài)度。筆者認(rèn)為,仿真

2019-04-30 18:24:00 23

23 本文檔的主要內(nèi)容詳細(xì)介紹的是HDL仿真軟件Modelsim的安裝教程資料免費(fèi)下載。安裝教程很詳細(xì),大家一步步來(lái)安裝基本都能安裝好。

2019-05-28 08:00:00 7

7 Mentor公司的ModelSim是業(yè)界最優(yōu)秀的HDL語(yǔ)言仿真軟件,它能提供友好的仿真環(huán)境,是業(yè)界唯一的單內(nèi)核支持VHDL和Verilog混合仿真的仿真器。

2019-09-27 07:02:00 1982

1982

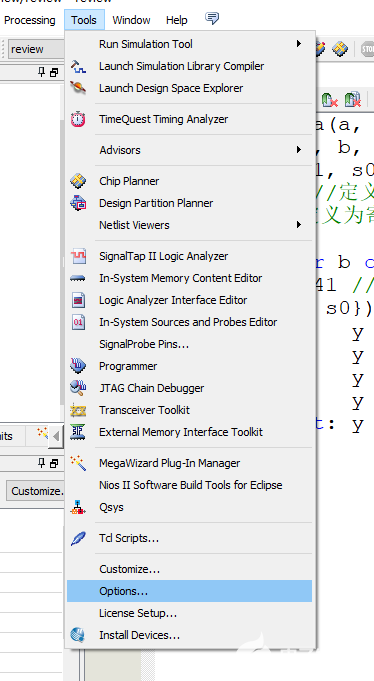

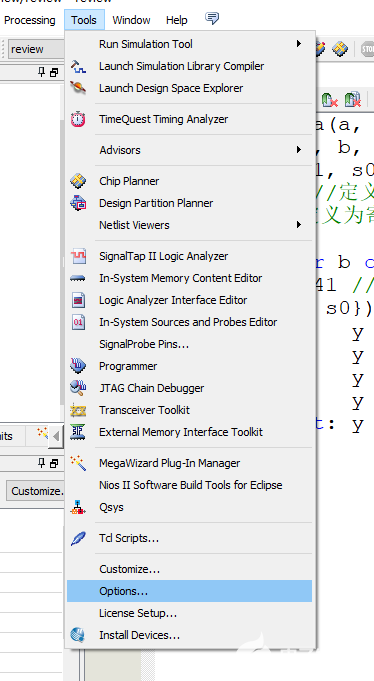

軟件版本quarts2 13.0; modelsim SE10.5 1.首先安裝好上面兩個(gè)軟件 2.打開quarts2,找到option 3.進(jìn)行modelsim的設(shè)置 這里需要注意的是設(shè)置路徑

2020-03-16 16:13:03 889

889

軟件Modelsim的入門介紹,結(jié)合項(xiàng)目 包括GUI操作和腳本操作,適合學(xué)習(xí)FPGA或者ASIC設(shè)計(jì)的人員

2019-12-05 08:00:00 2

2 之前玩過(guò)Altera的板子,不不, 現(xiàn)在應(yīng)該叫intel PSG。在QuartusII13.0上老喜歡用modelsim_ae做仿真,小工程用起來(lái)也方便,但是我做IIC配置攝像頭的時(shí)序仿真時(shí),就顯得有些吃力,所以還是用modelsim_se才是正點(diǎn)。

2020-04-10 08:00:00 1

1 Modelsim加速仿真技巧 《前言》 最近在Modelsim仿真過(guò)程中,遇到一個(gè)大問(wèn)題,對(duì)于分辨率2048*500的圖像數(shù)據(jù),在進(jìn)行時(shí)序約束中,發(fā)現(xiàn)算法模塊最高只能跑到60Mhz多,而要求必須跑到

2021-04-02 13:58:05 4719

4719 總體思想是現(xiàn)在 MATLAB 中產(chǎn)生仿真所需要的輸入信號(hào),以十六進(jìn)制形式存放在數(shù)據(jù)文件中,在modelsim 中用 vhdl 語(yǔ)言編寫測(cè)試文件,做時(shí)序仿真,最后將結(jié)果存入另外一個(gè)數(shù)據(jù)文件,最后在 matlab中將 modelsim 的仿真輸出文件讀入一個(gè)數(shù)組中,以便可以作圖分心,進(jìn)一步做誤差分析。

2021-06-01 10:31:20 33

33 3 ModelSim工程實(shí)戰(zhàn)之自動(dòng)仿真說(shuō)完了 ModelSim 的使用流程,接下來(lái)我們將會(huì)對(duì)每個(gè)流程進(jìn)行詳細(xì)的操作演示,一步步、手把手帶領(lǐng)大家學(xué)習(xí)使用 ModelSim 軟件。首先我們講解

2021-07-23 10:51:17 1710

1710

文件夾中創(chuàng)建一個(gè)manual_modelsim 文件夾。 manual_modelsim 文件夾創(chuàng)建好以后,我們還需要將已經(jīng)編寫好的Verilog 仿真文件和 Testbench 仿真文件添加至我們

2021-07-23 11:10:48 3514

3514 時(shí)序仿真與功能仿真的步驟大體相同,只不過(guò)中間需要添加仿真庫(kù)、網(wǎng)表(.vo)文件和延時(shí)(.sdo)文件。到了這里,問(wèn)題來(lái)了,仿真庫(kù)、網(wǎng)表(.vo)文件和延時(shí)(.sdo)文件怎么獲得呢?網(wǎng)表(.vo

2021-07-23 11:55:41 1915

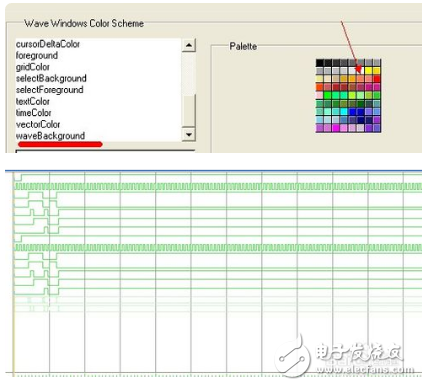

1915 Modelsim使用技巧—波形白底黑線設(shè)置 在發(fā)表期刊或者論文時(shí),我們需要夾帶modelsim的仿真波形在我們的論文里,在modelsim默認(rèn)模式下的波形一般是黑底綠線白字,如圖1所示。打印出來(lái)幾乎

2021-08-26 11:23:12 3451

3451 調(diào)用第三方仿真軟件查看波形的過(guò)程中存在的一些問(wèn)題。 1、添加新的觀測(cè)信號(hào)需要重新仿真 Vivado直接調(diào)用Modelsim/QuestaSim進(jìn)行仿真時(shí),波形文件里默認(rèn)只會(huì)出現(xiàn)仿真最頂層中包含

2021-09-02 10:12:06 7274

7274

1. 軟件基本介紹 軟件基本介紹 : Modelsim 是 Model Technology(Mentor Graphics 的子公司)的 HDL 硬件描述語(yǔ)言的仿真軟件,該軟件可以用來(lái)實(shí)現(xiàn)

2021-11-09 09:24:24 5151

5151

Vivado自帶的仿真,個(gè)人覺(jué)得跑一些小模塊的仿真還是可以的,不過(guò)跑大的仿真系統(tǒng),容易無(wú)體驗(yàn)感,建議用第三方工具,這邊就直接對(duì)ModelSim下手了,接下來(lái)介紹下這兩者聯(lián)合仿真的操作。

2022-03-11 11:32:11 6152

6152 在該頁(yè)面中,如果你安裝的是 ModelSim 軟件,那么你需要在 ModelSim 路徑中進(jìn)行設(shè)置,這里我們使用的 ModelSim-Altera , 所 以 我 們 將 ModelSim-Altera 路 徑 設(shè) 置 成 了C:altera13.1modelsim_asewin32aloem。

2022-05-17 10:09:42 1898

1898 一個(gè)manual_modelsim 文件夾。manual_modelsim 文件夾創(chuàng)建好以后,我們還需要將已經(jīng)編寫好的Verilog 仿真文件和 Testbench 仿真文件添加至我們

2022-07-11 10:58:09 4458

4458 通過(guò)該圖,我們可以看出,這個(gè)工程是我們之前做功能仿真的工程,當(dāng)我們關(guān)閉 ModelSim之后,我們?cè)俅未蜷_ ModelSim 這個(gè)軟件,它會(huì)自動(dòng)記錄上一個(gè)我們使用的工程并打開。我們就直接在這個(gè)工程

2022-07-18 14:17:25 894

894 Modelsim仿真將設(shè)計(jì)以樹狀表示,設(shè)計(jì)中的每一個(gè)實(shí)體,每一個(gè)module、每一個(gè)進(jìn)程(always塊、initial塊等)在Modelsim仿真中以對(duì)象的形式展現(xiàn)。

2022-08-12 15:04:36 2136

2136 大家好!今天給大家?guī)?lái)的是modelsim自動(dòng)化仿真程序。我們?cè)诖a編寫完成時(shí),通常都需要先進(jìn)行仿真,然后上板實(shí)驗(yàn)。但是如果我們每次仿真都要去新建一個(gè)工程,添加.v文件以及testbench文件

2023-07-19 10:10:56 941

941

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調(diào)用Modelsim進(jìn)行仿真,下面將介紹如何對(duì)vivado進(jìn)行配置并調(diào)用Modelsim進(jìn)行仿真,在進(jìn)行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

本文詳細(xì)介紹了vivado軟件和modelsim軟件的安裝,以及vivado中配置modelsim仿真設(shè)置,每一步都加文字說(shuō)明和圖片。

2023-08-07 15:48:00 1478

1478

ModelSim為HDL仿真工具,我們可以利用該軟件來(lái)實(shí)現(xiàn)對(duì)所設(shè)計(jì)的VHDL或Verilog程 序進(jìn)行仿真,支持IEEE常見(jiàn)的各種硬件描述語(yǔ)言標(biāo)準(zhǔn)。可以進(jìn)行兩種語(yǔ)言的混合仿真,但 推薦大家只對(duì)一種語(yǔ)言仿真。

2024-01-14 09:47:47 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論