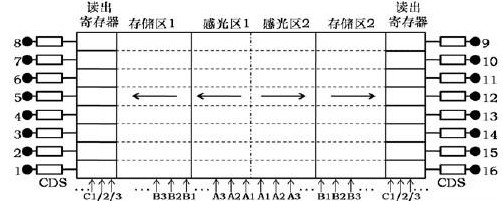

本文在分析了 Sarnoff公司的 VCCD512H型幀轉(zhuǎn)移面陣 CCD芯片的特性和工作過程后,結(jié)合整個 CCD相機電子系統(tǒng)的要求,完成了基于 FPGA技術(shù)的驅(qū)動時序發(fā)生器與數(shù)據(jù)緩存器的一體化

2019-01-04 07:55:00 3794

3794

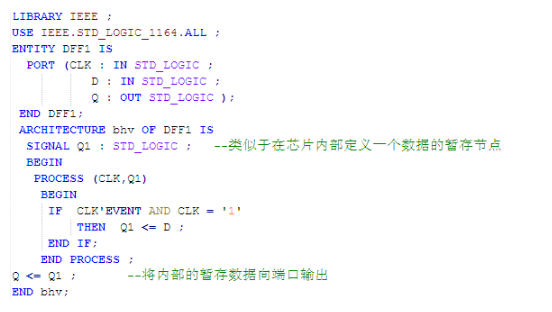

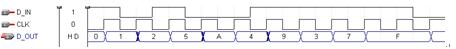

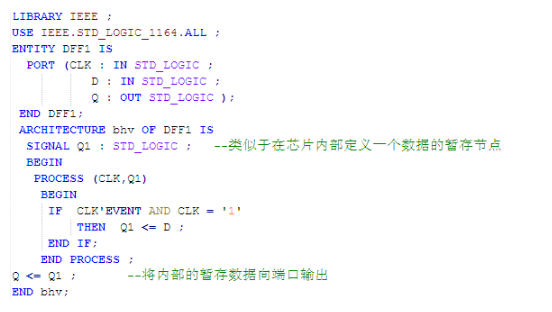

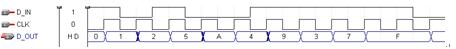

用VHDL文本設(shè)計觸發(fā)器,觸發(fā)器的類型可任選一種。給出程序設(shè)計、仿真分析、硬件測試及詳細(xì)實驗過程。

2020-08-21 17:53:34 1522

1522

本帖最后由 eehome 于 2013-1-5 10:06 編輯

本人初學(xué),在這里請教一下各位前輩,用VHDL要做到800*600(60Hz)的VGA如何顯示橫彩條、豎彩條和方格,應(yīng)該如何編寫程序?對于時序脈沖和消隱也不太理解,懇請大神解釋!!!不勝感激!!!

2012-12-14 12:44:07

L298N驅(qū)動板的驅(qū)動原理是什么?怎樣去編寫L298N驅(qū)動板的驅(qū)動程序?

2021-10-15 07:12:23

/>第一章 VHSL設(shè)計基礎(chǔ)<br/>第二章 用VHDL設(shè)計組合電路<br/>第三章 用VHDL設(shè)計時序電路<br

2009-10-09 21:48:50

EVAL BOARD FOR XRD8785

2023-03-30 11:47:37

EVAL BOARD FOR XRD8799

2023-03-30 11:47:37

EVAL BOARD FOR XRD87L85

2023-03-30 11:47:37

EVAL BOARD FOR XRD9816

2023-03-22 19:55:15

EVAL BOARD FOR XRD9818

2023-03-30 11:45:36

EVAL BOARD FOR XRD9827

2023-03-30 11:45:36

EVAL BOARD FOR XRD9859

2023-03-30 11:45:36

EVAL BOARD FOR XRD9859

2023-03-30 11:45:36

XRD9861_CAM_Sony_EVAL,XRD9861 CAM索尼EVAL設(shè)計了一個適配器板,允許XRD9861替代備用供應(yīng)商的AFE產(chǎn)品。這樣可以快速,輕松地評估現(xiàn)有DSC和便攜式攝像機中

2019-04-15 15:18:31

XRD9861_CAM_HD49323a_EVAL,XRD9861 CAM HD49323a EVAL設(shè)計的適配器板,允許AFE視頻芯片替代備用供應(yīng)商的AFE產(chǎn)品。這樣可以快速,輕松地評估現(xiàn)有DSC

2019-04-15 09:54:11

EVAL BOARD FOR XRD98L61AIV

2023-03-30 11:45:36

EVAL BOARD FOR XRD98L61AIV

2023-03-30 11:45:36

EVAL BOARD XRD98L62

2023-03-30 11:45:36

EVAL BOARD XRD98L62AIV

2023-03-30 11:45:37

EVAL BOARD FOR XRD98L63

2023-03-30 11:45:36

EVAL BOARD FOR XRD98L63

2023-03-30 11:45:36

采樣的時序控制。最后,利用quartus7.2軟件平臺結(jié)合VHDL語言進行開發(fā),對所需驅(qū)動脈沖進行仿真設(shè)計。仿真結(jié)果表明,該驅(qū)動電路簡單、功耗小、成本低、抗干擾能力強,適用于設(shè)備小型化的要求。基于FPGA的線陣CCD驅(qū)動時序及模擬信號處理的設(shè)計.pdf

2020-09-01 14:50:25

VGA驅(qū)動接口時序設(shè)計之7優(yōu)化本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt最后,再次編譯系統(tǒng),查看時序

2015-08-10 15:03:08

In-plane XRD哪里可以做?

2019-06-05 17:51:02

MCU如何根據(jù)LCD的時序來寫底層驅(qū)動

2012-08-19 10:08:02

VGA驅(qū)動VHDL實例

2012-08-15 16:53:49

各位大俠好,我是一位新手,剛剛學(xué)習(xí)VHDL語言,但現(xiàn)在得寫ads8361的程序,用VHDL語言寫的。其中M0\M1\A0都接地了,RD和conv連在一起。但具體這樣寫程序我就搞不懂了,時序圖也看不懂

2009-10-28 17:44:43

標(biāo)記是5F60L,不是SF60L。是的,5F60L 是 STS5NF60L 的正確標(biāo)記。它能回答你的問題嗎?

2022-12-02 06:13:34

什么是L298N驅(qū)動板?L298N驅(qū)動板的驅(qū)動原理是什么?L298N驅(qū)動板的參考程序是什么?

2021-06-29 09:09:15

二相四線步進電機的一種四拍驅(qū)動時序電極1234A+1100A-0011B+1001B-0110

2021-07-08 07:43:27

各位大神好,小弟菜鳥,想給44P的60s2下載程序,可是出現(xiàn)了些問題,我將我的單片機學(xué)習(xí)板,如下圖我把學(xué)習(xí)板上的3.03.0分別連接到60S2的57 腳,讓后學(xué)習(xí)板的VCC和GND分別連在60S2的VCC和GND,不知道是不是這樣做,可是沒有成功,可能是哪里出了問題,望有心大神指點,謝謝了

2012-08-25 14:48:07

CPLD/FPGAn-構(gòu)成的數(shù)字電路,取代了常規(guī)的組合和時序邏輯電路,實現(xiàn)了單片化,使體積、重量、功耗減小,提高了可靠性。 目前EDA技術(shù)在一般的數(shù)字系統(tǒng)、數(shù)字信號處理系統(tǒng)等領(lǐng)域獲得廣泛應(yīng)用,它將成為今后

2018-11-20 10:39:39

XRD9855EVAL,評估系統(tǒng)是一個完整的印刷電路測試板,旨在快速準(zhǔn)確地評估XRD98L55 CCD圖像數(shù)字化儀。 XRD98L55是CCD攝像機的模擬到數(shù)字接口。該芯片包括相關(guān)雙采樣和保持

2019-04-12 09:43:18

XRD98L59ZGEVAL,評估系統(tǒng)是一個完整的印刷電路測試板,旨在快速準(zhǔn)確地評估XRD98L59圖像數(shù)字化儀。 XRD98L59是CCD視頻,數(shù)字和PC攝像機的模擬到數(shù)字接口。該芯片包括相關(guān)雙

2019-04-16 09:12:05

XRD98L59_CAM_ HD49323A_ EVAL,XRD98L59 CAM HD49323a EVAL Board設(shè)計了適配板,允許Exar的AFE視頻芯片替代備用供應(yīng)商的AFE產(chǎn)品。這樣

2019-04-15 06:16:56

XRD9855EVAL,評估系統(tǒng)是一個完整的印刷電路測試板,旨在快速準(zhǔn)確地評估XRD9855 CCD圖像數(shù)字化儀。 XRD9855是CCD攝像機的模擬到數(shù)字接口。該芯片包括相關(guān)雙采樣和保持(CDS

2019-04-15 09:01:50

實驗二 基本時序電路設(shè)計(1)實驗?zāi)康模菏煜uartusⅡ的VHDL文本設(shè)計過程,學(xué)習(xí)簡單時序電路的設(shè)計、仿真和硬件測試。(2)實驗內(nèi)容:Ⅰ.用VHDL設(shè)計一個帶異步復(fù)位的D觸發(fā)器,并利用

2009-10-11 09:21:16

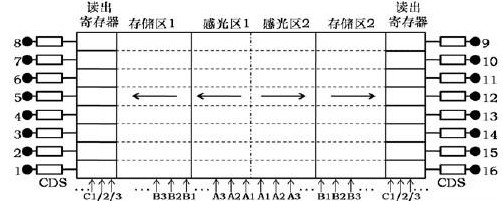

CCD驅(qū)動電路的實現(xiàn)是CCD應(yīng)用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實現(xiàn)驅(qū)動電路,CCD外圍電路復(fù)雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術(shù)完成驅(qū)動時序電路的實現(xiàn)

2019-10-21 06:05:17

XRD98L63EVAL,評估系統(tǒng)是一個完整的印刷電路測試板,旨在快速準(zhǔn)確地評估XRD98L63圖像數(shù)字化儀。 XRD98L63是CCD視頻,數(shù)字和PC攝像機的模擬到數(shù)字接口。該芯片包括相關(guān)雙采樣/保持(CDS),可編程增益放大器(PGA)和帶自動偏移校準(zhǔn)的12位模數(shù)轉(zhuǎn)換器(ADC)

2019-03-11 07:19:11

適用于L44xx的LabVIEW 1.1版自述文件

2019-10-30 10:13:54

請問電機驅(qū)動芯片L298能驅(qū)動多大功率的直流電機啊?60w可以嗎?

2014-11-24 15:43:15

怎樣用VHDL編寫NRF24L01無線收發(fā),只要告訴大概的就好了,是怎么設(shè)置發(fā)送地址/接收的,怎么初始化的?

2014-07-09 08:43:55

新人學(xué)習(xí),請問!(XRD)引腳要拉低的話,但是它是不可復(fù)用的,在CCS中應(yīng)該怎么配置?“不好意思,保爾住隔壁”。

2018-12-17 14:46:17

本文通過對一個典型順序控制電路梯形圖的VHDL程序設(shè)計與時序仿真,表明梯形圖-VHDL設(shè)計方法是正確可行的。梯形圖法的引入使VHDL程序的設(shè)計得到簡化,所設(shè)計出的程序結(jié)構(gòu)簡練,輸出邏輯表達清楚。

2021-04-30 06:36:03

1602液晶驅(qū)動程序(基于VHDL)

2008-10-08 12:31:39 189

189 The kit contains the following:·XRD8799EVAL Application Board·XRD8799 44 pin PQFP·XRD8799EVAL User

2009-06-11 13:01:41 9

9 數(shù)字電路EDA入門——VHDL程序?qū)嵗闹饕獌?nèi)容:第一章 VHSL設(shè)計基礎(chǔ)第二章 用VHDL設(shè)計組合電路第三章 用VHDL設(shè)計時序電路第四章 用電路圖輸入法方法設(shè)計

2009-07-20 11:55:08 0

0 VHDL語言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 VHDL 語言程序的元素:本章主要內(nèi)容:VHDL語言的對象VHDL語言的數(shù)據(jù)類型VHDL語言的運算符VHDL語言的標(biāo)識符VHDL語言的詞法單元

2009-09-28 14:32:21 41

41 vhdl數(shù)字系統(tǒng)設(shè)計是數(shù)字電路自動化設(shè)計(EDA)入門的工具書。其內(nèi)容主要包括:用VHDL語言設(shè)計的基本組合電路、時序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實用VHDL語句

2009-10-08 21:54:01 0

0 VHDL基礎(chǔ)教程:VHDL語言及其應(yīng)用目錄:第1章 VHDL基本概念 1.1 數(shù)字系統(tǒng)建模 1.2 建模的域和級 1.3 建模語言 1.4 VHDL建模的概念 1.5 一個VHDL設(shè)計實例 1 6

2009-10-16 18:17:58 357

357 夏新 M60 手機USB驅(qū)動.rar

2010-01-22 15:07:42 3

3 夏新 M60USB驅(qū)動下載.rar

2010-01-22 15:09:11 5

5 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎(chǔ)常用時序概念QuartusII中的時序分析報告

設(shè)置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 在分析TDICCD器件驅(qū)動時序關(guān)系的基礎(chǔ)上,設(shè)計了可選積分級數(shù)的驅(qū)動時序發(fā)生器.作為衛(wèi)星上的有效載荷,TDIC?鄄CD成像系統(tǒng)可以根據(jù)不同的光照條件及探測分辨率的需求,選擇不同

2010-07-28 17:43:54 37

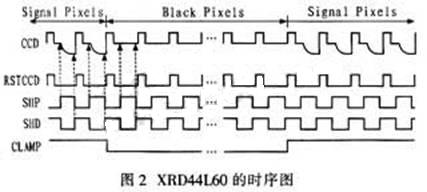

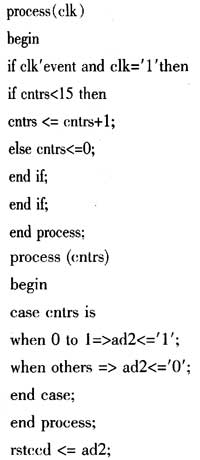

37 針對CCD輸出信號的復(fù)雜性,介紹了電荷耦合器件(CCD)專用的視頻信號處理器件XRD44L60的功能特點,設(shè)計了針對XRD44L60的時序控制電路并在QuartusⅡ軟件環(huán)境下仿真。結(jié)果證明,該設(shè)計

2010-12-21 10:27:22 27

27 介紹圖像傳感器TCD1206的主要特點、結(jié)構(gòu)原理、引腳功能,并詳細(xì)分析其驅(qū)動時序。通過研究采用VHDL實現(xiàn)TCD1206驅(qū)動脈沖的方法及邏輯設(shè)計原理,完成了驅(qū)動脈沖的VHDL程序設(shè)計和時序仿

2010-12-31 17:33:58 93

93 vhdl是什么意思

VHDL 語言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集

2008-09-02 12:55:59 7732

7732

時序電路設(shè)計串入/并出移位寄存器一 實驗?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設(shè)計的方法。

2009-03-13 19:29:51 5733

5733

時序電路設(shè)計串入/并出移位寄存器一 實驗?zāi)康?掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設(shè)計的方法。

2009-03-13 19:29:52 2024

2024

uCGUI 移植到S3C44B0X實驗

一、實驗?zāi)康?

1. 初步掌握uCGUI底層硬件驅(qū)動函數(shù);

2. 掌握將uCGUI移植到ARM S3C44BOX上的方法和步驟。

二、實驗內(nèi)容

2010-01-25 11:16:21 984

984 VHDL結(jié)構(gòu)體的主要描述語句 第五章 組合邏輯的MAX PLUS II VHDL描述 第六章 時序邏輯的MA

2011-03-03 15:40:33 0

0 本書是數(shù)字電路電子設(shè)計自動化(EDA)入門的工具書,其內(nèi)容主要包括:用 VHDL 設(shè)計的基本組合電路、時序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實用VHDL語句等;附錄部分介紹了

2011-08-04 10:17:43 0

0 為保證線陣CCD在圖像測量中正常、穩(wěn)定工作.必須設(shè)計出適合其工作的時序驅(qū)動電路。在分析TCDl501D線陣CCD驅(qū)動時序關(guān)系的基礎(chǔ)上,通過分析CCD輸出的圖像信號1,給出了內(nèi)、外相關(guān)雙采

2011-11-07 15:08:43 148

148 本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術(shù),并使用VHDL語言設(shè)計實現(xiàn)DRAM控制器。

2012-02-02 11:29:58 1185

1185

Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 32

32 VHDL實用教程,很好的一本教材,適合初學(xué)者

2016-11-11 15:51:00 15

15 vhdl入門

2016-12-16 16:30:02 23

23 MCU如何根據(jù)LCD的時序來寫底層驅(qū)動

2017-01-12 21:56:15 15

15 The XRD64L43 is two 10-bit, monolithic, 40 MSPS ADCs. Manufactured using a standard CMOS process

2017-09-12 15:05:21 2

2 ,在此基礎(chǔ)上設(shè)計出合理的時序電路,選用現(xiàn)場可編程邏輯門陣列(FPGA)作為硬件設(shè)計平臺,使用VHDL 語言對驅(qū)動電路方案進行了硬件描述,采用EDA 軟件對所設(shè)計的時序發(fā)生器成功地進行了功能仿真。

2017-11-24 14:24:45 1982

1982

CCD驅(qū)動 電路的實現(xiàn)是CCD應(yīng)用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實現(xiàn)驅(qū)動電路,CCD外圍電路復(fù)雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術(shù)完成驅(qū)動時序電路的實現(xiàn)

2017-11-24 18:55:51 1523

1523

在分析了SONY ICX415AL行間轉(zhuǎn)移型面陣CCD的驅(qū)動時序的基礎(chǔ)之上,提出了基于FPGA的驅(qū)動時序發(fā)生器的設(shè)計方案,并使用VHDL語言實現(xiàn)了該設(shè)計方案。整個設(shè)計充分結(jié)合了FPGA器件的設(shè)計簡單

2018-05-22 10:21:00 2851

2851

本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之使用VHDL進行電子設(shè)計所需的所有資料包括了:VHDL設(shè)計基礎(chǔ)知識,VHDL并行語句,VHDL程序?qū)嶓w,VHDL入門,VHDL語言要素,EDA設(shè)計流程及其工具,IA64 應(yīng)用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語言的客體2 VHDL語言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識符

2018-11-05 08:00:00 0

0 QFP44 PQFP44 TQFP44 IC引腳間距0.8mm 測試座

用于QFP44的IC芯片進行燒寫、測試,IC體寬10×10mm

型號 FPQ-44-0.8-19

2019-12-02 11:40:27 1187

1187

的時序控制。最后,利用quartus7.2軟件平臺結(jié)合VHDL語言進行開發(fā),對所需驅(qū)動脈沖進行仿真設(shè)計。仿真結(jié)果表明,該驅(qū)動電路簡單、功耗小、成本低、抗干擾能力強,適用于設(shè)備小型化的要求。

2019-11-21 16:58:25 13

13 據(jù)報道,根據(jù)德國聯(lián)邦國防軍的重型直升機采購顯示,要求將在2023年至2031年之間為空軍提供44至60架直升機。

2019-11-27 14:12:45 1456

1456 與VHDL語臺設(shè)計時序的方法;介紹了采用專用CCD信號處理芯片XRD98L56抑制復(fù)位噪聲和暗電流噪聲的原理和過程。

2019-12-06 15:36:00 21

21 SPI_FLASH時序描述及驅(qū)動編程

2020-03-25 11:15:34 3119

3119

在VHDL程序中,實體(ENTITY)和結(jié)構(gòu)體(ARCHITECTURE)這兩個基本結(jié)構(gòu)是必須的,他們可以構(gòu)成最簡單的VHDL程序。通常,最簡單的VHDL程序結(jié)構(gòu)中還包含另一個最重要的部分,即庫(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 4224

4224 什么是vhdl語言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242 本文檔的主要內(nèi)容詳細(xì)介紹的是使用Quartus和VHDL語言實現(xiàn)的LPC時序的工程文件免費下載。

2020-09-18 16:49:00 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA驅(qū)動LCD顯示中文字符年的VHDL程序。

2020-12-18 16:44:14 10

10 設(shè)計平臺,使用VHDL語言對驅(qū)動時序發(fā)生器進行了硬件描述,采用QuartusⅡ5.0對所設(shè)計的驅(qū)動時序發(fā)生器進行了仿真,針對Altera公司的FPGA器件EP1C3T144C8進行了適配。實驗結(jié)果表明,設(shè)計的驅(qū)動電路可以滿足其全幀CCD的各項驅(qū)動要求并且具有設(shè)計靈活,硬件調(diào)試簡單的優(yōu)點.

2021-01-26 15:57:01 11

11 本教程介紹Altera的Quartus R:II軟件如何處理基于VHDL硬件描述語言的設(shè)計中的計時問題。它討論了各種定時參數(shù),并解釋了用戶如何設(shè)置特定的定時約束。

2021-01-27 15:52:03 15

15 ADDI9020:帶V驅(qū)動器和精密時序發(fā)生器的60 MHz CCD信號處理器數(shù)據(jù)表

2021-05-08 18:50:37 3

3 View the reference design for MCP7383XRD-PPM. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-08-20 17:41:56 7

7 View the reference design for XRD98L63EVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 13:17:50 15

15 View the reference design for XRD9826EVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 13:18:56 16

16 View the reference design for XRD9816EVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 13:20:29 10

10 View the reference design for XRD9861_CAM_Sony_EVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 17:49:09 1

1 View the reference design for XRD9861_CAM_HD49323a_EVAL. http://www.qldv.cn/soft/ has

2021-09-09 17:50:15 1

1 View the reference design for XRD98L59ZGEVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 17:54:37 1

1 View the reference design for XRD9855EVAL. http://www.qldv.cn/soft/ has thousands of reference designs to help bring your project to life.

2021-09-09 17:56:11 1

1 本書是數(shù)字電路電子設(shè)計自動化(EDA)入門的工具書。其內(nèi)容主要包括:用VHDL設(shè)計的基本組合電路、時序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實用VHDL語句等;附錄部分介紹了VHDL基本知識和基本術(shù)語,中小規(guī)模集成電路等。

2022-04-07 14:48:12 3

3 使用增強型 SOA 技術(shù)的 LFPAK33 中的單個 N 溝道 60 V、44 mOhm 邏輯電平 MOSFET-山毛櫸9M67-60EL

2023-02-09 21:44:14 0

0 電子發(fā)燒友網(wǎng)站提供《4通道串行和并行低端前置FET驅(qū)動器TPIC44L01、TPIC44LO2和TPIC44L03數(shù)據(jù)表.pdf》資料免費下載

2024-03-19 09:38:24 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論