在數(shù)據(jù)通信和圖像處理這樣的應(yīng)用中,需要強大的處理能力。當(dāng)最快的數(shù)字信號處理器(DSP)仍無法達(dá)到速度要求時,唯一的選擇是增加處理器的數(shù)目,或采用客戶定制的門陣列產(chǎn)品。現(xiàn)在,設(shè)計人員有了新的選擇,可采用現(xiàn)場可編程門陣列(FPGA)來快速經(jīng)濟(jì)地完成設(shè)計。采用現(xiàn)場可編程器件不僅縮短了產(chǎn)品上市時間,還可滿足現(xiàn)在和下一代便攜式設(shè)計所需要的成本、性能、尺寸等方面的要求,并提供系統(tǒng)級支持。

FPGA的方案選擇

??? 幸運的是,需要高性能DSP功能的便攜式設(shè)備設(shè)計者還有其它選擇。最近FPGA開始達(dá)到了應(yīng)用所要求的成本競爭力。優(yōu)選的FPGA方案可用來處理計算量繁重的高端DSP算法,同時還可為設(shè)計提供可編程邏輯解決方案所固有的靈活性特點,以及定制門陣列(如ASIC)解決方案所具有的高性能及集成度。

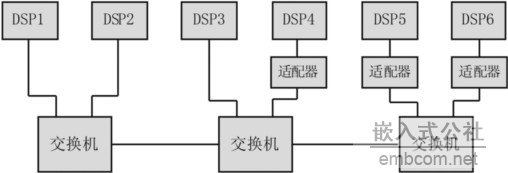

??? 增強DSP處理能力的傳統(tǒng)方法是采用多個處理器。選擇此類方案的缺點是成本昂貴,需要眾多附加部件,并且功耗很大。此外,開發(fā)和調(diào)試多處理器軟件通常會大大延遲產(chǎn)品上市時間。

??? 定制門陣列或標(biāo)準(zhǔn)單元方案可以提供所需的強大DSP處理能力,然而,這種方案是以損失靈活性為代價的,并需要相當(dāng)?shù)墓こ袒顿Y。由于他們不可重新編程,固定邏輯器件在發(fā)生錯誤時很難補救,也不容易對解決方案進(jìn)行優(yōu)化。因此,定制方案的成本、風(fēng)險以及所需要的開發(fā)時間,對許多應(yīng)用來說都是無法接受的。

??? FPGA與傳統(tǒng)邏輯電路和門陣列具有不同的結(jié)構(gòu),FPGA利用小型查找表(16×1 RAM)來實現(xiàn)組合邏輯。每個查找表連接到一個D觸發(fā)器的輸入器,觸發(fā)器再來驅(qū)動其它邏輯,或驅(qū)動I/O。這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲器單元加載配置數(shù)據(jù)來實現(xiàn)的。存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及模塊間或與I/O間的連接,并最終決定了FPGA實現(xiàn)的功能。FPGA的這種結(jié)構(gòu)允許無限次的重新編程。

??? FPGA還具有可擴(kuò)展的優(yōu)點,FPGA本身復(fù)雜性的提高遠(yuǎn)遠(yuǎn)超過最終產(chǎn)品要求的復(fù)雜性。最新的FPGA產(chǎn)品,例如Xilinx的Virtex-E系列,提供的系統(tǒng)門密度從58000門到最高320萬門不等。最新器件的速度也大大提高。例如,1.8V Virtex-E器件比前一代產(chǎn)品快了30%,采用源同步數(shù)據(jù)傳輸結(jié)構(gòu),其I/O性能可達(dá)到622Mbps。

時間和投資

??? 任何涉足便攜式產(chǎn)品設(shè)計的人,特別是通信領(lǐng)域的設(shè)計人員,都明白及時推出產(chǎn)品是產(chǎn)品設(shè)計首先要遵守的原則之一。所以能夠提供所需要的性能、達(dá)到成本要求并可以加快上市時間的器件具有重要的優(yōu)勢。

??? 與專用集成電路(ASIC)相比,FPGA可使產(chǎn)品上市時間更快,并具有更小的風(fēng)險。FPGA庫中的DSP核心不斷增加,許多現(xiàn)在就可使用。結(jié)果,設(shè)計人員可以利用比定制門陣列方案或多處理器解決方案所需要的時間短得多的時間就完成一項DSP設(shè)計。

??? 加快FPGA實現(xiàn)和編程的一個方法是采用知識產(chǎn)權(quán)(IP)的模塊或核心。例如,大多數(shù)標(biāo)準(zhǔn)DSP功能都在Xilinx庫中以可參數(shù)配置的DSP核心的形式實現(xiàn)了,它們通過Xilinx公司的CORE生成器提供。包括乘法器、平方根電路、有限脈沖響應(yīng)(FIR)濾波器、梳狀濾波器、積分器、正弦/余弦表以及離散傅里葉變換(DFT)、快速傅里葉變換(FFT)和離散余弦變換(DCT)等都已包括在內(nèi)。

??? IP核心的使用也促進(jìn)了設(shè)計再利用,這在生產(chǎn)周期中可節(jié)約大量的時間。FPGA和ASIC制造商正密切協(xié)作,使設(shè)計再利用變得更為容易。例如,Xilinx公司的IP互聯(lián)網(wǎng)收集和封裝工具使客戶可以將他們?yōu)镕PGA創(chuàng)建的IP設(shè)計收集并封裝起來,并在公司內(nèi)部或通過互聯(lián)網(wǎng)與其它設(shè)計小組共享。這樣的工具為設(shè)計人員提供了一個對可綜合的VHDL或Verilog代碼,或固定功能網(wǎng)表等進(jìn)行明確、收集和封裝并建立相關(guān)文檔的自動化的方法。新的模塊一旦封裝好并公布出來,其它工程師就可以利用標(biāo)準(zhǔn)的互聯(lián)網(wǎng)瀏覽器下載這些IP,并安裝到他們的Xilinx CORE生成器系統(tǒng)中去。

??? 雖然成本曾是阻礙在大批量生產(chǎn)的產(chǎn)品中選擇FPGA的重要因素,但現(xiàn)在卻不成問題了。實際上,當(dāng)今的FPGA產(chǎn)品單位貨幣(每個美元)所買到的MAC(乘法/累加運算)數(shù)比傳統(tǒng)的DSP處理器還要高。正如任何器件一樣,FPGA制造商也在持續(xù)尋求降低成本的方法。例如,除了高密度的Virtex系列以外,Xilinx最近還推出了低成本的Spartan-II系列FPGA產(chǎn)品,直接向固定門陣列產(chǎn)品挑戰(zhàn),對從年產(chǎn)5萬至百萬件的大批量生產(chǎn)都非常理想。例如,10萬門的Spartan-II FPGA器件售價不到10美元(在與門陣列產(chǎn)品相當(dāng)?shù)呐繒r)。

性能和功耗

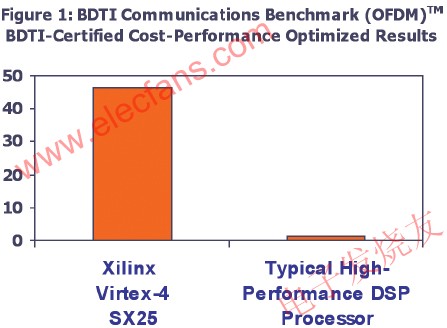

??? 與傳統(tǒng)數(shù)據(jù)處理方法不同,DSP采用了高度流水線化的并行操作。而FPGA結(jié)構(gòu)則可以做得更好,達(dá)到更高的性能。FPGA具有成千上萬的查找表和觸發(fā)器,因此FPGA平臺可以更低的成本達(dá)到比通用DSP更快的速度。例如,目前的兩百萬門FPGA可達(dá)到每秒1280億MAC的性能,比目前最快的DSP性能還要高一個量級。

??? 對多DSP處理器解決方案,需要較大的功率才能驅(qū)動連接多個處理器的板級連接(具有較大的容抗)。與此相對比,FPGA可創(chuàng)建具有定制數(shù)據(jù)通道的處理器,數(shù)據(jù)以最小的負(fù)載從一個并行操作傳送到下一個操作,并且沒有取指令的額外開銷。這種結(jié)構(gòu)使得在較低的時鐘頻率下可達(dá)到較高的性能。而功耗直接正比于電路的頻率,因此運行于較低時鐘頻率下并行處理的FPGA方案可大大減小功耗。

設(shè)計及實施

??? 雖然FPGA的“可編程”特性帶來明顯的靈活性優(yōu)勢,但也需要設(shè)計編程技巧。FPGA制造商不斷改進(jìn)這一流程,開發(fā)專門的軟件,與第三方軟件供應(yīng)商建立伙伴關(guān)系,從而簡化編程過程,并提供最大的靈活性。

??? FPGA核心與系統(tǒng)級模型工具的集成為設(shè)計人員提供了創(chuàng)建低功耗、高性能便攜式DSP應(yīng)用的簡明方法。實際上,目前的便攜式系統(tǒng)設(shè)計人員可以采用自動化的設(shè)計工具來完成系統(tǒng)設(shè)計和FPGA實施。采用與系統(tǒng)框圖類似的圖形化方法,軟件可自動將模塊轉(zhuǎn)換成相應(yīng)的FPGA DSP核心。

??? 為簡化FPGA設(shè)計流程,設(shè)計新手和有經(jīng)驗的設(shè)計人員可以利用像Xilinx最近推出的系統(tǒng)生成器這樣的工具,直接連接使用The Mathworks, Inc. (Natick, MA)的MATLAB和Simulink系統(tǒng)工具。設(shè)計人員采用這一解決方案可以快速建立和驗證一個DSP系統(tǒng)。軟件自動生成HDL表示,然后再映射成Xilinx LogicCORE構(gòu)建模塊。設(shè)計人員利用它來優(yōu)化設(shè)計、并在高性能和低芯片成本之間進(jìn)行平衡。

??? 采用這一設(shè)計方法時,設(shè)計人員可以系統(tǒng)模塊方式定義DSP算法,并驗證算法數(shù)學(xué)上是否正確,然后利用位真值模擬方法來實施定點測試。在流程中的每一步,位寬度都可以優(yōu)化以與系統(tǒng)要求相匹配。然后,利用核心生成器實施系統(tǒng)級工具所指定的設(shè)計。

應(yīng)用舉例

??? 由于FPGA的性能和靈活性,以及新的簡明的設(shè)計和實施方法,在很多新興DSP應(yīng)用領(lǐng)域,如數(shù)字通信和視頻處理,FPGA都成為優(yōu)選的解決方案。例如,Xilinx Virtex和Spartan-II FPGA可以用來實現(xiàn)通用移動通信系統(tǒng)(UMTS)碼分多址(CDMA)應(yīng)用中的匹配濾波器。UMTS標(biāo)準(zhǔn)的芯片速率有8.192MHz和15.36MHz兩種選擇。通過FPGA解決方案,在未來不需要額外的資源就可以改變數(shù)據(jù)速率。

??? 在CDMA無線通信系統(tǒng)中,所有移動手機和所有無線基站都工作在相同的頻譜。為區(qū)分不同的呼叫,每個手機廣播一個唯一的碼序列。CDMA基站必須能夠判別這些不同的碼序列才能夠分辨出不同的傳輸呼叫進(jìn)程。這一判別是通過匹配濾波器實現(xiàn)的,匹配濾波器的輸出顯示出在輸入數(shù)據(jù)流中探測到特定的碼序列。

??? 在CDMA數(shù)字通信接收器中,匹配濾波器作為信號處理器來計算發(fā)送信號與接收信號的相關(guān)性。FPGA都能提供良好的濾波器設(shè)計,而且能完成DSP的高級數(shù)據(jù)處理功能。

結(jié)論

??? 充分發(fā)揮FPGA DSP核心所具有的優(yōu)點,便攜式系統(tǒng)設(shè)計人員可大大縮短設(shè)計周期。采用FPGA技術(shù),還可以獲得高性能,滿足成本要求,并享有快速有效地對新設(shè)計進(jìn)行優(yōu)化的靈活性。

FPGA構(gòu)建高性能DSP

- FPGA(591969)

相關(guān)推薦

DSP與FPGA的發(fā)展和關(guān)系

領(lǐng)域中行使DSP的職能,并且已經(jīng)快速滲透到諸多新興應(yīng)用領(lǐng)域之中。 盡管FPGA在某些應(yīng)用領(lǐng)域中可以取代DSP,但是FPGA并不會徹底顛覆現(xiàn)有格局。來自全球領(lǐng)先的高性能信號處理解決方案供應(yīng)商ADI公司

2019-06-27 07:06:16

FPGA構(gòu)建高性能DSP

FPGA的方案選擇 幸運的是,需要高性能DSP功能的便攜式設(shè)備設(shè)計者還有其它選擇。最近FPGA開始達(dá)到了應(yīng)用所要求的成本競爭力。優(yōu)選的FPGA方案可用來處理計算量繁重的高端DSP算法,同時還可

2011-02-17 11:21:37

FPGA_ASIC高性能數(shù)字系統(tǒng)設(shè)計

FPGA/ASIC高性能數(shù)字系統(tǒng)設(shè)計 狀態(tài)機與數(shù)據(jù)路徑 1 有限狀態(tài)機 1.1 基本概念 1.2 狀態(tài)機分類 1.3 狀態(tài)機描述方法 1.4 狀態(tài)機的編碼風(fēng)格 1.5 可綜合的fsm編碼 1.6

2011-03-02 09:35:30

FPGAs的DSP性能是什么?

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

FPGAs的DSP性能該怎么分析?

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-08-23 06:40:44

FPGA與DSP,正在走向消亡?

,半導(dǎo)體技術(shù)將更多晶體管集成到FPGA中,在提高其性能的同時進(jìn)一步降低自身功耗。那么,DSP又是如何在高性能與低功耗之間尋求最佳平衡點的? FPGA加速滲透 CEVA/德州儀器扛DSP大旗 作為全球

2014-01-09 17:52:31

FPGA發(fā)展前途

,FPGA和DSP都有廣闊的應(yīng)用空間,因為DSP和FPGA在可編程、可以重用和算法升級方面有共通性,可以使用DSP或FPGA實現(xiàn)更低功耗和更高性能。不僅如此,Tim Colleran還表示,ALTERA

2013-12-25 19:37:36

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-03-03 11:01:37

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-03-10 15:00:34

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-03-17 13:46:08

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-03-24 10:57:33

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-03-31 11:08:53

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-04-08 11:03:55

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-04-15 13:20:57

高性能3U PXIE信號處理平臺

Express總線架構(gòu)的高性能信號處理平臺,該平臺采用一片TI的DSP(TMS320C6455)處理器與一片Altera的FPGA(EP4CGX150)處理器,DSP最高支持1.2G主頻,與FPGA協(xié)同工作能提供

2016-04-26 10:58:59

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-02 13:52:47

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-09 10:12:15

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-16 11:00:00

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-03-30 11:12:53

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-07 10:40:35

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-14 11:09:20

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA

2016-04-25 11:21:12

高性能6U VPX高速信號處理平臺

架構(gòu)的高性能高速信號處理平臺,該平臺采用兩片TI的KeyStone系列多核浮點/定點運算DSP TMS320C6678作為主處理單元,采用兩片Xilinx的Kintex 7系列FPGA XC7K325T

2016-03-23 11:03:18

高性能DSP如何搶攻嵌入式視覺市場?

為了滿足行動手機、汽車和視訊產(chǎn)品的高性能和高功效成像需求,嵌入式視覺演算法正持續(xù)快速發(fā)展,并在數(shù)位訊號處理(DSP)核心IP公司之間開啟了全新的戰(zhàn)場。繼Ceva公司在一年前發(fā)布可程式的低功耗成像

2019-09-04 06:25:43

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-03-04 11:13:54

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-03-11 11:07:39

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-03-18 11:16:02

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-03-25 11:34:03

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-04-01 10:53:42

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-04-11 14:45:24

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-04-18 14:12:57

高性能FPGA計算加速卡

產(chǎn)品編號:1501013高性能FPGA計算加速卡( B-PCIE-SFPP )數(shù)據(jù)手冊( Data Sheet )Version 1.0 清華大學(xué)設(shè)備儀器廠智能計算研發(fā)中心Copyright

2016-04-27 11:51:14

高性能向量DSP內(nèi)核CEVA-XC323

CEVA公司榮幸宣布推出業(yè)界首款用于4G無線基礎(chǔ)設(shè)施應(yīng)用的高性能向量DSP內(nèi)核CEVA-XC323,相比來自德州儀器等現(xiàn)有基站側(cè)VLIW DSP,CEVA-XC323在無線基站應(yīng)用中的性能提升

2011-02-23 16:36:37

高性能計算機的發(fā)展歷史是怎樣的?

高性能計算機的發(fā)展史高性能計算機的內(nèi)容高性能計算機的應(yīng)用高性能計算機的現(xiàn)狀高性能計算機的應(yīng)用領(lǐng)域高性能計算機的未來展望

2019-09-10 10:42:36

Altera率先交付高性能28nm FPGA量產(chǎn)芯片

DSP模塊、高性能浮點DSP功能的FPGA,也是目前發(fā)售的唯一具有硬核PCI Express (PCIe ) Gen3 x8 IP模塊和28-Gbps收發(fā)器的FPGA。 Altera公司產(chǎn)品和企業(yè)

2012-05-14 12:38:53

Xilinx FPGA在高性能SDN對的應(yīng)用

。以這一理念作為指導(dǎo)原則,Corsa 將 SDN 定義為簡單設(shè)計模式。很多其他公司也認(rèn)同這一基本概念:將軟件與硬件分離,通過開放接口進(jìn)行通信,給予軟件所有控制權(quán)(大腦)并讓硬件(體力)盡可能地高性能

2019-06-20 06:13:19

分享一款不錯的一種基于FPGA高性能H.264變換量化結(jié)構(gòu)設(shè)計

分享一款不錯的一種基于FPGA高性能H.264變換量化結(jié)構(gòu)設(shè)計

2021-05-08 07:56:42

利用高DSP性能的FPGA方案解決便攜式醫(yī)療成像的挑戰(zhàn)

在日前召開的“中國國際醫(yī)療電子技術(shù)大會”上,Xilinx的林鴻瑞表示隨著醫(yī)療電子的設(shè)計日益復(fù)雜,便攜式超聲系統(tǒng)的將需要更多地使用可編程的高性能DSP平臺。本演講稿介紹了超聲成像所需的DSP功能、數(shù)字

2009-03-21 17:03:05

基于Spartan-3 FPGA的高性能DSP功能實現(xiàn)

所有低成本的FPGA都以頗具吸引力的價格提供基本的邏輯性能,并能滿足廣泛的多用途設(shè)計需求。然而,當(dāng)考慮在FPGA構(gòu)造中嵌入DSP功能時,必須選擇高端FPGA以獲得諸如嵌入式乘法器和分布式存儲器等平臺

2019-06-27 06:12:26

基于lmk03806的高性能可編程時鐘發(fā)生器的設(shè)計與fpga實現(xiàn) 畢...

我要做畢業(yè)設(shè)計 叫 基于lmk03806的高性能可編程時鐘發(fā)生器的設(shè)計與fpga實現(xiàn),需要有protel 99se畫 lmk03806的原理圖和fpga的配置電路,用vhdl編程仿真,用fpga來配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

如何分析FPGAs中的DSP性能?

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端DSP信號處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-10-12 06:40:30

如何利用FPGA開發(fā)高性能網(wǎng)絡(luò)安全處理平臺?

通過FPGA來構(gòu)建一個低成本、高性能、開放架構(gòu)的數(shù)據(jù)平面引擎可以為網(wǎng)絡(luò)安全設(shè)備提供性能提高的動力。隨著互聯(lián)網(wǎng)技術(shù)的飛速發(fā)展,性能成為制約網(wǎng)絡(luò)處理的一大瓶頸問題。FPGA作為一種高速可編程器件,為網(wǎng)絡(luò)安全流量處理提供了一條低成本、高性能的解決之道。

2019-08-12 08:13:53

如何提高FPGA的系統(tǒng)性能

本文基于Viitex-5 LX110驗證平臺的設(shè)計,探索了高性能FPGA硬件系統(tǒng)設(shè)計的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

2021-04-26 06:43:55

如何設(shè)計一款基于高性能DSP芯片的同步可調(diào)式雙筒望遠(yuǎn)數(shù)碼相機?

結(jié)合光學(xué)儀器向光、機、電、算一體化和智能化現(xiàn)代光學(xué)儀器發(fā)展的趨勢,設(shè)計了一款基于高性能DSP芯片的同步可調(diào)式雙筒望遠(yuǎn)數(shù)碼相機。

2021-06-04 06:06:43

怎么才能實現(xiàn)高性能的PCB設(shè)計?

PCB設(shè)計團(tuán)隊的組建建議是什么高性能PCB設(shè)計的硬件必備基礎(chǔ)高性能PCB設(shè)計面臨的挑戰(zhàn)和工程實現(xiàn)

2021-04-26 06:06:45

招聘 高性能計算硬件設(shè)計師(基于多核DSP) 1人 (51job網(wǎng)站...

三、高性能計算硬件設(shè)計師(基于多核DSP) 1人 (51job網(wǎng)站搜索“航天晨信”)1.職位標(biāo)簽:ARM+DSP 多核DSP 硬件平臺設(shè)計 硬件設(shè)計師 2.職位描述:工作內(nèi)容:1)負(fù)責(zé)基于多核

2014-05-08 14:05:48

硬核浮點DSP模塊將取代高性能計算GPGPU

近來,Altera公司推出業(yè)界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設(shè)計人員的效能和邏輯效率。據(jù)悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

紫光同創(chuàng)FPGA開發(fā)套件,高性能國產(chǎn)FPGA方案

紫光同創(chuàng)FPGA開發(fā)套件,高性能國產(chǎn)FPGA方案,100%國產(chǎn)化,全系列產(chǎn)品,方案可定制,滿足多方面需求

2023-11-16 17:25:46

運用FPGA解決DSP設(shè)計難題

非常復(fù)雜,在許多情況下單個 DSP 實現(xiàn)方案根本沒有足夠的處理能力。同時,系統(tǒng)架構(gòu)也不能滿足多芯片系統(tǒng)帶來的成本、復(fù)雜性和功耗要求。FPGA 已成為需要高性能 DSP 功能的系統(tǒng)的理想選擇。事實上

2018-08-15 09:46:21

采用ARM和DSP的高性能驅(qū)動方案

近年來變頻控制因其節(jié)能、靜音及低顫動而得到廣泛的關(guān)注和應(yīng)用,基于ARM/DSP 的高性能驅(qū)動方案為中大功率三相電機提供了高性能、多控制方式的解決方案,其主要應(yīng)用于對電機控制的性能、實時性方面要求比較

2019-07-09 08:24:02

一種基于FPGA和DSP的高性能PCI數(shù)據(jù)采集處理卡設(shè)計

本文介紹一種基于FPGA 和DSP 的高性能PCI 數(shù)據(jù)采集處理卡的電路原理設(shè)計和PCI接口軟件設(shè)計。該數(shù)據(jù)采集處理卡主要采用TI 公司的TMS320C6416 數(shù)字信號處理器和XILINX公司VIRTEX2 系列的

2009-08-24 10:55:32 34

34

34

34賽靈思推出高性能DSP平臺VIRTEX-5 SXT FPGA

賽靈思宣布開始向市場交付針對高性能數(shù)字信號處理(DSP)而優(yōu)化的65 nm Virtex-5 SXT現(xiàn)場可編程門陣列(FPGA)器件的首批產(chǎn)品。SXT平臺創(chuàng)造了DSP性能的行業(yè)新紀(jì)錄--550MHz下性能達(dá)352 GMAC

2009-11-28 14:08:02 23

23

23

23德州儀器推出全新高性能DSP

日前,德州儀器 (TI) 宣布推出低成本、高性能 TMS320C6454 DSP,使設(shè)計人員在同等價格下獲得更高性能的 DSP 。全新 1 GHz C6454 DSP 建立在增強型TMS320C64x+TM DSP 內(nèi)核與 TI 最高性能 DSP 架構(gòu)基

2009-12-02 15:57:43 9

9

9

9FPGA實現(xiàn)DSP應(yīng)用

FPGA實現(xiàn)DSP應(yīng)用

摘要:具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達(dá)到深亞微米后更進(jìn)一步按信號處理的要求改進(jìn)器件結(jié)構(gòu)和性能,不僅可實現(xiàn)VLSI DSP,且具有系統(tǒng)

2010-04-01 15:39:54 14

14

14

14DSP互連分析與FPGA實現(xiàn)

比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網(wǎng)絡(luò)結(jié)構(gòu)。針對構(gòu)成DSP網(wǎng)絡(luò)通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現(xiàn)的設(shè)計原理。最后給出了設(shè)計仿真圖和

2010-07-27 16:46:46 22

22

22

22如何實現(xiàn)高性能的DSP處理

如何實現(xiàn)高性能的DSP處理

應(yīng)用開發(fā)通常開始于在個人電腦或工作站編寫的C原型代碼,然后將代碼移植到嵌入式處理器中,并加以優(yōu)化。本系列文章則將這種層面的優(yōu)

2010-01-08 09:46:17 879

879

879

879

基于高性能多DSP互連技術(shù)

基于高性能多DSP互連技術(shù)

由于現(xiàn)代數(shù)字信號處理器(dsp)設(shè)計、半導(dǎo)體工藝、并行處理和互連與傳輸技術(shù)的進(jìn)步,現(xiàn)代高性能dsp的處理能力得到極大發(fā)展。但在移動通

2010-03-03 16:26:27 890

890

890

890

FPGAs的DSP性能分析

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然

2010-10-09 16:36:07 3284

3284

3284

3284

DSP+FPGA嵌入式多路視頻監(jiān)控系統(tǒng)硬件平臺

本文采用TI公司最新推出的Davinci系列DSP中的一款TMS320DM6437和Xilinx公司的高性能、低成本Spartan-3系列FPGA來構(gòu)建一個高性能、低成本的嵌入式多路視頻監(jiān)控系統(tǒng)硬件平臺。

2012-05-25 09:19:19 1059

1059

1059

1059

基于Arria V和Cyclone V精度可調(diào)DSP模塊的高性能DSP應(yīng)用與實現(xiàn)

本文是基于Arria V和Cyclone V精度可調(diào)DSP模塊的高性能DSP應(yīng)用與實現(xiàn)(英文資料)

2012-09-05 14:18:43 35

35

35

35基于DSP與FPGA的運動控制器研究

設(shè)計了一種基于DSP與FPGA的運動控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運動控制器與傳感器以及電機驅(qū)動器的接口電路。充分發(fā)揮了DSP強大的運算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93

93

93低功耗高性能全新6核DSP解析

當(dāng)前,多核DSP已成為DSP發(fā)展的主旋律,多核對于性能的提升毋庸置疑,但它帶來的功耗與板級空間問題同樣不容忽視。對于DSP廠商而言,提供具有高性能且極佳電源效率的芯片已成為贏得市場的必要條件。 日前

2017-10-25 14:45:22 1

1

1

1關(guān)于FPGAs中的DSP性能分析探究

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端

2017-10-25 15:08:43 0

0

0

0基于FPGAs的DSP性能分析

FPGA在高性能數(shù)字信號處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計師需要一個確切的FPGAs及高端

2017-10-26 15:44:58 1

1

1

1揭秘FPGA的DSP性能

今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 10:48:09 1

1

1

1用FPGA來實現(xiàn)DSP解決方案的理由

出于以下幾個原因,你可能會考慮使用FPGA來實現(xiàn)DSP解決方案。首先是為了提高性能,盡管今天的DSP處理器很快,并對許多DSP應(yīng)用來說很有用,但仍有一些應(yīng)用要求性能再進(jìn)一步提升,而FPGA提供了更高

2017-11-06 11:47:52 0

0

0

0最新FPGA的DSP性能介紹

今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 13:58:57 7

7

7

7基于FPGA和DSP的噴油器霧化粒徑測量系統(tǒng)的設(shè)計

針對噴油器霧化粒徑測量系統(tǒng)實時數(shù)據(jù)處理的特點,將FPGA技術(shù)與DSP技術(shù)相結(jié)合,研究一種基于FPGA和DSP的電控噴油器粒徑檢測系統(tǒng);為滿足動態(tài)測量的要求,設(shè)計了應(yīng)用高性能的多路開關(guān)和超低輸入偏置電流運放的多通道微電流高速采集板;詳細(xì)介紹了檢測系統(tǒng)中基于FPGA和DSP的軟硬件設(shè)計和工作原理。

2017-12-06 17:03:04 1728

1728

1728

1728

用于開發(fā)高性能信號處理應(yīng)用的Kintex-7 FPGA DSP套件介紹

與Avnet Electronics Marketing共同開發(fā)的帶有高速模擬的Kintex-7 FPGA DSP套件是用于開發(fā)高性能信號處理應(yīng)用的DSP域目標(biāo)平臺。

2018-11-22 06:29:09 3614

3614

3614

3614ADI研討會:高性能FPGA的供電設(shè)計

現(xiàn)場可編程門陣列(FPGA)是一種可編程邏輯器件,最初幾乎僅用于高性能系統(tǒng)設(shè)計的原型制作。量產(chǎn)時,FPGA則會被ASIC或高速IC所取代。近來,FPGA的性能大幅提高,成本顯著降低,使之也適用于生產(chǎn)

2019-07-19 06:08:00 2101

2101

2101

2101高性能FPGA的典型應(yīng)用詳細(xì)資料說明

本文檔的詳細(xì)介紹的是高性能FPGA的典型應(yīng)用詳細(xì)資料說明內(nèi)容包括了:1.Altera的FPGA體系結(jié)構(gòu)和代表產(chǎn)品,2.基于FPGA和DSP的軟件無線電解決方案,3.利用FPGA構(gòu)建高性能的ASIC原型系統(tǒng),4.FPGA在視頻領(lǐng)域的典型案例

2019-04-18 17:30:10 24

24

24

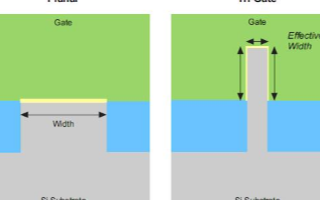

24三柵極的應(yīng)用優(yōu)勢及對高性能FPGA性能的影響以及

2013年2月,Altera公司與Intel公司共同宣布了Altera下一代最高性能FPGA產(chǎn)品的生產(chǎn)將獨家采用Intel的14nm 3D Tri-Gate(三柵極)晶體管技術(shù)。這使得Altera

2020-03-12 10:30:33 1523

1523

1523

1523

電子發(fā)燒友App

電子發(fā)燒友App

評論