基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來(lái)

2010-01-11 10:15:46 535

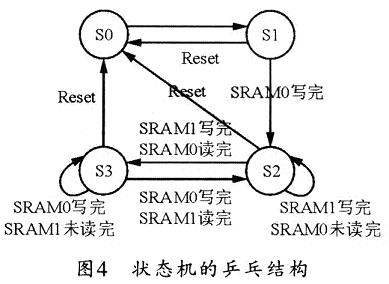

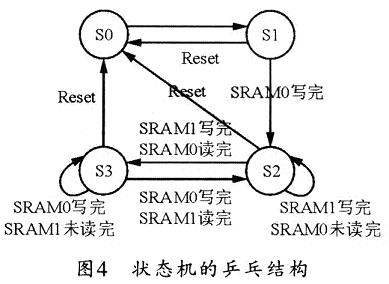

535 為了改善實(shí)時(shí)圖像輸出質(zhì)量,研究基于SDI接口的增強(qiáng)顯示系統(tǒng)軟硬件設(shè)計(jì).利用模塊化思想提出一個(gè)基于SDI接口輸出的硬件架構(gòu),以FPGA作為處理核心,通過(guò)2片SRAM的雙緩存結(jié)構(gòu)實(shí)現(xiàn)圖像的乒乓控制

2014-07-28 16:45:28 2799

2799

來(lái)說(shuō),濾除噪聲、擴(kuò)展對(duì)比度、銳化以及色彩增強(qiáng)等處理能顯著提升視覺(jué)效果。這里設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng),包含增強(qiáng)對(duì)比度擴(kuò)展和色飽和度兩種處理方法,相比于DSP和ASIC方案來(lái)說(shuō),FPGA在性能和靈活性方面具有絕對(duì)優(yōu)勢(shì),應(yīng)用FPGA設(shè)計(jì)視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

慕課電子科技大學(xué).嵌入式系統(tǒng).第三章.ARM微處理器編程基礎(chǔ)和接口實(shí)驗(yàn).ARM微處理器編程基礎(chǔ)實(shí)驗(yàn)0 目錄3 ARM微處理器編程基礎(chǔ)和接口實(shí)驗(yàn)3.1 ARM微處理器編程基礎(chǔ)實(shí)驗(yàn)3.1.1課堂重點(diǎn)

2021-12-14 09:04:05

慕課電子科技大學(xué).嵌入式系統(tǒng).第三章.ARM微處理器編程基礎(chǔ)和接口實(shí)驗(yàn).ARM設(shè)備接口實(shí)驗(yàn)0 目錄3 ARM微處理器編程基礎(chǔ)和接口實(shí)驗(yàn)3.2 ARM設(shè)備接口實(shí)驗(yàn)3.2.1課堂重點(diǎn)3.2.2測(cè)試與作業(yè)

2021-12-14 08:46:10

請(qǐng)教各位,最近需要BF706采集數(shù)據(jù)然后通過(guò)USB接口實(shí)時(shí)發(fā)送到上位機(jī)然后存儲(chǔ),沒(méi)有使用RTOS,通過(guò)配置BF706的USB控制器,如何實(shí)現(xiàn)?datasheet中有關(guān)USB部分的描述很不明確,ADI官方有沒(méi)有類似的關(guān)于USB實(shí)時(shí)傳輸?shù)睦蹋坑羞^(guò)相關(guān)開(kāi)發(fā)經(jīng)驗(yàn)的大神請(qǐng)指點(diǎn),多謝。

2018-08-08 07:20:20

TC1728沒(méi)有LIN接口,只有UART接口。可以用UART接口實(shí)現(xiàn)LIN接口嗎?

2024-02-06 06:51:22

android獲取藍(lán)牙MAC接口實(shí)現(xiàn)的代碼流程是怎樣的?

2022-03-03 07:02:57

`本節(jié)知識(shí)介紹:FPGA接口實(shí)現(xiàn)文本液晶顯示模塊文本液晶顯示模塊是基于廉價(jià)和易于使用微控制器或FPGA接口實(shí)現(xiàn)的。下面是一個(gè)1行×16字符模塊:要控制液晶顯示模塊,你需要11個(gè)IO引腳來(lái)驅(qū)動(dòng)一個(gè)8

2012-03-14 11:11:15

;quot;,意為串行外圍接口,是Motorola首先在其MC68HCXX系列處理器上定義的。SPI接口主要應(yīng)用在EEPROM、FLASH、實(shí)時(shí)時(shí)鐘、AD轉(zhuǎn)換器,還有數(shù)字信號(hào)處理器和數(shù)字信號(hào)解碼器之間。SPI

2012-03-26 15:47:42

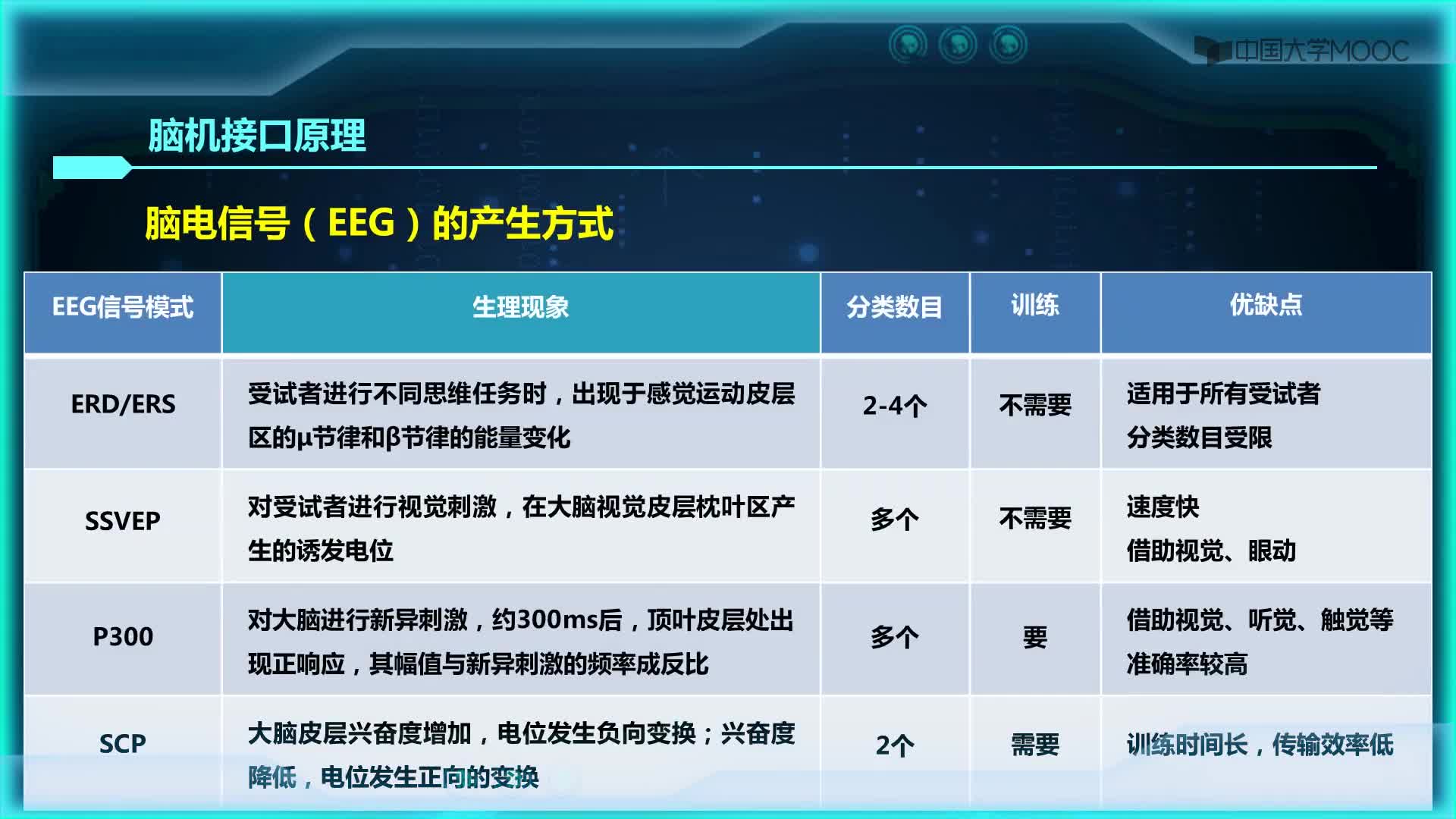

申請(qǐng)理由:我們希望申請(qǐng)?jiān)囉迷摽铋_(kāi)發(fā)板來(lái)作為我們項(xiàng)目的主要模塊,借以對(duì)腦電信號(hào)采集的數(shù)據(jù)進(jìn)行分析處理,并將其數(shù)據(jù)用于對(duì)飛行器的控制。項(xiàng)目描述:基于腦機(jī)接口(BCI)的飛行器控制系統(tǒng):腦機(jī)接口(BCI

2015-06-25 14:05:36

操作,生成輸出信號(hào)。FPGA 一方面將數(shù)據(jù)串行發(fā)送給232 接口芯片,然后通過(guò)232 串口發(fā)送給上位機(jī)。上位機(jī)可通過(guò)監(jiān)視軟件實(shí)時(shí)觀測(cè)溫度值和控制量的變化情況,方便系統(tǒng)調(diào)試與*估;另一方面從數(shù)據(jù)中提

2019-06-18 05:00:08

個(gè)值得探討的問(wèn)題。一般來(lái)說(shuō),嵌入式CPU都具有低功耗的工作模式,如果在任務(wù)調(diào)度的空閑時(shí)間,使CPU進(jìn)入這種模式,就能大幅度降低系統(tǒng)功耗。本文以嵌入式實(shí)時(shí)操作系統(tǒng)μC/OS-II在飛思卡爾8位單片機(jī)

2019-05-16 07:00:08

介紹了基于5l單片機(jī)和步進(jìn)電機(jī)的可控腦手術(shù)鉆的研制。系統(tǒng)設(shè)計(jì)是在提高實(shí)時(shí)控制的可靠性和快速性基礎(chǔ)上,采用了雙單片機(jī)的系統(tǒng)結(jié)構(gòu)和流水線查詢技術(shù)。系統(tǒng)硬件外部接線簡(jiǎn)單,具有可靠的抗干擾保護(hù)措施和良好的實(shí)時(shí)控制性。

2011-03-08 11:14:06

外部處理器直接訪問(wèn)多達(dá)4個(gè)EZ-USB FX3內(nèi)部緩沖區(qū)。USB3.0的控制交由FPGA,數(shù)據(jù)輸出到PC機(jī)進(jìn)行接收。圖 2 USB3.0從器件FIFO接口2.2 FPGA主控模塊本設(shè)計(jì)的主控模塊采用

2018-08-09 14:18:42

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì)

2017-12-26 16:51:49

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì),介紹了CCD圖像傳感器和ADV7181B解碼芯片的I2C配置原理。給出了乒乓緩存的原理與實(shí)現(xiàn)方法,同時(shí)給出了ADV7181B與FPGA等芯片組成視頻處理電路的設(shè)計(jì)和FPGA的程序?qū)崿F(xiàn)方法。

2017-11-17 13:59:48

接口實(shí)時(shí)顯示檢測(cè)得到的圖像邊緣信息。

1.3.2 系統(tǒng)的設(shè)計(jì)流程

本課題基于FPGA實(shí)現(xiàn),主要涉及到以下內(nèi)容:1、攝像頭接口的驅(qū)動(dòng);2、圖像數(shù)據(jù)的實(shí)時(shí)捕獲;3、彩色圖像到灰度圖像的轉(zhuǎn)換;4、中值濾波

2023-06-21 18:47:51

如表1所示,受試者是5名健康男性。正確判斷時(shí),在刺激模塊停止閃爍的同時(shí),光標(biāo)立刻移向受試者注視的模塊。基于瞬態(tài)視覺(jué)誘發(fā)電位的腦機(jī)接口實(shí)驗(yàn)表明,本文給出的基于FPGA的腦機(jī)接口實(shí)時(shí)系統(tǒng)的方案是可行

2019-06-04 05:00:19

基于FPGA的B超數(shù)字圖像實(shí)時(shí)采集系統(tǒng)

2012-08-17 11:55:04

接口信號(hào)提供電信號(hào)支持。第二,FPGA的I/O必須有足夠的gearing邏輯來(lái)支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應(yīng)現(xiàn)代攝像機(jī)對(duì)于緊湊外形的要求。 具有

2018-11-05 11:08:31

基于FPGA的高速實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2012-08-20 20:00:14

基于fpga的實(shí)時(shí)視頻處理系統(tǒng)難點(diǎn)在哪,解決方案,誰(shuí)能幫下忙

2014-04-08 19:03:45

見(jiàn)到一種方法是被大家所公認(rèn)的。就現(xiàn)在而言,基于腦電波的疲勞駕駛檢測(cè)系統(tǒng)被國(guó)際上視作為未來(lái)該領(lǐng)域的發(fā)展趨勢(shì)。腦電信號(hào)是一種微弱的生物信號(hào),并且極易受到干擾。基于腦電的疲勞駕駛檢測(cè)系統(tǒng)的設(shè)計(jì)思想為:首先要

2019-06-17 05:00:06

基于JTAG接口實(shí)現(xiàn)ARM的FPGA在線配置設(shè)計(jì)

2012-08-19 23:17:24

基于Proteus的Arm處理器的SPI接口實(shí)現(xiàn)

2010-02-10 10:41:58

如何使用編碼器接口實(shí)現(xiàn)定位?

2022-02-11 07:32:50

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)的應(yīng)用越來(lái)越廣泛。那么,我們?cè)撛趺蠢?b class="flag-6" style="color: red">FPGA與ADSP TS201設(shè)計(jì)總線接口呢?

2019-08-09 06:56:11

本文的點(diǎn)陣LED顯示系統(tǒng)以單片機(jī)89C51為基礎(chǔ),加以外圍電路,利用RS-232接口實(shí)現(xiàn)與計(jì)算機(jī)實(shí)時(shí)通信,可實(shí)現(xiàn)漢字、數(shù)字及各種字符的多種方式和速 度的顯示。

2021-06-03 06:26:15

如何利用串口實(shí)現(xiàn)智能大棚系統(tǒng)的設(shè)計(jì)?

2021-10-20 06:49:26

如何實(shí)現(xiàn)串口實(shí)時(shí)通信?

2017-08-14 09:10:36

如果不使用FPGA自帶的SERDES,可否適用LVDS接口實(shí)現(xiàn)其功能?

2023-05-08 17:37:48

學(xué)fpga的內(nèi)部結(jié)構(gòu)和各接口實(shí)驗(yàn)怎么學(xué),看什么資料

2014-05-10 18:38:05

原標(biāo)題:微機(jī)原理與接口實(shí)驗(yàn)箱, 教學(xué)實(shí)驗(yàn)箱 ,教學(xué)儀器SG-8086K 微機(jī)原理與接口實(shí)驗(yàn)箱 一、實(shí)驗(yàn)箱組成:硬件:(1)微機(jī)系統(tǒng)擴(kuò)展:8088CPU,64K監(jiān)控程序存儲(chǔ)器,64K用戶程序和數(shù)

2021-09-10 08:12:14

腦電信號(hào)EEG(Electroencephalograph)是人體一種基本生理信號(hào),具有重要的臨床診斷和醫(yī)療價(jià)值。南于腦電信號(hào)自身具有非平穩(wěn)性隨機(jī)的特點(diǎn),因此,對(duì)其實(shí)時(shí)濾波具有相當(dāng)難度。自從

2019-08-23 07:57:41

實(shí)時(shí)進(jìn)行目標(biāo)提取和偏差量計(jì)算。疊加視頻可通過(guò)DVI數(shù)字接口或模擬接口實(shí)時(shí)顯示。利用圖像高分辨率特性,系統(tǒng)可實(shí)現(xiàn)運(yùn)動(dòng)目標(biāo)精確跟蹤。

2021-06-01 07:03:16

腦電信號(hào)(EEG)是一種典型的生物電信號(hào),是大腦皮層腦神經(jīng)細(xì)胞電活動(dòng)的總體反映,其中包含了大量的生理和病理信息,是臨床檢測(cè)的重要生理參數(shù)之一,也是認(rèn)知科學(xué)、腦機(jī)接口和警覺(jué)度等領(lǐng)域研究的重要手段

2019-09-27 07:04:44

的信息并行存在,因此可以并行對(duì)其施以相同的操作,使得圖像處理的速度大大提高,這正好適合映射到FPGA架構(gòu)中用硬件算法得以實(shí)現(xiàn)。本篇闡述了基于FPGA設(shè)計(jì)一個(gè)能夠實(shí)時(shí)采集、實(shí)時(shí)處理并實(shí)時(shí)顯示的數(shù)字圖像處理系統(tǒng)的設(shè)計(jì)思想和流程,分析了攝像頭接口的時(shí)序;闡述了圖像...

2021-07-28 06:06:26

求助,請(qǐng)知道一下腦機(jī)接口入門,哪位大神懂腦機(jī)接口呀?本人很感興趣,但不知道怎么入門?

2014-01-14 16:39:52

。FPGA一方面將數(shù)據(jù)串行發(fā)送給 232接口芯片,然后通過(guò) 232串口發(fā)送給上位機(jī)。上位機(jī)可通過(guò)監(jiān)視軟件實(shí)時(shí)觀測(cè)溫度值和控制量的變化情況,方便系統(tǒng)調(diào)試與評(píng)估;另一方面從數(shù)據(jù)中提取出控制量,將其串行輸出到DAC

2020-08-19 09:29:48

終端測(cè)試系統(tǒng)通訊模塊的設(shè)計(jì)原理,重點(diǎn)介紹了支持熱插拔的CPCI接口電源電路分析、FPGA與PCI9030接口模塊時(shí)序分析和在Windriver軟件環(huán)境下的驅(qū)動(dòng)程序的開(kāi)發(fā),為AFDX上位機(jī)底層驅(qū)動(dòng)接口的開(kāi)發(fā)和軟件界面的開(kāi)發(fā)以及AFDX交換機(jī)的研發(fā)打下了良好的基礎(chǔ)。

2019-06-20 06:47:12

O 引言誘發(fā)電位是指對(duì)神經(jīng)系統(tǒng)某一特定部位給予特定刺激后在大腦皮層所產(chǎn)生的特定電活動(dòng),對(duì)于神經(jīng)系統(tǒng)功能性異常的疾病有獨(dú)特的檢測(cè)診斷能力,也是大腦認(rèn)知和腦機(jī)接口研究常用的技術(shù)手段。誘發(fā)電位儀通常包括

2019-05-16 07:00:09

XC2S200型FPGA器件實(shí)現(xiàn)。采用Spansion公司的NOR Flash存儲(chǔ)器來(lái)存放配置文件,其型號(hào)為S29GL512N,容量為512 Mb。系統(tǒng)總體框圖如圖3所示。上位機(jī)軟件包括Flash燒寫(xiě)

2019-05-30 05:00:05

摘要:為了改善實(shí)時(shí)圖像輸出質(zhì)量,研究基于SDI接口的增強(qiáng)顯示系統(tǒng)軟硬件設(shè)計(jì)。利用模塊化思想提出一個(gè)基于SDI接口輸出的硬件架構(gòu),以FPGA作為處理核心,通過(guò)2片SRAM的雙緩存結(jié)構(gòu)實(shí)現(xiàn)圖像的乒乓控制

2019-06-21 05:00:07

單片機(jī)人機(jī)接口實(shí)例集

2006-03-22 21:04:57 396

396 單片機(jī)人機(jī)接口實(shí)例集

2006-03-23 19:37:58 72

72 本文提出了一種基于USB 接口的FPGA SelectMap 配置方式的實(shí)現(xiàn)方案。方案以大容量Spartan3 FPGA 作為配置目標(biāo),選用Cypress EZ-USB FX2LP 作為USB 設(shè)備芯片,采用其內(nèi)置的端點(diǎn)FIFO 和GPIF 狀態(tài)

2009-05-26 10:25:33 28

28 應(yīng)用串行外圍接口實(shí)現(xiàn)多微控制器間通信:

2009-06-23 10:54:05 24

24 :本文介紹了基于SharcFIN 芯片的數(shù)字接收機(jī)ICS554 在軟件高頻雷達(dá)上與通用信號(hào)處理平臺(tái)之間的接口實(shí)現(xiàn),給出了ADSP-TS101S 通過(guò)該接口實(shí)現(xiàn)雷達(dá)信號(hào)處理系統(tǒng)與ICS554 之間實(shí)時(shí)通

2009-12-16 12:38:57 16

16 本文介紹了一種基于FPGA 的光纖陀螺慣導(dǎo)系統(tǒng)溫控電路接口設(shè)計(jì)。主要說(shuō)明了溫控電路整體結(jié)構(gòu),溫控電路工作流程,FPGA 與外圍電路的通信接口和FPGA 的邏輯設(shè)計(jì)等幾個(gè)方面。

2010-01-13 15:20:38 24

24 網(wǎng)絡(luò)講壇:實(shí)時(shí)系統(tǒng)與FPGA-labview視頻教程

2010-03-26 16:44:20 172

172 AD轉(zhuǎn)換接口實(shí)驗(yàn)

實(shí)驗(yàn)?zāi)康?

1、掌握A/D轉(zhuǎn)換器0809的工作原理及其與8031的連接方法。

2、掌握A/D轉(zhuǎn)換的程序設(shè)計(jì)。

(一)

2008-10-17 22:23:12 3528

3528 基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來(lái)記錄信息的

2009-12-16 10:20:55 576

576

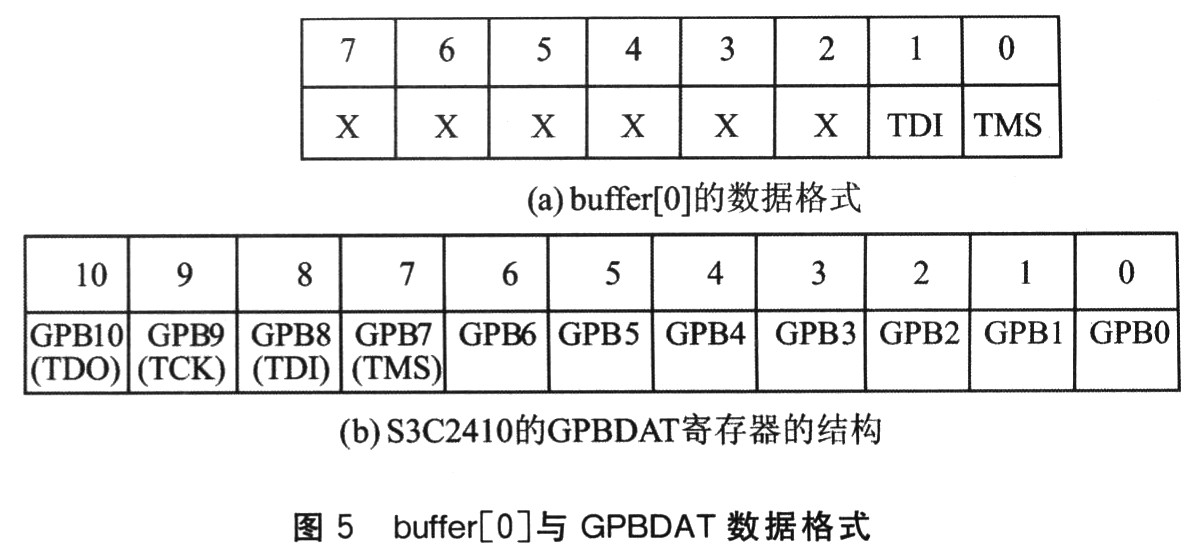

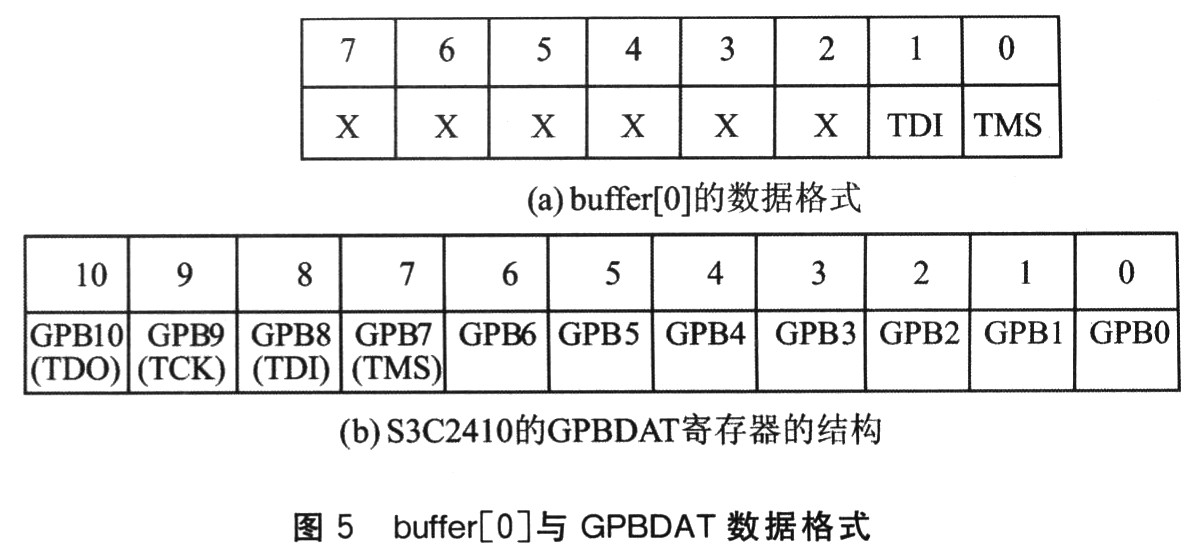

基于JTAG接口實(shí)現(xiàn)ARM的FPGA在線配置設(shè)計(jì)

引 言???? 為了解決不同標(biāo)準(zhǔn)間無(wú)線接口技術(shù)的互通和兼容,人們提出了軟件無(wú)線電(Software Defined Radio,SDR)技術(shù)

2010-02-09 10:56:10 3142

3142

SPI接口實(shí)險(xiǎn),LED數(shù)據(jù)管顯示。 1、程序通過(guò)SPI接口輸出數(shù)據(jù)到HC595芯片驅(qū)動(dòng)LED數(shù)據(jù)管簡(jiǎn)單顯示。 2、內(nèi)部1 M晶振,程序采用單任務(wù)方式,軟件延時(shí)。

2010-06-30 11:19:20 1196

1196 文中介紹了連接電子式互感器與保護(hù)、測(cè)量設(shè)備的合并單元及功能模型,分析了個(gè)丙單元與電子式互感器借口通信具有多任務(wù)并行處理等特點(diǎn),提出基于FPGA技術(shù)實(shí)現(xiàn)此接口方法。

2011-02-25 15:18:42 36

36 隨著 FPGA 的設(shè)計(jì)速度、尺寸和復(fù)雜度明顯增長(zhǎng),使得整個(gè)設(shè)計(jì)流程中的實(shí)時(shí)驗(yàn)證和調(diào)試成為當(dāng)前FPGA 系統(tǒng)的關(guān)鍵部分。獲得FPGA 內(nèi)部信號(hào)有限、FPGA 封裝和印刷電路板(PCB)電氣噪聲,這一

2011-06-10 15:42:28 28

28 介紹了一種高速實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)。該系統(tǒng)以FPGA作為邏輯控制的核心,以USB2.0作為與上位機(jī)數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">接口,能同時(shí)支持單端16路和差分8路模擬信號(hào)輸入,最大采樣率為200 kHz,

2011-09-29 17:16:36 62

62 基于FPGA的VGA接口實(shí)現(xiàn)和字符顯示論文

2015-10-29 17:18:24 8

8 基于FPGA的高速數(shù)據(jù)采集系統(tǒng)接口設(shè)計(jì).

2016-05-10 17:06:40 27

27 Xilinx FPGA工程例子源碼:基于FPGA實(shí)時(shí)處理的雙目測(cè)距系統(tǒng)

2016-06-07 15:07:45 37

37 多分辨率圖像實(shí)時(shí)采集系統(tǒng)的FPGA邏輯設(shè)計(jì)

2016-08-29 15:02:03 6

6 基于FPGADSP的實(shí)時(shí)圖像消旋系統(tǒng),下來(lái)看看

2016-08-26 12:58:19 4

4 基于FPGA的JPEG實(shí)時(shí)圖像編解碼系統(tǒng)

2016-08-29 16:05:01 15

15 基于FPGA的實(shí)時(shí)圖像預(yù)處理技術(shù)在汽車夜視系統(tǒng)中的應(yīng)用

2016-08-29 23:19:35 9

9 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 一種基于FPGA的雙接口NFC芯片驗(yàn)證系統(tǒng)_彭廣

2017-01-03 15:24:45 2

2 基于FPGA的多路數(shù)據(jù)實(shí)時(shí)采集與傳輸系統(tǒng)_馮希辰

2017-01-08 10:30:29 3

3 基于FPGA的高精度電流實(shí)時(shí)監(jiān)測(cè)系統(tǒng)設(shè)計(jì)_楊鷗寧

2017-01-31 21:14:56 4

4 基于FPGA的軟硬件協(xié)同實(shí)時(shí)紙病圖像處理系統(tǒng)_齊璐

2017-03-19 19:07:17 0

0 非實(shí)時(shí)考勤系統(tǒng)的通訊接口設(shè)計(jì)

2017-10-17 10:47:40 0

0 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

9 基于FPGA的實(shí)時(shí)NPR系統(tǒng)。實(shí)驗(yàn)結(jié)果表明,該系統(tǒng)對(duì)高幀率、高分辨率的視頻做實(shí)時(shí)NPR處理具有運(yùn)算速度快、系統(tǒng)穩(wěn)定等特點(diǎn),同時(shí)還具有體積小、便于攜帶等優(yōu)點(diǎn)。

2017-11-17 06:45:01 1679

1679

NI VeriStand是一款用于配置實(shí)時(shí)測(cè)試系統(tǒng)應(yīng)用的軟件環(huán)境,如硬件在環(huán)(HIL)測(cè)試系統(tǒng)等。當(dāng)向NI VeriStand添加實(shí)時(shí)I/O接口時(shí),用戶能夠快速配置多種標(biāo)準(zhǔn)模擬、數(shù)字和通信總線接口

2017-11-18 07:47:35 8846

8846

腦機(jī)接口BCI(Brain Computer Interface)是一種新穎的人機(jī)接口方式。它的定義是:不依賴于腦的正常輸出通路(外周神經(jīng)系統(tǒng)及肌肉組織)的腦-機(jī)(計(jì)算機(jī)或其他裝置)通訊系統(tǒng)

2017-11-24 15:12:34 872

872

在高速圖像采集中.需要對(duì)采集的大量數(shù)據(jù)進(jìn)行實(shí)時(shí)存儲(chǔ)。介紹了一種基于FPGA控制的高速圖像實(shí)時(shí)存儲(chǔ)系統(tǒng),該系統(tǒng)能在脫機(jī)方式下由FPGA直接控制IDE硬盤,實(shí)現(xiàn)高速圖像的實(shí)時(shí)存儲(chǔ),并通過(guò)PCI接口對(duì)硬盤進(jìn)行事后訪問(wèn)。目前,采用單硬盤時(shí)的記錄速度可達(dá)到24 MB/s。

2021-01-22 14:29:00 9

9 來(lái)看一下它的組成和特征吧! 進(jìn)口實(shí)時(shí)熒光定量pcr儀【云唐科器】有哪些部分組成? 由三部分組成:第一部分溫度控制系統(tǒng),實(shí)質(zhì)上是由標(biāo)準(zhǔn)的加熱/冷卻系統(tǒng)和熱蓋組成。 第二部分是由光學(xué)元件組成的熒光檢測(cè)系統(tǒng),包括激發(fā)光源,光學(xué)濾光片,變焦鏡頭和檢測(cè)

2021-02-25 15:35:01 2155

2155 介紹了一種雙接口NFC芯片的架構(gòu)和功能,提岀并實(shí)現(xiàn)了用于該雙接口NFC芯片的FPGA驗(yàn)證系統(tǒng)及其驗(yàn)證流程。該FPGA驗(yàn)證系統(tǒng)包括FPGA、PIC單片機(jī)以及帶NFC功能的手機(jī),可有效縮短芯片設(shè)計(jì)周期

2021-05-26 14:03:26 16

16 算法得以實(shí)現(xiàn)。 本篇闡述了基于FPGA設(shè)計(jì)一個(gè)能夠實(shí)時(shí)采集、實(shí)時(shí)處理并實(shí)時(shí)顯示的數(shù)字圖像處理系統(tǒng)的設(shè)計(jì)思想和流程,分析了攝像頭接口的時(shí)序;闡述了圖像信息的捕獲原理;詳細(xì)介紹了圖像邊緣檢測(cè)部分各模塊的功能;重點(diǎn)介紹了具有去噪

2021-06-30 09:49:01 1916

1916 ARM與FPGA的接口實(shí)現(xiàn)的解析(應(yīng)廣單片機(jī))-該文檔為ARM與FPGA的接口實(shí)現(xiàn)的解析詳述資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-22 09:47:55 14

14 基于FPGA的SDRAM串口實(shí)驗(yàn)(嵌入式開(kāi)發(fā)板實(shí)驗(yàn)報(bào)告)-基于FPGA的SDRAM串口實(shí)驗(yàn),verilog語(yǔ)言編寫(xiě)

2021-08-04 09:43:17 37

37 C#-Interface接口實(shí)現(xiàn)(安徽理士電源技術(shù)有限公司招聘信息)-該文檔為C#-Interface接口實(shí)現(xiàn)講解文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,,

2021-09-28 09:42:34 3

3 電子發(fā)燒友網(wǎng)站提供《基于XML語(yǔ)言描述的接口實(shí)現(xiàn)方法.pdf》資料免費(fèi)下載

2023-11-06 10:39:08 0

0 汽車用c總線接口實(shí)時(shí)時(shí)鐘模塊內(nèi)置調(diào)頻32.768 kHz晶體單元和DTCXO,高穩(wěn)定性和電源切換。接口類型我2C-Bus接口(400kHz)界面電壓范圍2.5V ~ 5.5V溫度補(bǔ)償電壓范圍2.0V

2024-01-04 17:35:38 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論