練習九.利用狀態機的嵌套實現層次結構化設計目的:1.運用主狀態機與子狀態機產生層次化的邏輯設計;

2.在結構化設計中靈活使用任務(task)結構。

在上一節,我們學習了如何使用狀態機的實例。實際上,單個有限狀態機控制整個邏輯電路的運轉在實際設計中是不多見,往往是狀態機套用狀態機,從而形成樹狀的控制核心。這一點也與我們提倡的層次化、結構化的自頂而下的設計方法相符,下面我們就將提供一個這樣的示例以供大家學習。

該例是一個簡化的EPROM的串行寫入器。事實上,它是一個EPROM讀寫器設計中實現寫功能的部分經刪節得到的,去除了EPROM的啟動、結束和EPROM控制字的寫入等功能,只具備這樣一個雛形。工作的步驟是:1.地址的串行寫入;2.數據的串行寫入;3.給信號源應答,信號源給出下一個操作對象;4.結束寫操作。通過移位令并行數據得以一位一位輸出。

模塊源代碼:

module writing(reset,clk,address,data,sda,ack);

? input reset,clk;

? input[7:0] data,address;

? output sda,ack; //sda負責串行數據輸出;

? //ack是一個對象操作完畢后,模塊給出的應答信號。

? reg link_write; //link_write 決定何時輸出。

? reg[3:0] state; //主狀態機的狀態字。

? reg[4:0] sh8out_state; //從狀態機的狀態字。

? reg[7:0] sh8out_buf;??? //輸入數據緩沖。

? reg finish_F;?????????? //用以判斷是否處理完一個操作對象。

? reg ack;

? parameter

??? idle=0,addr_write=1,data_write=2,stop_ack=3;

? parameter

??? bit0=1,bit1=2,bit2=3,bit3=4,bit4=5,bit5=6,bit6=7,bit7=8;

? assign?? sda = link_write? sh8out_buf[7] : 1'bz;

? always @(posedge clk)

??? begin

??????? if(!reset)?????????????? //復位。

????????? begin

???????????? link_write<= 0;

???????????? state??? <= idle;

???????????? finish_F <= 0;

???????????? sh8out_state<=idle;

?????????????????? ack<= 0;

???????????? sh8out_buf<=0;

????????? end

??????? else

????????? case(state)

????????? idle:??????????????????????

??????????? begin

??????????????? link_write? <= 0;

?????????????? state??? <= idle;

?????????????? finish_F <= 0;

?????????????? sh8out_state<=idle;

???????????????????? ack<= 0;

?????????????? sh8out_buf<=address;?

????????????? state??? <= addr_write;

??????????? end

????????? addr_write:???????? //地址的輸入。

??????????? begin

??????????????? if(finish_F==0)

????????????????? begin? shift8_out; end

??????????????? else

????????????????? begin

???????????????????? sh8out_state <= idle;

???????????????????? sh8out_buf?? <= data;

??????????????????????????? state <= data_write;

???????????????????????? finish_F <= 0;

????????????????? end

??????????? end

????????? data_write:?????? //數據的寫入。

??????????? begin

??????????????? if(finish_F==0)

????????????????? begin? shift8_out; end

??????????????? else

????????????????? begin

????????????????????? link_write <= 0;

?????????????????????????? state <= stop_ack;

??????????????????????? finish_F <= 0;?

???????????????????????????? ack <= 1;

????????????????? end

??????????? end????

????????? stop_ack:???????????? //完成應答。

??????????? begin

????????????????? ack <= 0;

????????????? state <= idle;

??????????? end

?????????

????????? endcase??????

??? end??????????????????????????

task shift8_out;??????????????? //串行寫入。

? begin

???? case(sh8out_state)

???? idle:

?????? begin

?????????? link_write? <= 1;

????????? sh8out_state <= bit0;

??????? end

???? bit0:

?????? begin

?????????? link_write <= 1;

???????? sh8out_state <= bit1;????????????????????????????????

?????????? sh8out_buf <= sh8out_buf<<1;

?????? end

???? bit1:

?????? begin

???????? sh8out_state<=bit2;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

???? bit2:

?????? begin

???????? sh8out_state<=bit3;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

???? bit3:

?????? begin

???????? sh8out_state<=bit4;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

???? bit4:

?????? begin

???????? sh8out_state<=bit5;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

????

???? bit5:

?????? begin

???????? sh8out_state<=bit6;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

???? bit6:

?????? begin

???????? sh8out_state<=bit7;

???????? sh8out_buf<=sh8out_buf<<1;

?????? end

???? bit7:

?????? begin

???????? link_write<= 0;

???????? finish_F<=finish_F+1;???????????????????????????????

?????? end?

??????

???? endcase

? end

endtask

endmodule?????????

測試模塊源代碼:

`timescale 1ns/100ps

`define clk_cycle 50

module writingTop;

? reg reset,clk;

? reg[7:0] data,address;

? wire ack,sda;

? always #`clk_cycle? clk = ~clk;

? initial

??? begin

??????????? clk=0;

??????????? reset=1;

??????????? data=0;

??????????? address=0;

??????????? #(2*`clk_cycle) reset=0;

??????????? #(2*`clk_cycle) reset=1;

?????? #(100*`clk_cycle) $stop;

??? end

? always @(posedge ack)????? //接收到應答信號后,給出下一個處理對象。

??? begin

??????????? data=data+1;

??????????? address=address+1;

??? end????????

? writing writing(.reset(reset),.clk(clk),.data(data),

????????????????? .address(address),.ack(ack),.sda(sda));?

endmodule???????

仿真波形:[[wysiwyg_imageupload:252:height=174,width=496]]

練習:仿照上例,編寫一個實現EPROM內數據串行讀取的模塊。編寫測試模塊,給出仿真波形。

利用狀態機的狀態機實現層次結構化設計

- 狀態機(27117)

- FGPA(15865)

相關推薦

狀態機編程實例-狀態表法

上篇文章,使用嵌套switch-case法的狀態機編程,實現了一個炸彈拆除小游戲。本篇,繼續介紹狀態機編程的第二種方法:狀態表法,來實現炸彈拆除小游戲的狀態機編程。

2023-06-20 09:05:05 1190

1190

1190

1190

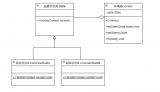

Spring狀態機的實現原理和使用方法

說起 Spring 狀態機,大家很容易聯想到這個狀態機和設計模式中狀態模式的區別是啥呢?沒錯,Spring 狀態機就是狀態模式的一種實現,在介紹 Spring 狀態機之前,讓我們來看看設計模式中的狀態模式。

2023-12-26 09:39:02 664

664

664

664

Verilog狀態機+設計實例

在verilog中狀態機的一種很常用的邏輯結構,學習和理解狀態機的運行規律能夠幫助我們更好地書寫代碼,同時作為一種思想方法,在別的代碼設計中也會有所幫助。 一、簡介 在使用過程中我們常說

2024-02-12 19:07:39 1818

1818

1818

1818

狀態機

控制狀態機控制狀態機的初始化和狀態轉換的最佳方法是使用枚麗型輸入控件。一般使用自定義類型的枚麗變量。使用子定義類型的枚麗變量可以是控件和實例乊間存在關聯,使得添加或刪除狀態時所有的枚麗型輸入控件副本自動更新。

2014-02-13 12:39:31

狀態機如何暫停

程序一運行 就開始自動運行程序 狀態機各種各種狀態開始執行 我這里是布爾變量 每一秒點亮一個布爾按鈕。我現在想在界面增加一個暫停按鈕 當點暫停時候 此時暫停按鈕文字成為繼續 如果 狀態機執行第二步

2018-04-09 09:23:30

狀態機是什么意思

剛開始學fpga,讀資料,有些名詞不太理解,比如狀態機,我只知道fpga就是由查找表和觸發器構成的,狀態機這個概念是怎么提出來的,干什么使得,求大神講解,什么情況下用到

2013-04-25 18:35:55

狀態機的相關資料下載

share,作者:亞索老哥)),原來狀態機還可以這么簡單地玩~~亞索老哥提出的狀態機六步法(1)、定義狀態接口(2)、定義系統當前狀態指針(3)、定義具體狀態,根據狀態遷移圖來實現具體功能和狀態切換(4)、定義主程序上下文操作接口(6)、主程序通過上下文操作接口來控制系統當前狀態的變化亞索老哥的狀態機例程

2022-02-15 06:01:46

狀態機編程

等待一段時間后,光標的位置就會右移,表示對最后輸入字符的確認。因此,按鍵輸入接口設計和實現的核心,更多的體現在軟件接口處理程序的設計中。下面將以此為例,介紹有限狀態機的分析設計原理,以及基于狀態機思想

2008-07-10 18:00:24

狀態機跳躍錯誤的解決辦法?

大家好,我對狀態機有疑問。我寫了一個狀態機來實現一些功能,設備是virtex-ii。機器中有26個狀態,其中4個是A,B,C,D,E;輸入信號為rdy_i和smp_rdy_i,輸出信號為p_o

2020-07-08 10:51:29

FPGA/CPLD狀態機穩定性研究

而言,狀態機更加穩定,運行模式類似于CPU,易于實現順序控制等.用VHDL語言描述狀態機屬于一種高層次建模,結果經常出現一些出乎設計者意外的情況:在兩個狀態轉換時,出現過渡狀態.在運行過程中,進入非法

2012-01-12 10:48:26

JKI狀態機如何中止后面的狀態

如題,JKI狀態機中假如我點確定按鈕,有一個狀態序列開始執行。但是中途我點擊個停止按鈕,以后的狀態不再執行,回到等待狀態。請問用JKI狀態機能實現嗎?

2018-12-13 08:30:57

LabVIEW事件狀態機

后右鍵的復制方式創建每個新分支,少出現連線的差錯,同時也可以在每條線上備注用于區分。這種用到事件狀態機比較合適用于傳輸每次狀態下共享的或者改變的事件,數據以流的形式在每個狀態傳遞。控制每個狀態的標簽

2019-07-06 14:31:33

LabVIEW程序設計模式研究和探討(四)—狀態機和事件結構結合

本帖最后由 zhihuizhou 于 2011-12-27 11:04 編輯

本節將介紹如何將狀態機與事件結構結合起來形成一種新的、穩定的模式。這樣可以同時避免基本狀態機的第(1~5)個

2011-12-27 11:01:31

Labview狀態機

本帖最后由 afnuaa 于 2017-5-24 11:22 編輯

狀態機是一種普遍而有效的架構,我們可以利用狀態機設計模式來實現狀態圖或流程圖的算法。State Machines

2017-05-23 17:11:34

MCU裸機編程狀態機的定義與注意事項是什么

MCU裸機編程的狀態機框架--第一部分1 狀態機的概念1.1 狀態機的要素1.2 狀態遷移表1.3 狀態機思路實現一個時鐘程序1.4 狀態機應用的注意事項1.5 更復雜的狀態機FSM編程是裸機編程

2022-02-14 06:02:46

Verilog實驗,交通燈的狀態機和非狀態機實現

本帖最后由 御宇1995 于 2015-6-6 15:06 編輯

實驗課要用FPGA(Altera的cycloneIV)實現交通燈,有用狀態機和非狀態機兩種方法,以下是代碼狀態機實現(一個數

2015-06-06 15:03:52

labVIEW狀態機在實戰中的應用(基礎)

問題:1.一個While循環+事件結構 組成的狀態機(最簡單的)2.一個Whie循環+用戶事件+事件結構3.隊列消息+while循環+事件結構 組成的狀態機(較復雜)4.隊列消息+while循環+用戶

2018-12-25 16:53:35

labview狀態機基本類型順序結構

前文介紹了LV編程的重要概念---狀態機,狀態機是個基本概念或者說理論,其具體表現形式多種過樣,很難具體分類,我根據個人在編程實踐中的體會,歸納幾種常見類型.一、順序結構LV本身是有順序結構的,而且

2011-11-29 16:55:53

不同形式的狀態機占用資源問題

最近在CPLD里面做了一個4通道的模塊,每個模塊內都有一個狀態機,開始我是用的一段式狀態機寫發,資源不夠,然后我將狀態機的寫法改為3段式,(將狀態轉換一段,輸出一段)發現資源降低了很多,問下,一段和三段式的狀態機為什么對占用資源會有影響?或者談談一段和三段的綜合情況?

2015-01-21 14:07:40

什么是狀態機

一. 什么是狀態機我們以生活中的小區的停車系統為例:停車桿一般沒車的是不動的(初態),有車來的時候需要抬桿(狀態1),車通過需要放桿(狀態2),如果在放桿的過程中突然有車,又需要抬桿(狀態3

2022-01-06 08:01:00

什么是狀態機

目錄1 前言2 狀態機2.1 什么是狀態機2.2 狀態機的概念2.3 使用狀態機寫鍵盤的思路3 代碼實例3.1 使用軟件3.2 protues電路圖3.2 狀態機部分程序3.3 Keil工程文件

2022-01-24 06:23:02

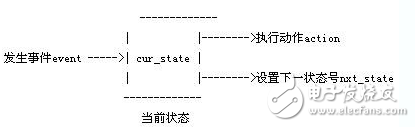

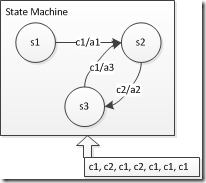

什么是狀態機?狀態機的三種實現方法

文章目錄1、什么是狀態機?2、狀態機編程的優點(1)提高CPU使用效率(2) 邏輯完備性(3)程序結構清晰3、狀態機的三種實現方法switch—case 法表格驅動法函數指針法小節摘要:不知道大家

2021-12-22 06:51:58

什么是有限狀態機呢

在嵌入式,機器人領域,由于多的復雜邏輯狀態,我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態機(finite-state machine),簡稱狀態機,是一種表示有限個狀態以及狀態間轉移等行為的數學模型。狀態機簡單來說

2021-12-20 06:51:26

關于狀態機結構

`老板交代一個任務,需要做一個測試機,完成IC的基本測試。本人白板一個,看了一些書籍和一些電子資料,做出了如下構想。考慮到一個IC有很多測試項,所以決定使用狀態機結構。如圖,我把IC的各個測試項做成

2013-08-07 11:16:10

單片機狀態機按鍵長按和短按實現

本文只介紹主要代碼段,完整代碼可參考我的“藍橋杯單片機狀態機按鍵按下和松開實現不同功能”藍橋杯單片機狀態機按鍵長按和短按實現不同功能定義變量key_time 按鍵計時時長key_time_flag按鍵計時標志位實現長按和短按不同功能的代碼段每過1ms,key_time自增1...

2022-01-06 08:26:45

取款機狀態機匯總

根據CLD的課程寫的取款機的邏輯。一邊看一邊改,從最簡單的狀態機,到事件驅動,生產者消費者模型,隊列狀態機,最后到AMC。實現的功能基本相同,但結構各有不同。取款機的邏輯非常簡單,前面板也沒有美化,只是實現了邏輯。附件提供給大家,希望和大家一起討論學習。

2017-08-01 16:25:25

如何利用狀態機進行編程呢

很多上升沿或下降沿,會引起誤判。這里我們使用狀態機的方式去處理,使用狀態機還有一個好處就是可以很方便的去判斷長按,短按,雙擊等狀態。當觸摸屏有觸點按下時,PENIRQ 引腳會輸出低電平,直到沒有觸摸...

2022-01-13 07:18:49

如何利用STM32去實現一種按鍵有限狀態機呢

STM32實現按鍵有限狀態機(超詳細,易移植)一、狀態機簡而言之,狀態機是使不同狀態之間的改變以及狀態時產生的相應動作的一種機制。1.1狀態機的四要素現態:狀態機當前狀態。觸發條件:改變當前狀態

2022-02-16 06:58:52

如何寫好狀態機

一篇經典文獻,詳細講解了一段、兩段、三段式狀態機的實現,效率、優缺點。看完后相信會對狀態機有一個詳細的了解。 狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以許 多公司

2011-10-24 11:43:11

如何用狀態機消抖法實現單片機矩陣鍵盤的控制

鍵盤不習慣,于是干脆解決這個問題,用狀態機消抖法實現矩陣鍵盤。代碼下載地址:https://gitee.com/zhang-yanping/singlechip.git下面是代碼/*功能:利用狀態機消

2022-02-17 07:47:36

問個關于狀態機的問題

問個關于狀態機的問題,書上說的三段式狀態機的第三段,同步時序的狀態輸出部分的狀態到底是當前態還是次態啊?有的書寫的是次態,case(next_state),有的寫的是case(cur_state)。

2014-09-22 20:42:17

如何寫好狀態機

如何寫好狀態機:狀態機是邏輯設計的重要內容,狀態機的設計水平直接反應工程師的邏輯功底,所以許多公司的硬件和邏輯工程師面試中,狀態機設計幾乎是必選題目。本章在引入

2009-06-14 19:24:49 96

96

96

96狀態機舉例

狀態機舉例

你可以指定狀態寄存器和狀態機的狀態。以下是一個有四種狀態的普通狀態機。 // These are the symbolic names for states// 定義狀態的符號名稱parameter [1

2009-03-28 15:18:28 893

893

893

893利用74LS161實現復雜狀態機

本文主要介紹了是如何利用74LS161實現復雜狀態機的。時序邏輯電路的數學模型是有限狀態機。有限狀態機它把復雜的控制邏輯分解成有限個穩定狀態,在每個狀態上判斷事件,變連續處理為離散數字處理,符合計算機的工作特點。本文主要討論使用MSI同步計數器74LS161進行復雜狀態機的設計。

2018-01-18 09:00:02 8299

8299

8299

8299

什么是狀態機 狀態機的描述三種方法

狀態機 1、狀態機是許多數字系統的核心部件,是一類重要的時序邏輯電路。通常包括三個部分:一是下一個狀態的邏輯電路,二是存儲狀態機當前狀態的時序邏輯電路,三是輸出組合邏輯電路。 2、根據狀態機的輸出

2020-11-16 17:39:00 24811

24811

24811

24811FPGA:狀態機簡述

本文目錄 前言 狀態機簡介 狀態機分類 Mealy 型狀態機 Moore 型狀態機 狀態機描述 一段式狀態機 二段式狀態機 三段式狀態機 狀態機優缺點 總結 擴展-四段式狀態機 01. 前言 狀態機

2020-11-05 17:58:47 6145

6145

6145

6145

什么是狀態機?狀態機5要素

玩單片機還可以,各個外設也都會驅動,但是如果讓你完整的寫一套代碼時,卻無邏輯與框架可言。這說明編程還處于比較低的水平,你需要學會一種好的編程框架或者一種編程思想!比如模塊化編程、狀態機編程、分層思想

2021-07-27 11:23:22 19223

19223

19223

19223

利用狀態機實現對tlc5620dac控制的實驗

利用狀態機實現對tlc5620dac控制的實驗(肇慶理士電源技術有限公司圖片)-利用狀態機實現對tlc5620dac控制的實驗,適合新手學習參考

2021-09-16 12:02:11 9

9

9

9利用狀態機實現對tlc5620dac控制的項目設計

利用狀態機實現對tlc5620dac控制的項目設計(開關電源技術趨勢)-利用狀態機實現對tlc5620dac控制的項目設計,適合感興趣的學習者學習.

2021-09-16 12:12:26 9

9

9

9利用狀態機實現對tlc5620dac控制.

利用狀態機實現對tlc5620dac控制.(西工大現代電源技術答案)-利用狀態機實現對tlc5620dac控制.適合感興趣的學習者學習.

2021-09-16 12:21:46 11

11

11

11狀態模式(狀態機)

share,作者:亞索老哥)),原來狀態機還可以這么簡單地玩~~亞索老哥提出的狀態機六步法(1)、定義狀態接口(2)、定義系統當前狀態指針(3)、定義具體狀態,根據狀態遷移圖來實現具體功能和狀態切換(4)、定義主程序上下文操作接口(6)、主程序通過上下文操作接口來控制系統當前狀態的變化亞索老哥的狀態機例程

2021-12-16 16:53:04 7

7

7

7狀態機要實現哪些內容

狀態機模式是一種行為模式,通過多態實現不同狀態的調轉行為的確是一種很好的方法,只可惜在嵌入式環境下,有時只能寫純C代碼,并且還需要考慮代碼的重入和多任務請求跳轉等情形,因此實現起來著實需要一番考慮

2023-06-22 14:26:00 411

411

411

411

如何在FPGA中實現狀態機

狀態機往往是FPGA 開發的主力。選擇合適的架構和實現方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執行基于序列和控制的行動, 比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動

2023-07-18 16:05:01 499

499

499

499

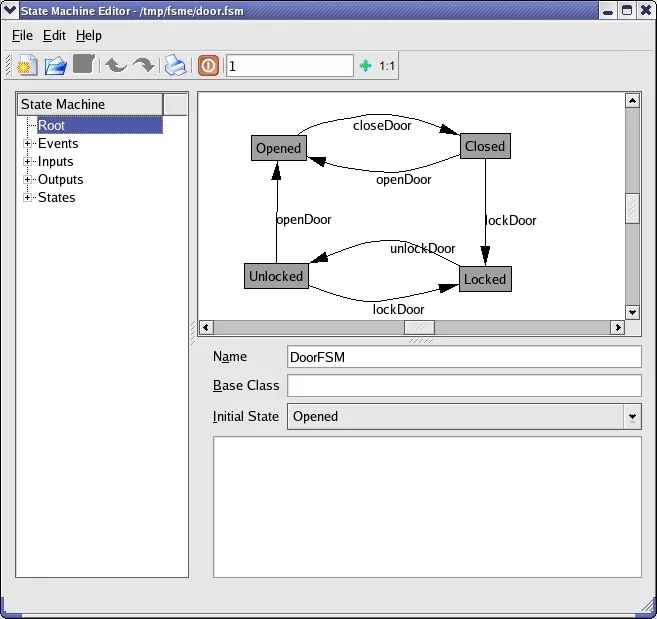

如何生成狀態機框架

生成狀態機框架 使用FSME不僅能夠進行可視化的狀態機建模,更重要的是它還可以根據得到的模型自動生成用C++或者Python實現的狀態機框架。首先在FSME界面左邊的樹形列表中選擇"Root

2023-09-13 16:54:15 618

618

618

618

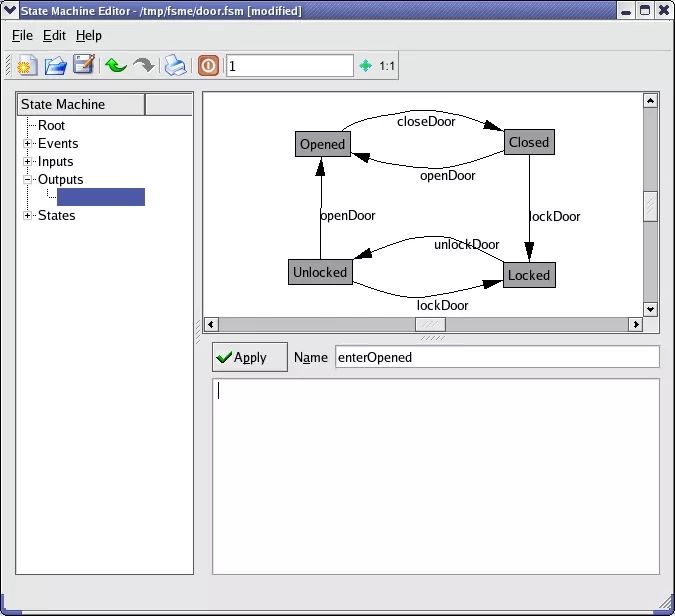

如何使用FSME來定制狀態機

定制狀態機 目前得到的狀態機已經能夠響應來自外部的各種事件,并適當地調整自己當前所處的狀態,也就是說已經實現了狀態機引擎的功能,接下來要做的就是根據應用的具體需求來進行定制,為狀態機加入與軟件系統

2023-09-13 16:57:37 821

821

821

821

什么是狀態機?狀態機的種類與實現

狀態機,又稱有限狀態機(Finite State Machine,FSM)或米利狀態機(Mealy Machine),是一種描述系統狀態變化的模型。在芯片設計中,狀態機被廣泛應用于各種場景,如CPU指令集、內存控制器、總線控制器等。

2023-10-19 10:27:55 3405

3405

3405

3405 電子發燒友App

電子發燒友App

評論