本文介紹了基于ZynqSoC的PMSM驅(qū)動(dòng)控制系統(tǒng),該控制系統(tǒng)使用ARM和FPGA相結(jié)合的形式實(shí)現(xiàn)了高性能、高集成度的控制算法。本系統(tǒng)中FPGA部分實(shí)現(xiàn)了計(jì)算并行度高、計(jì)算性能要求高的PMSM電流環(huán)矢量控制算法,ARM部分實(shí)現(xiàn)了可移植性強(qiáng)、算法種類多的速度控制算法、位置控制算法等。實(shí)驗(yàn)結(jié)果表明,該系統(tǒng)具備高性能和可擴(kuò)展性,能夠方便地應(yīng)用到不同的實(shí)際項(xiàng)目中。

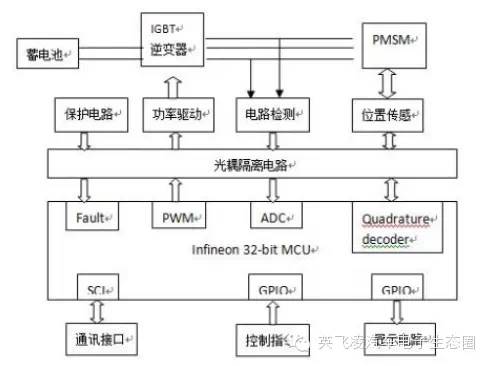

在機(jī)器人、機(jī)械臂和數(shù)控機(jī)床等工業(yè)控制系統(tǒng)中,永磁同步電機(jī)(PMSM)的驅(qū)動(dòng)控制一直是此類控制系統(tǒng)的核心。而隨著工業(yè)技術(shù)的發(fā)展以及PMSM應(yīng)用的越來越廣泛,PMSM的驅(qū)動(dòng)控制系統(tǒng)對(duì)性能和精度的需求也越來越高。為了滿足高性能、高精度等需求,有學(xué)者采用高性能的DSP作為軟硬件解決方案,也有學(xué)者使用ARM微控制器作為系統(tǒng)解決方案,例如使用STM32實(shí)現(xiàn)的控制系統(tǒng)[3]。由于PMSM控制算法愈加復(fù)雜化、控制算法對(duì)控制器性能的要求不斷提高,國(guó)外學(xué)者提出了使用FPGA作為PMSM的驅(qū)動(dòng)控制系統(tǒng)解決方案[4],且效果顯著。

本文使用的控制核心板即為搭載有Zynq7000系列芯片XC7Z020CLG484的ZedBoard開發(fā)板。使用這類產(chǎn)品可以在充分發(fā)揮FPGA并行計(jì)算優(yōu)勢(shì)的前提下,利用ARM進(jìn)行快捷的操作系統(tǒng)移植[7]以及人機(jī)交互等軟件開發(fā)。本文的開發(fā)方案是在ARM和FPGA上分別實(shí)現(xiàn)不同的控制算法模塊,該方案在結(jié)合ARM和FPGA各自優(yōu)勢(shì)的同時(shí),提高了系統(tǒng)的控制性能和可移植性。點(diǎn)擊查看更多精彩內(nèi)容.

1 控制系統(tǒng)介紹

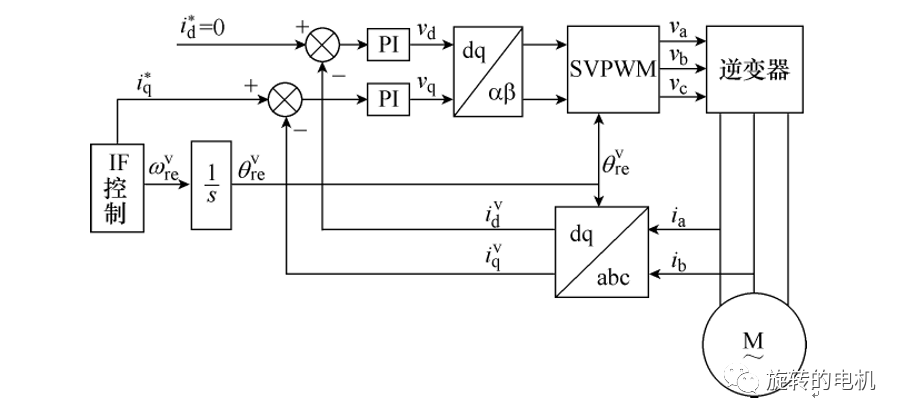

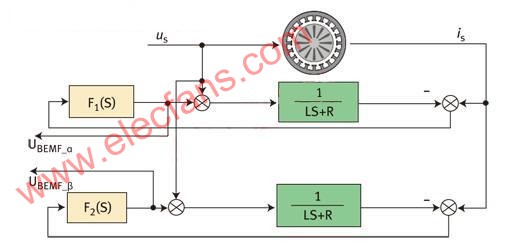

常見的PMSM驅(qū)動(dòng)控制系統(tǒng)可以分為電流環(huán)、速度環(huán)、位置環(huán)3個(gè)層次的控制模塊,以及機(jī)電傳感器信號(hào)處理接口、數(shù)據(jù)監(jiān)測(cè)、人機(jī)交互等。電流環(huán)控制方案較多采用的是矢量控制算法,該算法通過檢測(cè)PMSM的相電流值,以坐標(biāo)變換的方式將定子電流分解成勵(lì)磁電流和轉(zhuǎn)矩電流,以實(shí)現(xiàn)各自的閉環(huán)控制[8]。而速度環(huán)、位置環(huán)控制器常用的是PID控制器。

控制系統(tǒng)結(jié)構(gòu)如圖1所示。按照功能類型可以將系統(tǒng)組件劃分為機(jī)電接口組件、矢量控制算法組件和控制層組件下幾個(gè)部分。

圖1 控制系統(tǒng)結(jié)構(gòu)圖

1.1 機(jī)電接口組件

機(jī)電接口組件主要是實(shí)現(xiàn)機(jī)械、電路等模塊的信號(hào)接收、發(fā)送和信號(hào)處理等功能。該組件的信號(hào)輸入捕捉模塊為隨后的算法層提供帶有指定格式的數(shù)據(jù),信號(hào)輸出模塊為機(jī)電執(zhí)行電路提供標(biāo)準(zhǔn)的可控信號(hào)波形。具體來說,該組件由以下幾個(gè)模塊構(gòu)成:

① 編碼器正交解碼模塊。該模塊實(shí)現(xiàn)對(duì)編碼器信號(hào)的處理,通過捕捉編碼器的輸出波形,計(jì)算出電動(dòng)機(jī)轉(zhuǎn)速、轉(zhuǎn)子位置等數(shù)據(jù)。

② ADC接口模塊。該模塊實(shí)現(xiàn)的是A/D轉(zhuǎn)換器的傳輸協(xié)議,本系統(tǒng)是使用帶有SPI接口的A/D轉(zhuǎn)換器,故而該模塊實(shí)現(xiàn)SPI通信協(xié)議。

③ PWM發(fā)生器。該模塊完成脈寬可調(diào)制波形(PWM)的生成,該模塊產(chǎn)生用于驅(qū)動(dòng)本文所設(shè)計(jì)逆變器的6路PWM信號(hào)。

1.2 矢量控制算法組件

矢量控制算法組件完成PMSM的電流環(huán)相關(guān)算法。該組件包括以下幾個(gè)模塊:

① Sin&Cos模塊。該模塊完成轉(zhuǎn)子的電角度值到正弦、余弦值的計(jì)算。

② 空間坐標(biāo)轉(zhuǎn)換模塊。該模塊把該系統(tǒng)的控制目標(biāo)PMSM等效成一臺(tái)控制算法和更簡(jiǎn)單的直流電動(dòng)機(jī),主要包含了三相兩相坐標(biāo)變換和同步旋轉(zhuǎn)變換等模塊,實(shí)現(xiàn)了定子三相電流解耦成轉(zhuǎn)矩電流iq和勵(lì)磁電流id的計(jì)算過程。

③ SVPWM模塊。該模塊實(shí)現(xiàn)空間矢量PWM信號(hào)的產(chǎn)生等功能。

1.3 控制層組件

控制層組件實(shí)現(xiàn)PMSM的三環(huán)控制,主要包括以下幾個(gè)模塊:

① 電流環(huán)轉(zhuǎn)矩電流iq和勵(lì)磁電流id的控制器模塊;

② 速度環(huán)、位置環(huán)控制器,以及轉(zhuǎn)子速度、位置計(jì)算等模塊;

③ 輔助控制以及測(cè)試相關(guān)的模塊,主要實(shí)現(xiàn)人機(jī)交互、調(diào)試數(shù)據(jù)獲取等功能。

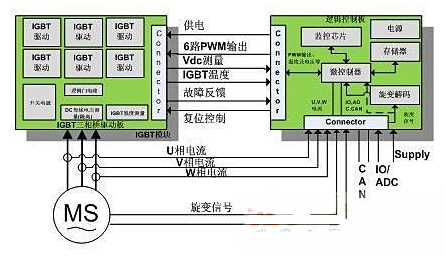

2 系統(tǒng)硬件平臺(tái)設(shè)計(jì)

該嵌入式驅(qū)動(dòng)控制系統(tǒng)的硬件平臺(tái)由四塊印制電路板(PCB)構(gòu)成,其組成結(jié)構(gòu)如圖2所示。PCB板由ZedBoard開發(fā)板、FMC接口板、信號(hào)處理板以及驅(qū)動(dòng)板組成。

圖2 系統(tǒng)電路板組成

3 系統(tǒng)軟件設(shè)計(jì)

根據(jù)驅(qū)動(dòng)控制系統(tǒng)原理框圖,可將系統(tǒng)的軟件算法模塊根據(jù)算法并行性、性能需求和可移植性需求劃分到ARM或者FPGA上實(shí)現(xiàn)。控制系統(tǒng)利用FPGA實(shí)現(xiàn)矢量控制電流環(huán)以提高算法并行性和計(jì)算頻率;使用ARM實(shí)現(xiàn)速度環(huán)、位置環(huán)和人機(jī)交互等算法,以保證軟件開發(fā)的便捷性和算法的可移植性。而系統(tǒng)中ARM和FPGA的通信使用Zynq片上高性能總線(AXI HP)以及中斷信號(hào)實(shí)現(xiàn)。系統(tǒng)軟件組成框圖略——編者注。

3.1 ARM與FPGA通信設(shè)計(jì)

ARM與FPGA的核間通信問題是Zynq應(yīng)用開發(fā)的重中之重,其核間通信總線AXI HP可采用存儲(chǔ)器直接訪問(DMA)的形式進(jìn)行數(shù)據(jù)傳輸,總線最高位寬為64位,理論通信帶寬最高可達(dá)1 200 MB/s。采用的通信方案為中斷信號(hào)和AXI HP總線協(xié)同工作的方式,中斷信號(hào)實(shí)現(xiàn)ARM和FPGA控制周期的協(xié)同,AXI HP總線為ARM和FPGA提供高帶寬的通信速率。系統(tǒng)采用AXI HP總線以DMA的形式直接讀寫ARM數(shù)據(jù)空間的方案,所以在控制算法周期內(nèi)ARM無需管理通信時(shí)序。

該系統(tǒng)的核間通信時(shí)序圖如圖3所示。

圖中數(shù)據(jù)傳輸發(fā)生在FPGA和ARM的算法軟件把數(shù)據(jù)處理完成之后,此處的數(shù)據(jù)處理包括如下兩個(gè)方面:

圖3 ARM和FPGA通信時(shí)序圖

① FPGA端數(shù)據(jù)處理包括對(duì)編碼器、A/D轉(zhuǎn)換器等傳感器信號(hào)的獲取和處理,以及上一周期的電流環(huán)控制算法運(yùn)算過程中的重要變量數(shù)據(jù)收集和處理等工作。

② ARM端數(shù)據(jù)處理包括速度環(huán)輸出的電流給定指令的保存、上一周期的電流環(huán)反饋數(shù)據(jù)處理,以及人機(jī)交互指令數(shù)據(jù)解析等操作。

圖3中描述的通信信號(hào)簇的數(shù)據(jù)傳輸主要是完成FPGA數(shù)據(jù)寫到ARM可訪問的內(nèi)存空間、FPGA讀取ARM指定內(nèi)存空間的數(shù)據(jù)兩個(gè)方面的操作。圖3中涉及的中斷信號(hào)是由FPGA上的算法模塊發(fā)起,主要功能是同步FPGA和ARM的運(yùn)行時(shí)序。經(jīng)過上述AXI HP總線的數(shù)據(jù)傳輸和中斷信號(hào)兩個(gè)操作,可實(shí)現(xiàn)ARM和FPGA的數(shù)據(jù)交互功能,其總線頻率為90 MHz,測(cè)試其數(shù)據(jù)傳輸帶寬為284 MB/s。

3.2 FPGA部分代碼設(shè)計(jì)

該系統(tǒng)使用控制器XC7Z020芯片上嵌入的FPGA(Xilinx公司的Artix7系列),其資源總量約為1.3 M邏輯門。在本系統(tǒng)中電流環(huán)控制頻率為16 kHz,其實(shí)現(xiàn)的算法框圖如圖4所示。

圖4 FPGA實(shí)現(xiàn)軟件系統(tǒng)框圖

在FPGA上實(shí)現(xiàn)的軟件包括算法和接口兩個(gè)部分,其中算法部分?jǐn)?shù)據(jù)格式為16位的Q15定點(diǎn)數(shù),該部分代碼通過Xilinx工具ISE14.7完成代碼的功能仿真和驗(yàn)證,各個(gè)模塊占用FPGA總資源量如表1所列。該算法代碼運(yùn)行時(shí)鐘頻率為90 MHz,算法計(jì)算耗時(shí)為5.7 μs,可見其運(yùn)算耗時(shí)充分滿足本系統(tǒng)使用的16 kHz電流環(huán)控制頻率的要求。

表1 FPGA算法資源占用量

3.3 ARM部分代碼設(shè)計(jì)

運(yùn)行于本系統(tǒng)雙核ARM CortexA9上的軟件程序主要包括控制組件和輔助組件兩大部分。控制組件運(yùn)行于中斷服務(wù)程序中,以滿足算法對(duì)控制周期的時(shí)序要求;輔助組件運(yùn)行于背景循環(huán)程序中,實(shí)現(xiàn)人機(jī)交互接口管理、系統(tǒng)監(jiān)測(cè)等功能。

系統(tǒng)軟件的中斷服務(wù)程序運(yùn)算流程如圖5所示,該中斷服務(wù)程序的中斷信號(hào)由FPGA的矢量控制算法模塊發(fā)出。

圖5 運(yùn)行于ARM的軟件流程

圖中的數(shù)據(jù)處理流程包括以下幾個(gè)部分:

① 人機(jī)交互數(shù)據(jù)處理。實(shí)現(xiàn)用戶命令解析,系統(tǒng)運(yùn)行指令給定等功能。該系統(tǒng)的主要運(yùn)行模式包括速度模式和位置模式兩種,運(yùn)行指令包括給定電機(jī)轉(zhuǎn)動(dòng)位置、轉(zhuǎn)動(dòng)速度等。

② 電流環(huán)反饋數(shù)據(jù)解析和處理。該環(huán)節(jié)實(shí)現(xiàn)對(duì)運(yùn)行于FPGA上的算法進(jìn)行監(jiān)控,并對(duì)電機(jī)運(yùn)行數(shù)據(jù)進(jìn)行封裝,以便人機(jī)交互組件進(jìn)行數(shù)據(jù)發(fā)送等操作。

③ 電流環(huán)指令給定數(shù)據(jù)的保存。該環(huán)節(jié)主要是處理上一周期的速度控制器輸出數(shù)據(jù),保證該數(shù)據(jù)能準(zhǔn)確傳輸?shù)紽PGA。

完成數(shù)據(jù)處理之后,軟件運(yùn)行到核心控制器環(huán)節(jié)。該環(huán)節(jié)采用的位置環(huán)控制器為比例控制器,速度環(huán)控制器為積分抗飽和的PI控制器。經(jīng)過參數(shù)整定,該軟件算法能夠滿足系統(tǒng)控制精度等要求。

4 實(shí)驗(yàn)分析

本系統(tǒng)使用Xilinx開發(fā)工具套件ISE14.7、Vivado 2014.2以及SDK實(shí)現(xiàn)代碼開發(fā)和工程管理工作。其中,ISE 14.7用來完成FPGA代碼開發(fā)、算法功能仿真驗(yàn)證等工作,Vivado 2014.2用來進(jìn)行工程管理和Zynq ARM端的啟動(dòng)文件配置等工作,SDK用來進(jìn)行ARM端應(yīng)用程序開發(fā)工作。

本系統(tǒng)的實(shí)驗(yàn)平臺(tái)包含了以下幾個(gè)部分:

① 帶有2500線編碼器的PMSM電機(jī),電機(jī)參數(shù)如表2所列。

② 電機(jī)驅(qū)動(dòng)板、信號(hào)處理板、FMC接口板,用于供給驅(qū)動(dòng)板直流母線電壓的線性電源等。

③ 搭載有XC7Z020CLG484芯片的ZedBoard開發(fā)板。

給定PMSM驅(qū)動(dòng)控制系統(tǒng)2 400 r/min的速度階躍值時(shí)電機(jī)的速度和電流響應(yīng)情況圖略——編者注。該系統(tǒng)速度響應(yīng)無超調(diào)、無靜差、電流響應(yīng)迅速,可見該P(yáng)MSM控制系統(tǒng)具有良好的控制性能和控制精度。

表2 實(shí)驗(yàn)平臺(tái)PMSM參數(shù)

結(jié)語

介紹了一個(gè)基于Zynq的PMSM驅(qū)動(dòng)控制系統(tǒng),并介紹了異構(gòu)多核控制系統(tǒng)的片上總線通信方案的設(shè)計(jì)。該系統(tǒng)充分結(jié)合了ARM和FPGA在嵌入式系統(tǒng)應(yīng)用開發(fā)中的優(yōu)勢(shì),在ARM上實(shí)現(xiàn)人機(jī)交互以及可移植性強(qiáng)的算法,在FPGA上實(shí)現(xiàn)并行度高、性能要求高的算法。

通過實(shí)驗(yàn)驗(yàn)證了使用Zynq實(shí)現(xiàn)PMSM控制系統(tǒng)的可行性以及便捷性,說明該方案不僅可以提高系統(tǒng)控制性能、提高控制精度和帶寬,而且能夠在完成高性能控制器的基礎(chǔ)上實(shí)現(xiàn)復(fù)雜算法的驗(yàn)證、人性化的人機(jī)交互等功能,系統(tǒng)的控制性能和可擴(kuò)展性都得到了大幅增強(qiáng)。

編者注:本文為期刊縮略版,全文見本刊網(wǎng)站www.mesnet.com.cn。

參考文獻(xiàn)

[1] 陳應(yīng)豪。 基于DSP的PMSM矢量控制在電梯控制中的應(yīng)用[J]。 微處理機(jī),2010(3): 105107.

[2] 李長(zhǎng)紅。 PMSM調(diào)速系統(tǒng)中最大轉(zhuǎn)矩電流比控制方法的研究[J]。 中國(guó)電機(jī)工程學(xué)報(bào),2005,25(21): 169174.

[3] 張巍。 基于ARM的PMSM控制系統(tǒng)設(shè)計(jì)[J]。 微計(jì)算機(jī)信息: 嵌入式與SOC,2010,26(112): 7071.

[4] Mohamed Wissem Naouar. FPGABased Predictive Current Controller for Synchronous Machine Speed Drive [J]。 IEEE TRANSACTIONS ON POWER ELECTRONICS,2008,23 (4): 21152126.

[5] 李虎修。 基于FPGA + ARM 的永磁同步電動(dòng)機(jī)高精度轉(zhuǎn)速檢測(cè)[J]。 組合機(jī)床與自動(dòng)化加工技術(shù),2012(11): 5356.

[6] Xilinx. Zynq7000 All Programmable SoC Technical Reference Manual [EB/OL]。 [201411]。 http://www.xilinx.com/support/documentation/user_guides/ug585Zynq7000TRM.pdf.

[7] 方華啟。 多核實(shí)時(shí)操作系統(tǒng)TOPPERS/FMP移植研究[J]。 單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2013(12): 47.

[8] 陳伯時(shí)。 電力拖動(dòng)自動(dòng)控制系統(tǒng)—運(yùn)動(dòng)控制系統(tǒng)[M]。 3版。 北京: 機(jī)械工業(yè)出版社,2003: 190214.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論