傳統(tǒng)的大型LED顯示屏系統(tǒng)以單片機(jī)MCU、ARM 或PLD為核心控制芯片,以FPGA為核心的LED顯示屏控制系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)起來(lái)比較復(fù)雜,并且需要以高性能的FPGA芯片作為基礎(chǔ),而以微處理器為核心的

2011-11-16 15:39:13 2483

2483

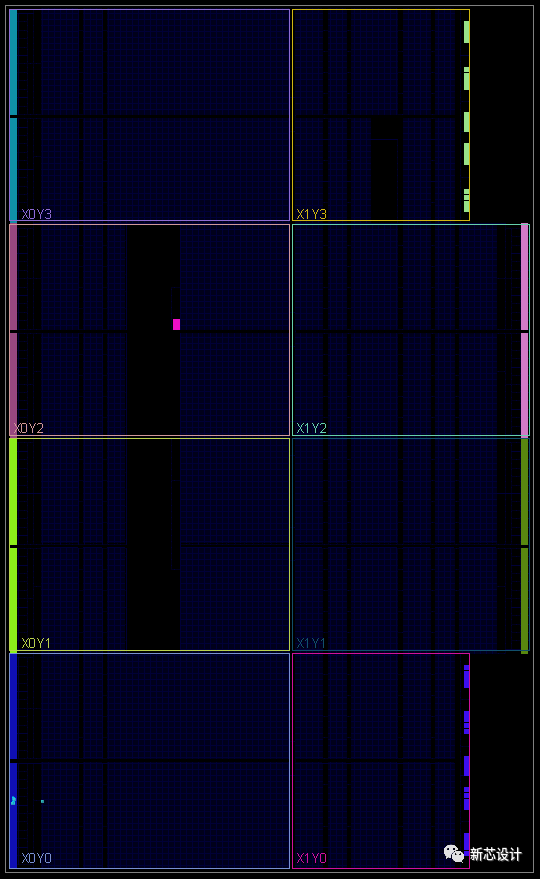

本文以FPGA作為核心處理器,提出了一種基于FPGA多路機(jī)載冗余圖像處理系統(tǒng)的設(shè)計(jì)方案。##整個(gè)系統(tǒng)顯示的分辨率為1600×1200@60 Hz,信號(hào)位為真彩色24b,則一幀圖像所需需要存儲(chǔ)的容量C≈47 Mb。##讀寫(xiě)操作交替進(jìn)行仿真圖如圖5所示。圖5中包含了兩個(gè)寫(xiě)入操作,一個(gè)讀取操作。

2014-01-07 10:28:32 2802

2802

通常來(lái)講,“一個(gè)好漢三個(gè)幫”,一個(gè)完整的嵌入式系統(tǒng)中由單獨(dú)一個(gè)FPGA使用的情況較少。##系統(tǒng)架構(gòu)確定,下一步就是FPGA與各組成器件之間互聯(lián)的問(wèn)題了。

2015-05-12 13:41:18 2836

2836 最近學(xué)習(xí)了ARM+FPGA的設(shè)計(jì)架構(gòu),ARM和FPGA結(jié)構(gòu)的通信大致可以分為兩種。

2015-05-25 10:35:04 21452

21452 加速。安排如下: 首先基于直方圖算法進(jìn)行FPGA架構(gòu)設(shè)計(jì),這里主要考慮了如何加速以及FPGA資源的利用兩個(gè)因素;最后基于system Verilog搭建一個(gè)驗(yàn)證系統(tǒng)。 FPGA設(shè)計(jì)架構(gòu) 不論是圖像灰度直方圖還是梯度直方圖,本質(zhì)上是對(duì)數(shù)據(jù)的分布進(jìn)行計(jì)數(shù)。從F

2020-12-10 16:37:20 2339

2339 成本。FPGA架構(gòu)的設(shè)計(jì)涉及許多不同的設(shè)計(jì)選擇,從高級(jí)架構(gòu)參數(shù)到晶體管級(jí)實(shí)現(xiàn)細(xì)節(jié),目標(biāo)是制造高度可編程的器件,同時(shí)最小化可重新配置的面積和性能成本。隨著應(yīng)用需求和工藝技術(shù)能力的不斷發(fā)展,FPGA架構(gòu)也必須適應(yīng)

2023-08-11 09:52:09 921

921

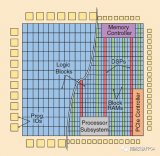

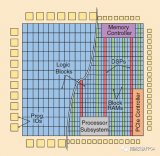

FPGA 內(nèi)部詳細(xì)架構(gòu)FPGA 芯片整體架構(gòu)1.可編程輸入輸出單元(IOB)(Input Output Block)2.可配置邏輯塊(CLB)(Configurable Logic Block)3.

2021-07-30 08:10:06

`FPGA代表現(xiàn)場(chǎng)可編程門(mén)陣列,它是一種半導(dǎo)體邏輯芯片,可編程成幾乎任何類(lèi)型的系統(tǒng)或數(shù)字電路,類(lèi)似于PLD。PLD僅限于數(shù)百個(gè)門(mén),但FPGA支持?jǐn)?shù)千個(gè)門(mén)。FPGA架構(gòu)的配置通常使用語(yǔ)言來(lái)指定,即

2018-12-14 17:39:44

的設(shè)計(jì)仍然可看做為高性能嵌入式系統(tǒng)的典型配置。 經(jīng)典的處理器+FPGA的配置中有多種的架構(gòu)形式,即多個(gè)處理器單元,可能是ARM,MIPS,或者DSP,FPGA也可能是多片的配置,具體架構(gòu)形式于具體處理的業(yè)務(wù)

2018-08-06 11:45:27

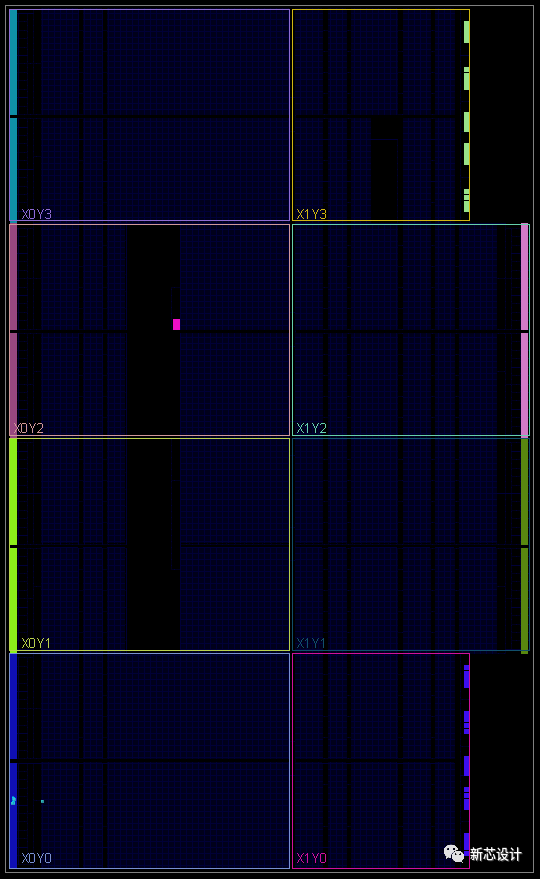

FPGA芯片整體架構(gòu)如下所示,整個(gè)芯片是以BANK進(jìn)...

2021-07-29 07:00:54

文中詳細(xì)介紹了該機(jī)載數(shù)字視頻記錄系統(tǒng)的軟?硬件設(shè)計(jì)思想及注意事項(xiàng)?

2021-06-04 06:11:00

機(jī)載雷達(dá)面臨哪些技術(shù)難題?機(jī)載雷達(dá)的信號(hào)是如何分布的?STAP的基本原理是什么?

2021-06-21 06:22:37

ARM的架構(gòu)相較于x86有哪些特點(diǎn)?ARM架構(gòu)的系統(tǒng)與X86架構(gòu)系統(tǒng)的特性有什么不同?

2021-06-16 09:05:32

XILINX FPGA 芯片整體架構(gòu)是如何構(gòu)成的?XILINX FPGA 芯片有哪些資源?

2021-10-29 06:26:23

做為高性能嵌入式系統(tǒng)的典型配置。經(jīng)典的處理器+FPGA的配置中有多種的架構(gòu)形式,即多個(gè)處理器單元,可能是ARM,MIPS,或者DSP,FPGA也可能是多片的配置,具體架構(gòu)形式于具體處理的業(yè)務(wù)相關(guān)和目標(biāo)設(shè)備

2017-06-07 13:12:54

的讀心術(shù)。soc fpga架構(gòu)下的的ARM處理器通過(guò)AIX總線訪問(wèn) FPGA域中的外設(shè)或者內(nèi)存空間,這些總線行為是可以通過(guò)硬邏輯狀態(tài)機(jī)來(lái)監(jiān)控的,針對(duì)一些需要高速處理的外設(shè),硬邏輯狀態(tài)機(jī)和處理器之間的交互

2015-01-06 17:24:03

項(xiàng)目名稱(chēng):基于FPGA的串***互命令架構(gòu)數(shù)碼管顯示項(xiàng)目試用計(jì)劃:申請(qǐng)理由本人在FPGA領(lǐng)域有一定的經(jīng)驗(yàn),開(kāi)發(fā)板很適合初學(xué)者學(xué)習(xí)使用,可以做一些簡(jiǎn)單的入門(mén)實(shí)驗(yàn)來(lái)快速入門(mén)Verilog語(yǔ)言,提高

2020-07-16 10:26:27

幾個(gè)問(wèn)題,一,性能不滿(mǎn)足需求。二,設(shè)計(jì)頻繁變更。三,系統(tǒng)不穩(wěn)定,調(diào)試問(wèn)題不收斂。磨刀不誤砍柴工,FPGA設(shè)計(jì)的需求分析是整個(gè)設(shè)計(jì)第一步。如何將系統(tǒng)的功能需求,轉(zhuǎn)換成FPGA的設(shè)計(jì)需求,是FPGA架構(gòu)

2019-08-02 08:30:00

`一種創(chuàng)新的機(jī)載娛樂(lè)系統(tǒng)`

2013-08-02 00:35:49

和FPGA可以構(gòu)成一個(gè)基本的嵌入式系統(tǒng),在后續(xù)的例程中它們大有用處;3個(gè)32PIN的標(biāo)準(zhǔn)插座可用于外接FPGA子板,進(jìn)行各種外設(shè)功能的擴(kuò)展。 圖2.8 FPGA核心板電路架構(gòu) `

2016-08-01 18:19:50

傳感器信息融合在同一個(gè)坐標(biāo)系中,因此需要研究機(jī)載環(huán)境中高清視頻處理技術(shù),研究在較大尺寸的顯示器上顯示處理高清視頻信號(hào)。 高清視頻處理模塊位于顯示分系統(tǒng)中,加速顯示高清視頻信號(hào),實(shí)現(xiàn)高清視頻的縮放和疊加

2018-11-07 10:42:22

足之處是開(kāi)關(guān)電源的輸出紋波較大,會(huì)產(chǎn)生有害的邊帶調(diào)制效應(yīng)。如果電源的開(kāi)關(guān)頻率可控,能與系統(tǒng)的PRF同步,這樣開(kāi)關(guān)電源紋波所產(chǎn)生的剩余調(diào)制邊帶就可通過(guò)采用MTI技術(shù)消除。因此設(shè)計(jì)了一種高功率開(kāi)關(guān)電源,集開(kāi)關(guān)頻率的外同步控制與高功率、高效率于一體,首次應(yīng)用于機(jī)載相控陣?yán)走_(dá)。[hide][/hide]

2009-12-10 16:39:51

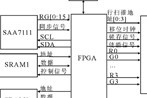

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過(guò)程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于

2019-06-28 08:10:26

隨著現(xiàn)代電子信息技術(shù)的發(fā)展,人機(jī)交互、圖形圖像數(shù)據(jù)的輸出顯示在系統(tǒng)設(shè)計(jì)中越來(lái)越重要,一方面要求各種參數(shù)的輸入,另一方面要求將數(shù)據(jù)結(jié)構(gòu)顯示出來(lái)。文中設(shè)計(jì)的基于DSP和FPGA的系統(tǒng)結(jié)構(gòu),實(shí)現(xiàn)了人機(jī)交互

2019-07-03 08:08:33

時(shí)間。針對(duì)上述研究現(xiàn)狀和分布式采集場(chǎng)景分析,本文介紹了一種基于FPGA和TOE架構(gòu),實(shí)現(xiàn)TCP/IP協(xié)議數(shù)據(jù)傳輸?shù)亩嗦凡杉c切換系統(tǒng)。該系統(tǒng)涉及并行數(shù)據(jù)采集、多路通道切換、TCP/IP協(xié)議通信等模塊

2021-07-12 08:30:00

基于FPGA的機(jī)載顯示系統(tǒng)該如何去設(shè)計(jì)?如何對(duì)機(jī)載顯示系統(tǒng)進(jìn)行優(yōu)化?

2021-06-01 06:04:12

目前伺服控制器的設(shè)計(jì)多以DSP或MCU為控制核心,但DSP的靈活性不如FPGA,且在某些環(huán)境比較惡劣的條件如高溫高壓下DSP的應(yīng)用效果會(huì)大打折扣,因此以FPGA為控制核心,對(duì)應(yīng)用于機(jī)載三軸伺服控制平臺(tái)的控制器進(jìn)行了設(shè)計(jì)與優(yōu)化。

2019-07-08 06:28:36

機(jī)載視頻圖形顯示系統(tǒng)主要實(shí)現(xiàn)2D圖形的繪制,構(gòu)成各種飛行參數(shù)畫(huà)面,同時(shí)疊加實(shí)時(shí)的外景視頻。由于FPGA具有強(qiáng)大邏輯資源、豐富IP核等優(yōu)點(diǎn),基于FPGA的嵌入式系統(tǒng)架構(gòu)是機(jī)載視頻圖形顯示系統(tǒng)理想的架構(gòu)

2019-06-24 06:07:53

基于FPGA的高清視頻采集與顯示系統(tǒng)

2012-08-17 23:57:42

圖像跟蹤系統(tǒng)。一方面,采用雙DSP體系結(jié)構(gòu)實(shí)現(xiàn)系統(tǒng)任務(wù)的并行劃分使本系統(tǒng)具備極高的運(yùn)算處理速度;另一方面,現(xiàn)場(chǎng)可編程邏輯器件FPGA的引入使系統(tǒng)的靈活性也得到極大的提高。而將兩者結(jié)合可使本系統(tǒng)充分體現(xiàn)新一代機(jī)載實(shí)時(shí)圖像跟蹤系統(tǒng)更快速、更精確、更靈活的特點(diǎn)。

2019-07-02 06:57:27

基于虛擬儀器技術(shù)的航空機(jī)載電子設(shè)備自動(dòng)測(cè)試系統(tǒng)虛擬儀器技術(shù)是利用軟件替代部分硬件功能的技術(shù),硬件模塊實(shí)現(xiàn)信號(hào)的調(diào)理,采集和輸出,軟件實(shí)現(xiàn)信號(hào)的處理,顯示和產(chǎn)生,利用軟件強(qiáng)大,快速和靈活的運(yùn)算處理能力

2009-12-15 15:07:00

利用可見(jiàn)光成像與紅外成像傳感器實(shí)現(xiàn)實(shí)時(shí)目標(biāo)成像跟蹤是精確制導(dǎo)武器及機(jī)載成像光電系統(tǒng)研究的核心技術(shù)。伴隨著實(shí)戰(zhàn)環(huán)境日益復(fù)雜以及偽裝、隱身等目標(biāo)特性控制技術(shù)的飛速發(fā)展,機(jī)載實(shí)時(shí)圖像跟蹤系統(tǒng)的應(yīng)用也日益廣泛與深入。當(dāng)跟蹤目標(biāo)并非一般地面慢速目標(biāo),而是其它快速運(yùn)動(dòng)目標(biāo)?

2019-09-03 07:06:05

': Exec format error兩個(gè)系統(tǒng)都是32位的,只是架構(gòu)不同,一個(gè)arm架構(gòu),一個(gè)Intel 80386架構(gòu),難道是不同架構(gòu)不能chroot嗎?,還是需要配置什么環(huán)境呢?懇請(qǐng)各位大俠賜教,感激不盡!

2019-07-30 05:45:23

為滿(mǎn)足機(jī)載系統(tǒng)發(fā)射機(jī)需求,一種高功率發(fā)射組件的設(shè)計(jì)與實(shí)現(xiàn)—樊錫元

2021-01-08 06:43:42

隨著現(xiàn)代航空電子技術(shù)飛速發(fā)展以及飛機(jī)性能的提高,使得機(jī)載圖形顯示系統(tǒng)所顯示的參數(shù)越來(lái)越多,同時(shí)也對(duì)畫(huà)面顯示質(zhì)量從人機(jī)工效學(xué)的角度提出了很高的要求。要保證圖形顯示的連續(xù)性,顯示系統(tǒng)必須以每秒50幀以上

2019-08-14 07:04:39

您可以顯著提高無(wú)線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-09-19 07:50:50

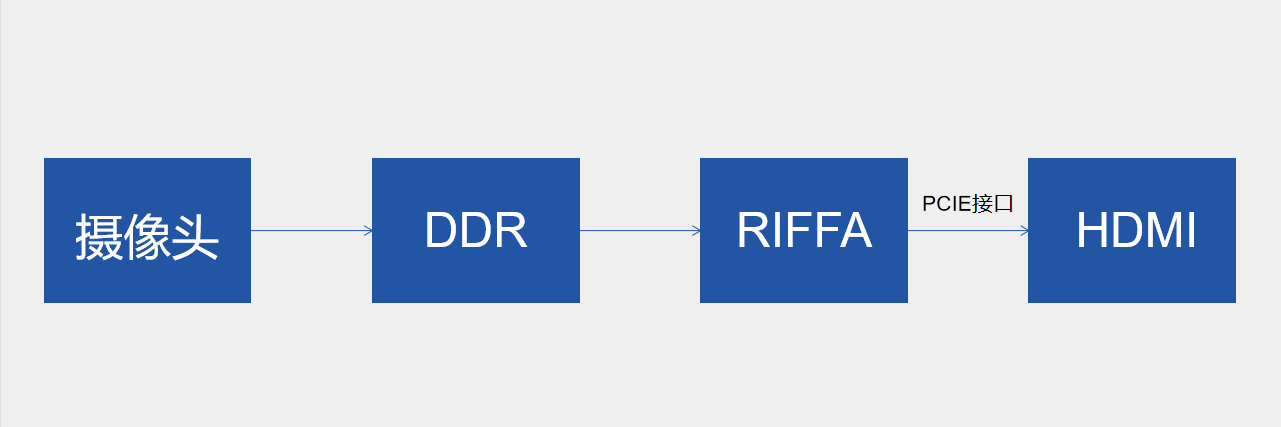

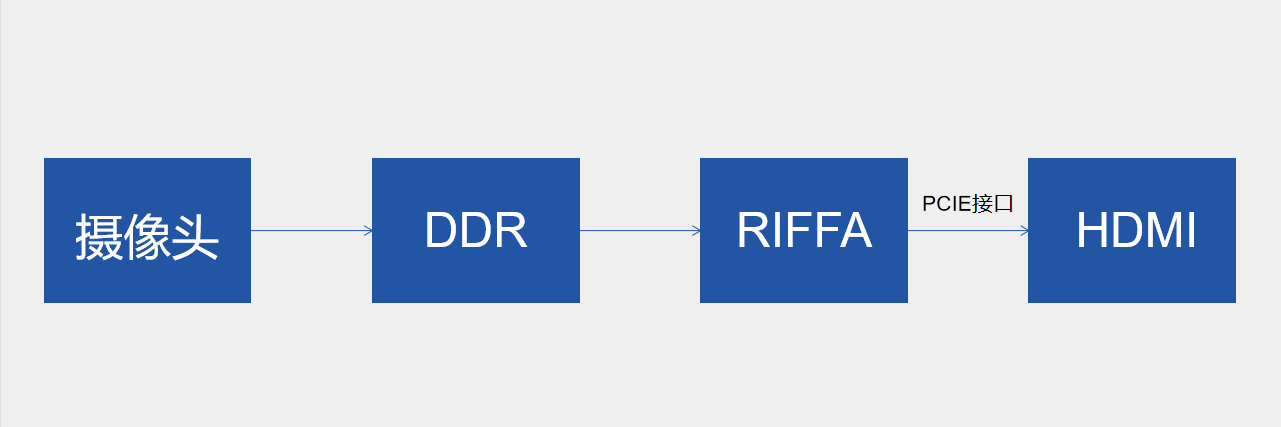

的信息并行存在,因此可以并行對(duì)其施以相同的操作,使得圖像處理的速度大大提高,這正好適合映射到FPGA架構(gòu)中用硬件算法得以實(shí)現(xiàn)。本篇闡述了基于FPGA設(shè)計(jì)一個(gè)能夠?qū)崟r(shí)采集、實(shí)時(shí)處理并實(shí)時(shí)顯示的數(shù)字圖像處理系統(tǒng)的設(shè)計(jì)思想和流程,分析了攝像頭接口的時(shí)序;闡述了圖像...

2021-07-28 06:06:26

陀螺儀測(cè)試系統(tǒng)硬件是怎樣設(shè)計(jì)的?如何去設(shè)計(jì)陀螺儀測(cè)試系統(tǒng)的軟件?怎樣去設(shè)計(jì)一款機(jī)載陀螺儀測(cè)試系統(tǒng)?并將其應(yīng)用于哪些領(lǐng)域?

2021-04-13 06:19:00

傳統(tǒng)的航空機(jī)載陀螺儀測(cè)試系統(tǒng)采用分立儀器搭建,具有成本高、自動(dòng)化程度低、擴(kuò)展性差的缺點(diǎn),因此,這里提出一種基于虛擬儀器技術(shù)的航空機(jī)載陀螺儀自動(dòng)測(cè)試系統(tǒng)的設(shè)計(jì)方案。

2021-05-11 06:15:04

ARM架構(gòu)是怎樣構(gòu)成的?STM32系統(tǒng)架構(gòu)地基本原理是什么?

2021-10-20 06:10:22

主要討論如何利用FPGA 實(shí)現(xiàn)數(shù)字圖像在VGA 顯示器和電視上進(jìn)行顯示, 并介紹所使用的Atmel AT40K 系列FPGA 及其特點(diǎn)。

2009-04-16 14:16:44 25

25 主要討論如何利用FPGA 實(shí)現(xiàn)數(shù)字圖像在VGA 顯示器和電視上進(jìn)行顯示, 并介紹所使用的Atmel AT40K 系列FPGA 及其特點(diǎn)。

2009-05-14 14:44:04 17

17 基于ARM+FPGA架構(gòu),高速采集和高清顯示二合一CPU集成i.MX 8M Mini+ARTIX7處理器,二合一成本優(yōu)勢(shì)明顯;高性能的ARM MPU+多媒體能力,良好

2022-11-04 16:12:46

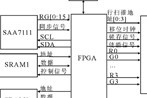

本文設(shè)計(jì)并實(shí)現(xiàn)了機(jī)載SAR 監(jiān)控系統(tǒng),在系統(tǒng)設(shè)計(jì)中采用89C52 作為處理器,并結(jié)合FPGA 對(duì)幾個(gè)關(guān)鍵技術(shù)進(jìn)行了分析。介紹了系統(tǒng)結(jié)構(gòu),總體方案

2009-09-15 10:28:01 15

15 本文介紹了一種機(jī)載塔康測(cè)試系統(tǒng),并闡述了該系統(tǒng)的結(jié)構(gòu)及硬件、軟件設(shè)計(jì)。

2010-03-02 14:40:02 25

25 為了在各種環(huán)境下對(duì)某飛機(jī)的機(jī)載電子設(shè)備進(jìn)行有效地功能測(cè)試和故障定位,提出了一種基于PXI構(gòu)架的測(cè)試系統(tǒng),可以在各種環(huán)境下實(shí)現(xiàn)整機(jī)聯(lián)合測(cè)試,也可實(shí)現(xiàn)該機(jī)載計(jì)算機(jī)系統(tǒng)

2010-07-15 17:53:59 6

6

分析機(jī)載數(shù)據(jù)中繼系統(tǒng)的組成和機(jī)載天線控制特性,使用真實(shí)數(shù)據(jù)接收機(jī)解調(diào)并輸出數(shù)據(jù),使用軟件模擬機(jī)載天線運(yùn)動(dòng)和波束特性,完成半實(shí)物仿真方式的機(jī)載數(shù)據(jù)中

2010-11-26 16:17:11 0

0 麥道90機(jī)載變速恒頻發(fā)電系統(tǒng)的諧波分析

摘要:介紹麥道(MD)90飛機(jī)機(jī)載變速恒頻交流發(fā)電系統(tǒng)的組成和工作原理。重點(diǎn)對(duì)其輸出階

梯波的諧波作理論分

2009-07-11 08:39:59 1417

1417

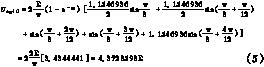

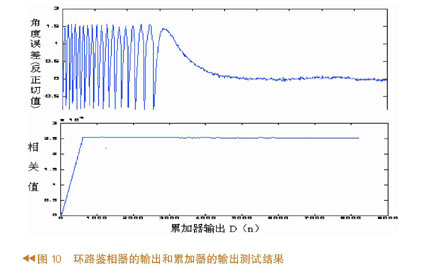

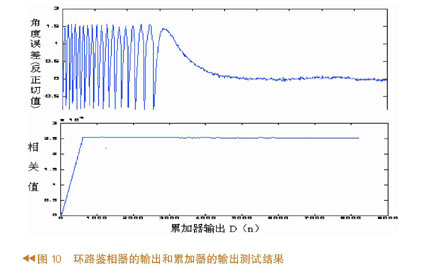

直擴(kuò)導(dǎo)航系統(tǒng)中數(shù)字科思塔斯環(huán)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

引言

擴(kuò)頻接收機(jī)載波的同步包括捕獲和跟蹤兩個(gè)過(guò)程,載波捕獲即多普勒頻移的粗略估計(jì)通常包含在偽

2010-03-01 09:11:45 1060

1060

現(xiàn)行的機(jī)載雷達(dá)一般都采用電視體制的PAL制或VGA制式,這兩種信號(hào)均為模擬信號(hào),模擬信號(hào)在用于現(xiàn)代的液晶顯示時(shí),要經(jīng)歷先D/A后A/D的變換,經(jīng)過(guò)變換后信號(hào)必然有所損失,為了避免

2011-03-21 15:11:24 107

107 性能分析和早期的架構(gòu)探索研究,可以確保你選擇合適的FPGA平臺(tái),在結(jié)構(gòu)和軟件方面實(shí)現(xiàn)應(yīng)用的最佳劃分分配。這種早期探索稱(chēng)為快速可視原型。借助在圖形化環(huán)境中使用預(yù)組建、參數(shù)

2011-03-24 10:11:07 158

158 本文介紹了一種基于FPGA的視頻采集與顯示系統(tǒng)的設(shè)計(jì)。系統(tǒng)以FPGA為核心,配合高分辨率CCD圖像傳感器、ADC模數(shù)轉(zhuǎn)換、視頻編碼器等,實(shí)現(xiàn)了高清視頻實(shí)時(shí)采集與顯示。詳細(xì)闡述了色彩插

2011-08-19 10:53:51 4581

4581 本設(shè)計(jì)開(kāi)發(fā)出了一套基于雙FPGA+ARM架構(gòu)的高速計(jì)算機(jī)屏幕圖像壓縮系統(tǒng)。系統(tǒng)通過(guò)對(duì)圖像壓縮系統(tǒng)任務(wù)的劃分,利用FPGA的并行計(jì)算能力和靈活的編程方式,完成圖像壓縮算法。

2011-08-22 11:44:31 2039

2039

ARINC429總線接口板的研制,實(shí)現(xiàn)多通道 ARINC429總線 數(shù)據(jù)的接收和發(fā)送,成為目前對(duì)飛機(jī)機(jī)載總線接口研究的重點(diǎn)。 1 ARINC429總線簡(jiǎn)介 在現(xiàn)代民用飛機(jī)上,系統(tǒng)與系統(tǒng)之間、系統(tǒng)與部件之

2011-10-05 16:07:15 1955

1955

針對(duì)圖像處理要求運(yùn)行復(fù)雜靈活的圖像處理算法和大數(shù)據(jù)量的數(shù)據(jù)傳輸處理的要求,提出了一種基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng),簡(jiǎn)要介紹了系統(tǒng)的工作原理,詳細(xì)介紹了系統(tǒng)硬

2011-12-05 14:12:28 62

62 文中采用一片TS201實(shí)現(xiàn)某機(jī)載雷達(dá)所需要的測(cè)角系統(tǒng),該設(shè)計(jì)滿(mǎn)足實(shí)時(shí)性要求,具有精度高、自動(dòng)測(cè)角、實(shí)現(xiàn)簡(jiǎn)單、穩(wěn)健性好等優(yōu)點(diǎn)。

2012-02-10 16:32:07 24

24 首先,針對(duì)機(jī)載光電跟蹤控制系統(tǒng)的特點(diǎn),建立了被控對(duì)象的模型。接著,對(duì)機(jī)載光電跟蹤系統(tǒng)模糊PID控制器的設(shè)計(jì)進(jìn)行了詳細(xì)介紹。最后,利用經(jīng)典PID控制、模糊控制、模糊PID控制3種

2012-02-16 17:05:05 42

42 文中首先研究了F16雷達(dá)對(duì)抗系統(tǒng)仿真的流程,重點(diǎn)對(duì)雷達(dá)系統(tǒng)的基本模型以及干擾模型進(jìn)行了論述,并對(duì)F16機(jī)載雷達(dá)對(duì)抗系統(tǒng)進(jìn)行了仿真。測(cè)試結(jié)果表明,系統(tǒng)可以較好地為機(jī)載雷達(dá)對(duì)抗系

2012-04-20 10:51:26 44

44 本文以Virtex-II系列PlatformFPGA為例,說(shuō)明采用FPGA方案進(jìn)行數(shù)字顯示系統(tǒng)設(shè)計(jì)所具有的靈活、快速和低成本等特性。

2012-06-01 15:22:59 619

619 機(jī)載圖像無(wú)損近無(wú)損壓縮方案及其FPGA實(shí)現(xiàn)

2016-08-29 15:02:03 5

5 基于ARM7與FPGA架構(gòu)的面陣CCD圖像采集系統(tǒng)的設(shè)計(jì)

2016-08-29 15:31:41 19

19 DDR2SDRAM控制器在機(jī)載顯控系統(tǒng)中的應(yīng)用_孫少偉

2017-03-19 11:26:54 1

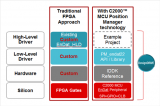

1 在這個(gè)系列的第一篇博文中,我們了解到FPGA是如何被引入到驅(qū)動(dòng)架構(gòu)中的。現(xiàn)在,我們來(lái)看一看在一個(gè)工業(yè)驅(qū)動(dòng)/伺服機(jī)架構(gòu)中使用FPGA時(shí)遇到的一些挑戰(zhàn),以及以COTS MCU形式運(yùn)轉(zhuǎn)的控制片上系統(tǒng) (SoC) 的全新功能如何用FPGA來(lái)改變針對(duì)工業(yè)驅(qū)動(dòng)的成本有效模型。

2017-04-26 12:17:39 2013

2013

本文介紹了基于FPGA的機(jī)載視頻圖形顯示系統(tǒng)架構(gòu)的設(shè)計(jì)與優(yōu)化,并介紹了三種系統(tǒng)架構(gòu),對(duì)系統(tǒng)各組成部分進(jìn)行了詳細(xì)的分析與概述。

2017-10-15 10:19:56 2

2 1 引言 利用可見(jiàn)光成像與紅外成像傳感器實(shí)現(xiàn)實(shí)時(shí)目標(biāo)成像跟蹤是精確制導(dǎo)武器及機(jī)載成像光電系統(tǒng)研究的核心技術(shù)。伴隨著實(shí)戰(zhàn)環(huán)境日益復(fù)雜以及偽裝、隱身等目標(biāo)特性控制技術(shù)的飛速發(fā)展,機(jī)載實(shí)時(shí)圖像跟蹤系統(tǒng)

2017-10-26 16:41:30 0

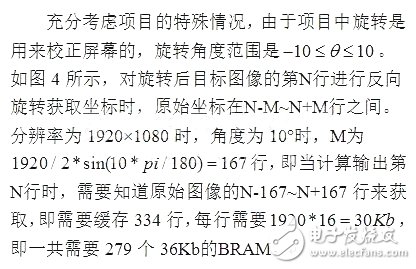

0 本文對(duì)基于FPGA的機(jī)載視頻圖形顯示系統(tǒng)架構(gòu)進(jìn)行設(shè)計(jì)和優(yōu)化。從實(shí)時(shí)性、BRAM資源占用和DDR3吞吐量三方面進(jìn)行分析,改進(jìn)幀速率提升算法來(lái)提高實(shí)時(shí)性;改進(jìn)視頻旋轉(zhuǎn)算法來(lái)降低BRAM資源占用;改變

2017-11-18 03:42:01 1882

1882 隨著航空電子技術(shù)的不斷發(fā)展,現(xiàn)代機(jī)載視頻圖形顯示系統(tǒng)對(duì)于實(shí)時(shí)性等性能的要求日益提高。常見(jiàn)的系統(tǒng)架構(gòu)主要分為三種: (1)基于 GSP+VRAM+ASIC 的架構(gòu),優(yōu)點(diǎn)是圖形 ASIC 能夠有效提高

2017-11-30 15:10:09 21

21 本文主要介紹了一種基于STM32+FPGA的全彩LED顯示屏系統(tǒng)的設(shè)計(jì),STM32作為主控芯片,通過(guò)以太網(wǎng)傳輸數(shù)據(jù),以FLASH作為存儲(chǔ)模塊,由FPGA完成對(duì)LED顯示屏的高速掃描刷新。系統(tǒng)工作

2017-12-28 13:59:47 12505

12505

操作系統(tǒng),滿(mǎn)足高性能、強(qiáng)實(shí)時(shí)的網(wǎng)絡(luò)通信,對(duì)傳統(tǒng)的軟硬件架構(gòu)都帶來(lái)了新的挑戰(zhàn)。在機(jī)載應(yīng)用工作模式、多任務(wù)綜合、高性能計(jì)算、強(qiáng)實(shí)時(shí)網(wǎng)絡(luò)等多種需求的牽引下,設(shè)計(jì)并實(shí)現(xiàn)了一種基于Rapidl0網(wǎng)絡(luò)的機(jī)載嵌入式通信軟件,滿(mǎn)足了新一代航電

2018-01-25 17:26:02 3

3 壽命預(yù)測(cè)和估計(jì)是機(jī)載液壓系統(tǒng)健康管理的核心難點(diǎn)。綜述了機(jī)載系統(tǒng)壽命預(yù)測(cè)與估計(jì)常用方法,針對(duì)長(zhǎng)壽命機(jī)載系統(tǒng)不可能在出廠前給出準(zhǔn)確壽命,提出動(dòng)態(tài)數(shù)據(jù)更新的粒子濾波壽命估計(jì)方法。建立機(jī)載液壓系統(tǒng)多場(chǎng)耦合

2018-03-10 09:54:57 0

0 無(wú)人機(jī)在偵察、測(cè)繪等領(lǐng)域?qū)D像分辨率的要求不斷提高,隨之帶來(lái)了數(shù)據(jù)量的顯著增大,其次,視頻圖像系統(tǒng)與傳統(tǒng)遙控遙測(cè)系統(tǒng)的融合也是設(shè)計(jì)中需要考慮的。針對(duì)以上問(wèn)題,設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA

2018-09-07 15:39:27 18

18 介紹了一種基于FPGA的LED視頻顯示系統(tǒng)的設(shè)計(jì)方案,詳細(xì)闡述了系統(tǒng)各模塊的工作原理及調(diào)試情況,給出了單色LED視頻顯示系統(tǒng)的實(shí)驗(yàn)結(jié)果,并對(duì)由單色顯示屏擴(kuò)展成彩色顯示屏的技術(shù)進(jìn)行了探討。

2018-09-18 16:07:38 13

13 關(guān)鍵詞:機(jī)載 , 記錄系統(tǒng) , 視頻 , 數(shù)字 通過(guò)嵌入式計(jì)算機(jī)PC104對(duì)MPEG A/V編碼芯片SZ1510進(jìn)行配置和控制,可以縮短研制高性能航空機(jī)載環(huán)境下數(shù)字式彩色視頻記錄儀的開(kāi)發(fā)時(shí)間文中詳細(xì)

2018-12-06 16:31:01 242

242 傳統(tǒng)的大型LED顯示屏系統(tǒng)以單片機(jī)MCU、ARM 或PLD為核心控制芯片,以FPGA為核心的led顯示屏控制系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)起來(lái)比較復(fù)雜,并且需要以高性能的FPGA芯片作為基礎(chǔ),而以微處理器為核心

2018-12-25 11:21:17 13

13 機(jī)載制氧系統(tǒng)是針對(duì)飛機(jī)在氧氣系統(tǒng)出現(xiàn)不能滿(mǎn)足戰(zhàn)術(shù)要求的情況下所設(shè)計(jì)的,機(jī)載制氧系統(tǒng)是在保留飛機(jī)原有供氧部分的情況下,連續(xù)的制氧供機(jī)組人員使用的一套系統(tǒng),該系統(tǒng)的投入使用,減少了地面保障工作的難度,同時(shí)也增強(qiáng)了飛機(jī)的出動(dòng)強(qiáng)度和整機(jī)的戰(zhàn)術(shù)性能。

2020-09-22 15:40:54 1792

1792 通用FPGA架構(gòu)由三種類(lèi)型的模塊組成。它們是I / O塊或焊盤(pán),開(kāi)關(guān)矩陣/互連線和可配置邏輯塊(CLB)。基本FPGA架構(gòu)具有二維邏輯塊陣列,其具有用于用戶(hù)安排邏輯塊之間的互連的裝置。下面討論FPGA架構(gòu)模塊的功能:

2020-09-30 14:00:33 7542

7542 論述一種基于DSP和FPGA的機(jī)載圖形顯示系統(tǒng),并提出一種新穎的基于FPGA的動(dòng)態(tài)畫(huà)面的硬件填充方法在填充操作過(guò)程中,由DSP完成畫(huà)面中填充區(qū)域邊界的標(biāo)志運(yùn)算,FPGA完成填充畫(huà)面像素的刷新操作,使整個(gè)畫(huà)面刷新的速度大為提高.

2021-01-22 15:08:40 18

18 本文使用FPGA芯片,在 QuartusⅡI工作平臺(tái)下,利用 Verilog硬件描述語(yǔ)言,實(shí)現(xiàn)了VGA多幅圖片動(dòng)態(tài)彩色顯示系統(tǒng)的設(shè)計(jì)。設(shè)計(jì)中將VGA顯示的同步控制、圖像顯示地址、像素存儲(chǔ)單元

2021-06-01 10:08:09 27

27 基于FPGA和DSP的機(jī)載圖形顯示系統(tǒng)

2021-06-08 10:48:08 36

36 大家好,ARM+FPGA 作為一種主流的嵌入式系統(tǒng)的處理架構(gòu)。相對(duì)于單純的的ARM開(kāi)發(fā)或單純的FPGA開(kāi)發(fā),ARM加FPGA能夠帶來(lái)功耗、性能、成本等組合優(yōu)勢(shì)。

2023-01-13 17:56:02 2305

2305

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 機(jī)載視頻圖形顯示系統(tǒng)主要實(shí)現(xiàn)2D圖形的繪制,構(gòu)成各種飛行參數(shù)畫(huà)面,同時(shí)疊加實(shí)時(shí)的外景視頻。由于FPGA具有強(qiáng)大邏輯資源、豐富IP核等優(yōu)點(diǎn),基于FPGA的嵌入式系統(tǒng)架構(gòu)是機(jī)載

2023-06-08 03:35:01 1024

1024 各位工程師小伙伴們,大家好,ARM+FPGA作為一種主流的嵌入式系統(tǒng)的處理架構(gòu)。相對(duì)于單純的的ARM開(kāi)發(fā)或單純的FPGA開(kāi)發(fā),ARM加FPGA能夠帶來(lái)功耗、性能、成本等組合優(yōu)勢(shì)。米爾新推出

2023-01-13 15:24:23 525

525

?FPGA 芯片架構(gòu)是非常重要的,如果你不了解 FPGA 芯片內(nèi)部的詳細(xì)架構(gòu)。

2023-07-04 14:36:07 811

811

加速FPGA選擇和系統(tǒng)設(shè)計(jì)的架構(gòu)探索

2022-12-30 09:21:10 3

3 FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)的架構(gòu)主要由可配置邏輯模塊(CLB)、輸入/輸出模塊(IOB)以及可編程互連資源組成。

2024-03-14 17:05:29 94

94 FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)芯片架構(gòu)是一種高度靈活和可編程的集成電路架構(gòu),它以其獨(dú)特的結(jié)構(gòu)和功能,在現(xiàn)代電子系統(tǒng)中扮演著至關(guān)重要的角色。FPGA芯片架構(gòu)的核心在于其可編程性和高度的并行處理能力,這使得它能夠在各種應(yīng)用中實(shí)現(xiàn)高效、可靠的性能。

2024-03-15 14:56:29 107

107

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論