摘要:基于PCI 總線和FPGA 的特點,設計了具有高精度、高穩定性及高準確性的多通道信號采集傳輸系統。系統采用以FPGA 為主控單元,通過控制模擬選擇開關ADG706 及A/D 轉換器AD7667 實現對模擬信號的采集,并由FIFO 緩存經過PCI總線將所采集的數據上傳至上位機顯示分析。經實際應用,系統性能穩定,符合設計要求。

數據采集就是將被測對象( 外界、現場) 的各種參量( 物理量、化學量、生物量等) 通過各種傳感元件做適當轉換后,再經調理、采樣、量化、編碼、傳輸等步驟,最后送到控制器進行數據處理或存儲記錄的過程[1]。數據采集技術可以將許多抽象的模擬量數字化,進而給出其量值,或通過信號處理對該模擬量進行分析。基于FPGA 器件的高時鐘頻率、內部延時小、時序簡便精確控制、編程配置靈活等優點,故本系統以FPGA 為核心來控制通道切換模數、轉換、數據編幀及傳輸。此外基于PCI 總線穩定性高,數據傳輸速度快,擴張性強的優點,本設計中采用PCI 總線實現上位機與FPGA 的無縫連接,完成上位機與FPGA 控制模塊之間的數據傳輸。

1 系統設計

1. 1 系統組成

本系統對29 路高頻壓力信號進行采集( 其中速變信號4 路采樣率40 K,緩變信號25 路采樣率6. 6 K) 。設計采用模塊化設計。各個模塊之間既整體協調又相互獨立構成整個系統。系統主要由信號采集模塊、FPGA 控制模塊、PCI 總線接口模塊、電源模塊組成。模塊化設計既有利于電路調試、編程和擴展,又能很方便的快速定位問題和解決問題。本系統中考慮到控制程序占用較多的邏輯資源,FPGA 控制模塊采用Xilinx 公司spartan—3 系列芯片XC3S400 作為主控芯片與外圍器件進行連接。系統總體框圖如圖1 所示。

1. 2 系統原理

本系統上電隨即實現采集與傳輸功能,無需等待命令字。模擬信號通過運放OPA4340 進行放大,再進入一階濾波電路和電壓跟隨器進行信號調理,之后在FPGA 的時序控制下通過模擬選擇開關ADG706的選通進入AD7667 進行模數轉化,轉換后的數據緩存到FIFO 中,最后經PCI 總線接口電路上傳至上位機進行顯示和分析。整個系統的供電由電源模塊提供,電源模塊自帶EMI 模塊進行濾波保護,向FPGA控制模塊提供所需的5 V、3. 3 V 和1. 2 V 電壓,向信號采集模塊提供所需的5 V、3. 3 V 電壓。

2 硬件電路設計

2. 1 信號調理及跟隨電路

高頻壓力信號進入系統后,首先要經過信號調理電路完成對信號的放大、濾波、跟隨保持,調理電路如圖2 所示,經過信號放大電路,將信號幅值調節到0—5 V 的范圍內,之后通過一階濾波電路,其中濾波電路截止頻率為,,這樣把輸入信號的頻率范圍調理成系統采集信號的頻率范圍內,最后進入模擬開關ADG706。圖2 中的D1 起到了反向保護的作用。

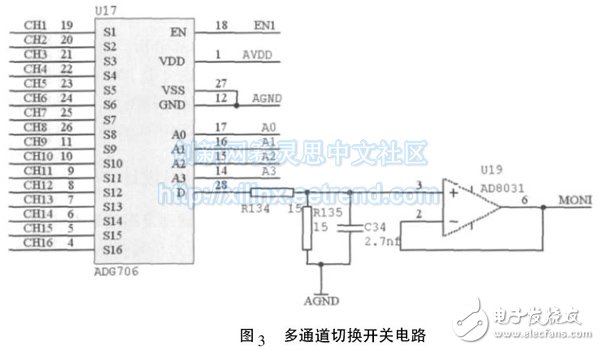

2. 2 多通道切換開關電路

16 路選擇模擬開關ADG706 把各路模擬信號切換依次送入模數轉換器AD7667 進行A/D 轉換,設計中可使用2 個ADG706 實現29 路模擬信號的切換。在設計過程中FPGA 控制模塊對于模擬開關

ADG706 的使能控制和通道切換控制是設計中應該注意的問題。此外信號在通過ADG706 后將進入電壓跟隨器,這里的跟隨器選用的高速運放AD8031,根據芯片資料知其最大可帶容性負載為15PF,遠遠高于AD8031 的驅動能力。因此有可能會造成振蕩問題。設計中增加一階有源濾波電路可以濾除高頻振蕩。多通道切換開關電路如圖3 所示。

2. 3 A \D 轉換電路

本系統中模數轉換器AD7667,具有16 bit /1 M的采樣能力。輸入信號經其轉換后變成16 位數字信號,在FPGA 控制下依次取其高8 位與低8 位,根據設計的幀結構的順序依次寫入FIFO 緩存器。設計中模擬信號在進入AD7667 之前經過調理后穩壓在0 ~ 5 V 范圍內。由于AD7667 內部具有2. 5 V 的基準電壓源,所以進入AD7667 前信號通過電阻網絡進行分壓,經過分壓處理后的電壓范圍為:

( 0 ~5 V) ×10 K/( 12 K +10 K) = ( 0 ~2. 25 V) 。

結果在AD7667 的電壓輸入范圍之內。此外C49 為去耦電容,作用是用來降低電源、噪聲等產生的干擾。A\ \D 轉換電路如圖4 所示。

2. 4 FIFO 緩存電路

本系統采用外部FIFO IDT7206,這是由于外部FIFO 引腳功能較多,尤其是半滿信號以及空信號都易于判斷,此外也不會占用FPGA 的內部資源。本設計中IDT7206 采取半滿即讀的工作方式,這樣不會發生FIFO 緩存數據溢出現象,并且可以將緩存的數據高速讀出,達到高速緩存的目的。FIFO 緩存電路如圖5 所示。

2. 5 PCI 接口模塊設計

PCI 總線接口模塊采用PLX 公司的PCI 總線通用接口芯片PCI9054,PCI9054 符合PCI V2. 1 和V2. 2 規范,具有兩個獨立的可編程DMA 控制器,數據寬度32 位,理論數據傳輸速率最高可達132 MBps[2]。為了滿足上位機與PCI 總線模塊之間的高速傳輸,PCI9054 采用DMA 突發傳輸模式來實現。

FPGA 控制模塊檢測到FIFO 的“半滿”信號為低電平時,將FIFO 中的數據讀取出來,組成規定的數據包,控制PCI9054 向上位機傳輸數據。

3 系統時序設計

3. 1 信號采樣幀結構的設計

在設計中采樣幀結構即信號采樣順序( 通道切換順序) 是最需要優先考慮的部分。在保證各路信號采樣率的情況下,在一個幀結構中平均同一信號的各采樣點時間間隔是設計的關鍵之處。在本系統中需采樣的速/緩變模擬信號參數如下:

S: 為速變信號,4 路( S1 ~ S4 ) ,采樣率: 40Ksps,8 bit;

H: 為緩變信號, 25 路( H1 ~ H25) ,采樣率: 6. 6Ksps,8 bit;

速變信號采樣率為緩變信號采樣率的6 倍,因此不需要提升系統總體采樣率。首先確定幀結構的行數: 將采樣率高的S 放置在幀結構的最起始位置,因其采樣率為6. 6 Ksps 的6 倍,所以一幀中S信號采樣點應為H 信號的6 倍,由此確定幀結構中一列為6 個采樣點,幀結構行數為6,且幀結構的前4 列為S 的采樣點,所以幀結構列數應大于4。

再確定幀結構的列數: 由于一列為6 個采樣點,這樣H 信號占用的采樣點數為25,需要5 列才能放下,同時空出5 個空位正好用來放置幀計數與幀標記。于是幀結構的列數為: 4 + 5 = 9。

于是可以確定幀結構是一個6 × 9 的矩陣,總采樣點54 個。其中幀計數與幀標記占用5 個采樣點,我們得到一種采樣幀結構如表1 所示。

3. 2 FPGA 的時序設計

本系統中模擬開關的選通,A \ \D 的控制,FIFO的讀寫均是由FPGA 進行控制,信號的總采樣率為

6. 6 K × 54 = 360 Ksps。FPGA 的時鐘頻率為54MHz,因此FPGA 內部邏輯在每一次采樣點上均有150 個狀態機可供使用,這對于模擬開關通道切換、A\ \D 模數轉換和FIFO 緩存已經完全足夠。此外模擬開關切換與啟動A \ \D 轉換被盡量分開,這樣安排主要是為了讓模擬信號在通道切換后,A \ \ D采樣前有足夠的時間穩定下來,以提高采樣精度[3]。FPGA 控制時序圖如下圖6 所示。

圖6 中: COVST 為AD 采樣控制信號,低電平有效; ADDR 為輸出的模擬開關切換地址; WRCLK 為FIFO 寫信號,上升沿有效; DATA 為將寫入FIFO 中的數據; BYTE 為字節輸出控制信號,低電平時取數據的低8 位,高電平時取數據的高8 位。

4 測試結果分析

在實際應用中,通過PCI 總線將采集到的數據上傳至上位機,其中上傳的一部分數據如圖7 所示。由圖7 可知上傳的數據幀格式完整,幀標志對齊,幀計數正確,沒有丟數現象。數據通過上位機處理后繪制出的曲線如圖8 所示。其中信號輸入為正弦波。由圖8 可知系統采樣功能正常,波形完整。綜上所述,本系統功能完整,性能滿足設計要求。

5 總結

本設計針對采集傳輸技術要求及當前技術實現手段,完成了多通道信號采集傳輸系統設計,將FPGA 和PCI 總線技術進行了有機的結合,充分利用了各自的優點,使采集系統具備實時采集、即時顯示、即時反饋、自動處理、自動傳輸的功能,為現場采集數據的真實性、有效性、實時性、可用性提供了可靠保證。

電子發燒友App

電子發燒友App

評論