高速率跳頻、高帶寬技術(shù)是提高跳頻發(fā)射機性能的關(guān)鍵,本文結(jié)合軟件無線電思想和架構(gòu),提出一種基于FPGA+DSP的跳頻電臺傳輸系統(tǒng)的設(shè)計方案,該系統(tǒng)兼容多種調(diào)制方式和跳頻速率及數(shù)碼率。系統(tǒng)采用上下變頻器作為系統(tǒng)基帶信號與中頻信號之間的頻率轉(zhuǎn)換器,還給出了系統(tǒng)電路原理圖和程序流程圖。

引言

跳頻技術(shù)是一種具有高抗干擾性、高抗截獲能力的擴頻技術(shù)[1]。接收系統(tǒng)是跳頻通信系統(tǒng)中非常重要的部分,自適應(yīng)跳頻技術(shù)、高速跳頻技術(shù)、信道編碼技術(shù)、高效調(diào)制解調(diào)技術(shù)成為近年來跳頻技術(shù)發(fā)展的新動態(tài),基于FPGA的跳頻通信接收系統(tǒng)[2]研究有很高的應(yīng)用價值。

跳頻電臺就是采用了頻率跳變來擴展頻譜,提高抗干擾能力,在軍事通信中得到了廣泛的應(yīng)用[3]。基于FPGA+DSP的跳頻電臺傳輸系統(tǒng)的設(shè)計方案[4]具有很好的可移植性。無線通信調(diào)制解調(diào)紛繁復(fù)雜,數(shù)碼率及誤碼率要求也不盡相同,該傳輸系統(tǒng)還需要能夠自適應(yīng)地檢測跳頻電臺的時鐘信息及同步碼,并進行相應(yīng)的處理,以滿足業(yè)務(wù)速率的接收解調(diào)。

本文系統(tǒng)中采用Xilinx公司的VIRTEX5 XC5VSX50T668 FPGA,該芯片具有先進的高性能邏輯架構(gòu),包含多種硬IP系統(tǒng)級模塊,并且還支持以太網(wǎng)與PCI Exprees端點模塊。其中RocketIO GTP收發(fā)器的設(shè)計運行速度為100 Mb/s~3.75 Gb/s,RocketIO GTX收發(fā)器的設(shè)計運行速度為150 Mb/s~6.5 Gb/s。

1 系統(tǒng)總體架構(gòu)

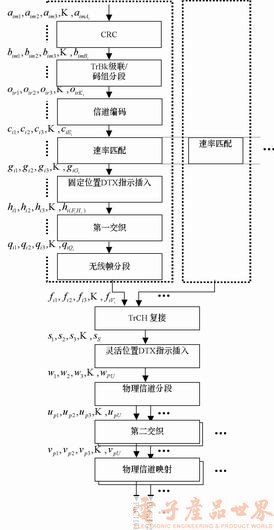

該系統(tǒng)采取半雙工形式進行工作,通過 PTT進行收/發(fā)切換。高速跳頻通信系統(tǒng)可具體化為發(fā)送狀態(tài)模型和接收狀態(tài)模型。本系統(tǒng)的硬件設(shè)備分為兩個實體,一個負責(zé)發(fā)送數(shù)據(jù),一個負責(zé)接收數(shù)據(jù),主要的軟件工作在基帶板和中頻板卡上。系統(tǒng)總體框架圖如圖1所示。

圖1 系統(tǒng)總體框架圖

基帶板芯片主要包括FPGA和DSP,處理器間使用RapidIO接口交換數(shù)據(jù),中頻板主要由FPGA和AD/DA轉(zhuǎn)換芯片組成,基帶板和中頻板通過高速SERDES傳輸信號數(shù)據(jù),基帶信號經(jīng)過信道編碼、交織、軟擴頻,然后添加同步頭,組成特定的幀格式后,寫入FPGA 的發(fā)送消息存儲區(qū),其結(jié)構(gòu)圖如圖2所示。

圖2 基帶板與中頻板框圖

從圖2可以看出,在發(fā)送端,數(shù)據(jù)終端或語音終端將數(shù)字信息送入基帶信號處理器(高速通用FPGA+DSP),然后DSP 對這些數(shù)字信息進行基帶處理,得到數(shù)字化的基帶信號并送入FPGA 進行數(shù)字中頻處理(頻譜上搬移過程),用數(shù)字化的方法將信號搬移中頻上,數(shù)字化的中頻信號再經(jīng)過寬帶D/A轉(zhuǎn)換器轉(zhuǎn)化為模擬信號,最后經(jīng)由射頻電路將載有信息的電磁波送入自由空間。

圖3 跳頻發(fā)射機結(jié)構(gòu)框圖

圖4 跳頻接收機結(jié)構(gòu)框圖

當接收信號到達接收端后,經(jīng)過前端電路的模擬中頻信號將通過寬帶A/D 轉(zhuǎn)換器轉(zhuǎn)化為數(shù)字信號,并送入FPGA 經(jīng)行中頻處理(頻譜下搬移過程),F(xiàn)PGA在把解調(diào)以后的數(shù)字基帶信號送入DSP,DSP 在完成接收基帶處理以后,將把信息序列送入遠端的語音終端或數(shù)據(jù)終端,這樣就完成了一次完整的通信過程。

對于其中的處理器,本課題選用了TI公司的DSP 芯片TMS320C6487TCI和Xilinx公司的FPGA VIRTEX5 XC5VSX50T668作為高速跳頻系統(tǒng)實現(xiàn)的硬件架構(gòu)載體。其中Xilinx公司的Virtex5系列采用第二代 ASMBL(高級硅片組合模塊)列式架構(gòu),包含5種截然不同的平臺(子系列),比此前任何 FPGA系列提供的選擇范圍都大,它具有運算速度高、使用靈活、功耗低等優(yōu)點,可以快速地完成數(shù)字信號處理中的特殊運算。

2 系統(tǒng)設(shè)計

跳頻發(fā)射機系統(tǒng)包括基帶處理部分和中頻處理部分,基帶處理部分由FPGA和DSP完成,主要處理包括:產(chǎn)生發(fā)送消息,進行信道編碼[5]、交織,按幀格式進行打包,寫入FPGA內(nèi)部消息存儲器,生成跳頻圖案、跳頻數(shù)、跳時等參數(shù),寫入FPGA內(nèi)部頻率表存儲器、跳頻數(shù)寄存器和跳時寄存器。中頻處理部分由FPGA和AD/DA完成,主要處理包括:存儲器控制、基帶調(diào)制、脈沖成形、數(shù)字上變頻,發(fā)送數(shù)據(jù)控制和跳頻控制。為了提高數(shù)據(jù)的傳輸速率,處理器之間使用DSP芯片的RapidIO端口進行數(shù)據(jù)交換,基帶板和中頻板通過高速SERDES方式轉(zhuǎn)換數(shù)據(jù)進行傳輸。

接收機與發(fā)射機完全是對偶關(guān)系,主要完成的數(shù)據(jù)處理工作包括:正交數(shù)字下變頻、解調(diào)、解擴、跳頻同步等。使用FPGA+DSP的形式完成基帶處理部分和控制部分,主要數(shù)據(jù)處理任務(wù)包括對接收到數(shù)據(jù)的信道解碼和解交織,并完成與FPGA接口的數(shù)據(jù)轉(zhuǎn)換工作。基帶部分還需要完成寫入跳頻頻率表、跳頻圖案、擴頻碼表,讀出解擴后的數(shù)據(jù)等,F(xiàn)PGA內(nèi)部存儲器用于與DSP進行數(shù)據(jù)交換。

2.1 硬件設(shè)計

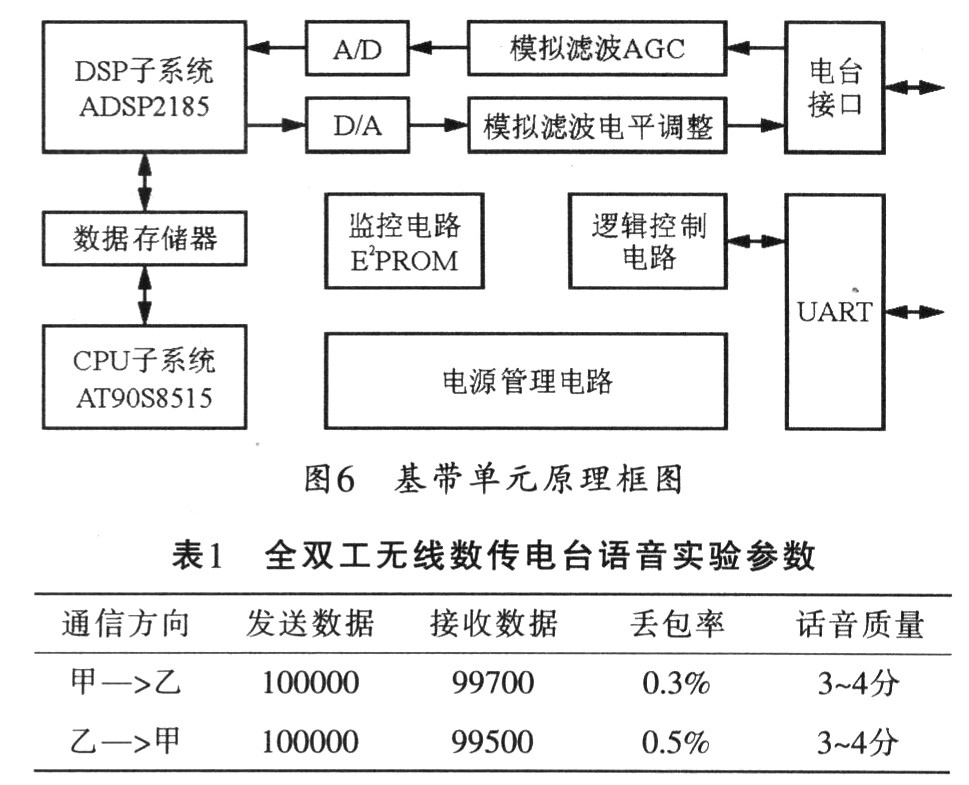

跳頻電臺傳輸系統(tǒng)的硬件實現(xiàn)[6]如圖3~4所示,主要包括兩大部分:發(fā)送板和接收板。芯片主要包括:VIRTEX5 XC5VSX50T668、TMS320C6487TCI,D/A芯片AD9788、A/D芯片ADS62C17、McBSP接口控制器、存儲器模塊。在該系統(tǒng)設(shè)計方案中假設(shè)信源產(chǎn)生的數(shù)據(jù)率為9.6 kbps。

發(fā)送狀態(tài)下系統(tǒng)的工作原理:終端通過與跳頻通信機之間的串口,對跳頻通信機的工作模式等參數(shù)進行設(shè)置,之后就可以進行信息的發(fā)送,信源以9.6 kbps的速率將信息通過RS232異步串口連續(xù)把數(shù)據(jù)送給基帶速率匹配單元,該單元將數(shù)據(jù)每32字節(jié)分為一組,以3.686 4 Mbps的傳輸速率通過SPI同步串口送給RS編碼單元進行RS編碼,編碼采用RS(255,239)的縮短碼形式RS(48,32)實現(xiàn)差錯控制,累計接收三組RS編碼數(shù)據(jù)后送往交織單元,交織后的數(shù)據(jù)包為144字節(jié),然后將144字節(jié)編碼數(shù)據(jù)進行并/串變換為1 152位/包,并以3.125 Mbps的傳輸速率,然后在1 152位/包的數(shù)據(jù)前加8字節(jié)數(shù)據(jù)幀同步頭,隨后將完整的一幀152字節(jié)(共1 216位)以1.98 Mbps的傳輸速率,通過DSP的RapidIO端口傳送給FPGA處理器,F(xiàn)PGA處理器通過同步串口接收中斷與緩沖器接收到數(shù)據(jù),F(xiàn)PGA中頻速率匹配單元將接收的數(shù)據(jù)按照中頻調(diào)制器要求的串行時鐘主外部幀模式,以32 kbps的幀速率將調(diào)制數(shù)據(jù)送給調(diào)制器,進行中頻跳頻調(diào)制。

接收狀態(tài)下系統(tǒng)的工作原理:接收信號經(jīng)過中頻板FPGA中的解擴器和解調(diào)器完成數(shù)字解調(diào),將基帶32 kb數(shù)據(jù)以連續(xù)的同步串行數(shù)據(jù)的格式送給DSP。DSP對數(shù)據(jù)進行同步幀檢測并解幀,并以3.125 Mbps的傳輸速率并行將144字節(jié)/包的數(shù)據(jù)送往解交織器進行解交織,處理后的數(shù)據(jù)每48字節(jié)為一組,以3.125 Mbps的傳輸速率通過同步并口送給RS譯碼模塊,依次進行RS譯碼。RS譯碼得到的32字節(jié)/包信息,通過緩沖器以SPI數(shù)據(jù)模式送給基帶速率匹配單元,傳輸速率為1.562 5 Mbps。基帶速率匹配單元將去掉冗余碼的數(shù)據(jù),再以9.6 kbps的速率送往信宿,至此接收處理過程完成。

2.2 軟件設(shè)計

為了實現(xiàn)高速跳頻通信系統(tǒng),需要考慮的問題是跳頻碼的接收同步和跳頻幀結(jié)構(gòu)[8]的實現(xiàn)。跳頻同步算法[7]的性能主要考慮達到同步所需要的時間和精度,幀結(jié)構(gòu)[9]主要考慮到跳頻數(shù)據(jù)的平衡和發(fā)送速率。其中,跳頻圖案的同步是關(guān)鍵,能否快速、準確地實現(xiàn)跳頻圖案的同步,直接關(guān)系到能否實現(xiàn)數(shù)據(jù)的正確接收與判決。載波同步由頻率合成器的性能來保證,位同步和幀同步與一般的數(shù)字通信系統(tǒng)相同。

2.2.1 跳頻控制模塊的功能

電臺開機或由其他工作狀態(tài)進入跳頻工作方式后,首先進行初始化,然后轉(zhuǎn)入搜索狀態(tài),一方面檢測PTT線是否指示發(fā)狀態(tài),一方面搜索同步信息。一旦檢測到PTT線是指示發(fā)初始同步信息,隨即轉(zhuǎn)入正常跳頻狀態(tài);若接收到同步信息,則也轉(zhuǎn)入正常跳頻狀態(tài)。在正常跳頻狀態(tài),一方面用戶可以進行話音或數(shù)據(jù)通信;另一方面,若電臺處于發(fā)送狀態(tài),并檢測到PTT己經(jīng)松開,則發(fā)完結(jié)束信息后轉(zhuǎn)入搜索狀態(tài);若電臺處于接收狀態(tài),并檢測到有效的結(jié)束信息,則也轉(zhuǎn)入搜索狀態(tài)。從以上分析可以看出,電臺主要有三種工作狀態(tài),即發(fā)送狀態(tài)、接收狀態(tài)和搜索狀態(tài),而且跳頻電臺工作狀態(tài)設(shè)置及其轉(zhuǎn)移具有以下特點:

①同步搜索態(tài)是電臺的常態(tài),或稱穩(wěn)態(tài),電臺開機后,只要是進入跳頻,電臺無論是發(fā)方還是收方,都將首先處于同步搜索狀態(tài),遲入網(wǎng)同步也從搜索態(tài)開始。

②這是一個閉環(huán)同步系統(tǒng),電臺開機后,不需要人工的同步操作,全部自動實現(xiàn),方便戰(zhàn)術(shù)使用。

2.2.2 數(shù)據(jù)幀結(jié)構(gòu)及同步跳

(1) 初始同步信息構(gòu)成

同步信息分成2組(記為A組、B組);每組同步消息幀包含80位數(shù)據(jù),第一組用4個同步頻率(f1,f2,f3,f4)傳送,第二組用另4個同步頻率(f5,f6,f7,f8)傳送;其中第1組同步信息(稱為A組)重發(fā)5次,第2組同步信息(稱為B組)重發(fā)2次;同時在每組同步信息跳之后,分別在A組和B組同步信息跳之后插入2跳偽同步跳(f9,f10)和(f11,f12)。這樣,初始同步跳共發(fā)送了32跳。以400跳/s的跳速發(fā)送這32跳同步信息,則初始同步時間需要80 ms。A組信息結(jié)構(gòu)如下:

同步信息的構(gòu)成除TOD低位外還包括前導(dǎo)序列、幀頭、網(wǎng)號、與慢跳結(jié)束時刻的時間差等,B組同步信息結(jié)構(gòu)如下:

(2) 勤務(wù)同步幀結(jié)構(gòu)

在數(shù)據(jù)跳中,偽隨機地插入了勤務(wù)跳,遲入網(wǎng)電臺可通過搜索這些位于數(shù)據(jù)跳中的勤務(wù)跳來完成入網(wǎng)。勤務(wù)跳頻的4個頻點和初始同步頻點一樣,根據(jù)TOD信息和密鑰隨機的選出,并且4個頻點均勻分布在整個跳頻頻帶內(nèi)。勤務(wù)跳頻內(nèi)的同步信息與初始同步信息結(jié)構(gòu)基本一致,由保護時間、幀同步、網(wǎng)號、TOD組成,幀結(jié)構(gòu)如下:

接收機在1000跳/s的數(shù)據(jù)接收狀態(tài)下根據(jù)勤務(wù)跳的同步信息不斷調(diào)整本地時鐘,以實現(xiàn)跳頻的跟蹤保持狀態(tài)。當發(fā)射機停止發(fā)數(shù)后,自動發(fā)送8跳結(jié)束標志信息,接收機收到結(jié)束標志信息后斷開基帶數(shù)據(jù)通路,以停止接收數(shù)據(jù),并且迅速轉(zhuǎn)入慢跳搜索狀態(tài)。結(jié)束信息在每次松開PTT鍵后發(fā)送。

(3) 數(shù)據(jù)跳幀結(jié)構(gòu)

數(shù)據(jù)跳幀格式如下:

由于以9.6 kbps的用戶速率傳送96字節(jié)數(shù)據(jù)需要80 ms時間,經(jīng)過Rs編碼與交織等處理后,整包數(shù)據(jù)變?yōu)?52字節(jié)。傳送152字節(jié)數(shù)據(jù),使用1000跳/s的跳速,76個數(shù)據(jù)跳全部發(fā)送完畢。剩余的4 ms時間內(nèi)插入4個頻點的勤務(wù)同步跳,共4跳,作為勤務(wù)同步和遲入網(wǎng)同步。因此本跳頻系統(tǒng)中設(shè)計了一個跳頻通信周期為80 ms,如表1所列。

表1 各時鐘關(guān)系

一個通信周期為80 ms,每1 ms容納32個基帶位(基帶速率為32 kbps)。

發(fā)端在按下PTT(Push To Talk)鍵時先發(fā)送一組同步頭,用來傳送初始同步信息[10],然后再發(fā)送語音信息。初始同步信息由初始同步頻率進行發(fā)送,根據(jù)發(fā)送的初始同步信息,初始同步頻率分成兩組,每組有4個同步頻率組成,為了提高同步的抗干擾性能,同步的頻率是隨著時間的變化而更新的。第一組頻率為f1、f2、f3、f4,每隔100個通信周期換掉一個同步頻率,用于傳送A組初始同步信息,傳送完A組同步信息后插入兩跳偽隨機跳頻(f9,f10)。第二組頻率為f5、f6、f7、f8,也是每隔100個通信周期換掉一個同步頻率,用于傳送B組初始同步信息,傳送完B組同步信息后插入兩跳偽隨機跳頻(f11,f12)。每次按下PTT鍵,發(fā)送32跳的初始同步信息,其發(fā)送格式如圖5所示。

圖5 初始同步信息發(fā)送

正常跳頻通信時在語音跳中間加傳勤務(wù)同步跳,每800跳為一個通信循環(huán),每80跳為一通信周期,每個通信周期傳4跳(f1,f2,f3,f4)勤務(wù)同步信息發(fā)送。

結(jié)語

基于FPGA的跳頻通信接收系統(tǒng)與常規(guī)跳頻通信接收系統(tǒng)相比,該系統(tǒng)具有靈活性強、可靠性高、開發(fā)周期短和費用低等優(yōu)點,可廣泛應(yīng)用于通信領(lǐng)域。在測試過程中發(fā)現(xiàn)本文設(shè)計的系統(tǒng)滿足性能要求:4.8 kbps以下業(yè)務(wù)跳頻同步時間小于6 s,4.8 kbps以上業(yè)務(wù)跳頻同步時間小于0.6 s。

電子發(fā)燒友App

電子發(fā)燒友App

評論