在傳統的數據采集系統中,A /D的控制和數據的轉存均通過CPU或者MCU來完成。在這種方式下,將A /D轉換的結果讀入,然后再轉存到片外的存儲器中,這一過程至少需要4個機器周期。即使對于ARM芯核的單片機(CPU采用流水線結構, 1個機器周期占1個CLK) ,使用33 MHz的晶振,它的最高轉存數據速度也只達到8Mbit/ s. 在高速采樣系統中,這種方式一方面占用太多CPU資源,另外也遠遠不能滿足高速采樣的速度要求。同時,在數據采集系統的前端數字信號處理(DSP)中,如FFT、F IR、IIR濾波等,以往一般都是利用DSP內部的硬件乘法器加軟件控制來實現。DSP 的工作方式是通過內部的CPU 逐條執行軟件指令來完成各種運算和邏輯功能的,在排隊式串行指令執行方式下,工作速度和效率也將降低。為了提高數字信號處理速度,現在一些實現專用算法的DSP模塊和通信接口也由FPGA 或者CPLD 實現。基于上述原因,設計了以Virtex - 5系列的XC5VLX50為核心處理芯片的多路數據采集系統,它以硬件電路方式來提高速度[ 1 ]。

1 高速數據采集系統設計

1.1 高速數據采集系統的基本電路結構

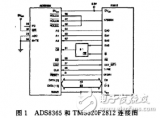

系統中,通過多路數據選擇器選定多路信號中的一路進行采集,在高速狀態機控制下,將采集到的模擬信號經過多片A /D器件流水轉換之后,轉換結果直接儲存到FPGA XC5VLX50TFFG1136內部由Block RAM構建的高速緩沖RAM陣列中,然后轉存至低速存儲器( FLASHMEMORY)中,再由FPGA構成的專用數字信號處理單元進行數據處理。在嵌入式硬核CPU Power PC405的控制下又可以將FLASH MEMORY中的數據送入PCI總線設備或者硬盤中長期存儲,同時也可以將采樣結果在LCD上顯示。該系統的結構框圖如圖1 所示。虛線內部的功能都是通過對FPGA芯片XC5VLX50TFFG1136硬件編程實現。

1.2 FPGA芯片XC5VLX50

XC5VLX50內部有豐富的資源,包括8個數字時鐘管理器(DCM, 290 Kbits的分布RAM, 88 ×16KByte 的Block RAM, 88個18 ×18 的專用乘法器(DedicatedMultip liers)單元, 2個Pow2erPC405內核, 564個可配置I/O 引腳達(最多276 對差分I/O,

速度高達31125 Gbit / s,最高內部工作頻率540 MHz. Power2PC405內核通過Xilinx提供的IP軟核編程實現,文中使用了內

部一個Power PC 405作為主控制器,用來完成高分辨率的液晶顯示器的控制和一些外圍設備和整個系統的協調性控制[ 2 ]。

2 流水采樣實現

采用高帶寬( 1 GHz) 高速( 80 MHz) 低功耗A /D 芯片AD9432 (12bit)作為A /D轉換器件,采樣時鐘由XC5VLX50內部的鎖相環實現。AD9432是一種單流水線ADC,它采用多個低精度閃電式ADC對采樣信號進行分級量化,然后將各級的量化結果組合起來以構成一個高精度的量化輸出。各級電路分別有自己的跟蹤保持電路,因此當每級電路把信號傳給下級電路時就可以接收上級傳過來的數據,每級電路一次采樣可在一個時鐘周期內完成,但是存在流水線延遲的問題,AD9432采樣轉換過程如圖2所示。

每次采樣的最終轉換結果要等待6~7個時鐘周期后才能出現在輸出端。AD9432的控制以及數據的緩沖轉存采用狀態機控制,當AD9 4 3 2接收到CLK信號后開始采樣。由于每塊A /D 的最高采樣率僅有80MHz,在此采用了4塊AD9432進行

流水采樣,每塊A /D的采樣時鐘相位延遲90°,這樣在每個周期內是由4 塊A /D均勻采樣的,采樣率等效提高了4倍。4塊AD9432采樣時鐘的相位延遲利用FPGA設計的高速狀態機以及內部數字時鐘管理器(DCM)來實現。采用4片A /D相位延

遲并行流水采集的過程如圖3所示,圖中CLK1~4是4片A /D的采樣時鐘,在這種流水采集中,單流水線延遲的影響可以忽

略[ 3 ]。

3 數據的轉存設計和分析驗證

采集到的信號經過A /D器件轉換之后,通過XC5VLX50內部高速緩沖,轉存到片外存儲器FLASH MEMORY中。系統中

XC5VLX50內部Block RAM陣列的控制比較簡單,采用乒乓操作大大降低了采樣數據讀取處理速度。16塊Block RAM分成

2組,時鐘和控制信號均獨立。系統工作時,高速狀態機會不斷地往Block RAM中放入采集到的數據。當采樣數據放滿1組

的8塊Block RAM后自動切換到另外一組。同時并行從剛剛放滿的8 塊Block RAM 中以64 位的并行數據讀入FLASH

MEMORY中( FLASH MEMORY內存具有可靠性高、互換性好、容量大等特點) [ 4 ]。

采用流水方式的4片12位的A /D的采樣頻率為320MHz,則數據流為480 Mbit/ s,但是FLASH MEMORY的最大存儲速度為20Mbit/ s(忽略編程時間). 為了實現數據的實時存儲,采用面積換取速度的原理,充分利用XC5VLX50的內部邏輯資源和豐富的I/O口資源,設計了2個存儲器陣列,每個存儲器陣列由24 片FLASH MEMORY,在XC5VLX50 內部進行乒乓操作,把480Mbit / s的數據量分流成20Mbit/ s,分別存儲到24片FLASH MEMORY中,當FLASHMEMORY達到編程時間的時候轉向第二個存儲陣列,這樣的外部乒乓操作就達到了FLASHMEMORY的最高存儲效率,實現了數據的高速實時采集和存儲, 2個存儲陣列共享控制總線和數據總線,但是使能總線獨立;在一個存儲陣列內部,存儲芯片控制總線共享,數據總線獨立,這樣能達到緊密協作和節省FPGA邏輯資源和I/O口資源的效果。而設計的FLASH MEMORY 控制器的速度達480MHz,數據帶寬符合轉存需要的速度,完全可以實現實時連續采樣。數據采集結束后,DSP模塊會在Power PC405的控制下對FLASH MEMORY內存中的數據進行高速處理,然后又放回FLASH MEMORY中,處理后的數據也能通過PCI總線傳到帶有PCI接口的設備中,或者通過USB總線存儲到硬盤中,對PCI和硬盤操作均支持DMA66操作[ 5 ] 。

系統的Power PC405采用Xilinx的IP Core實現。FLASHMEMORY Controller、PCI Controller及USB Controller等功能電

路則是根據相應的數據傳輸協議自行設計,采用VHDL 編程實現,使用ModelSim進行功能仿真, Synp lify進行邏輯綜合,將綜合結果下載到XC5VLX50 器件中實現相應的系統邏輯功能。

在完成電路的軟件與硬件系統設計以后,用Agilent16900Logic Analysis和高速示波器對該電路進行測試驗證。16900

LA的多通道眼圖的掃描可以迅速發現FLASH MEMORY總線中一些處于比較危險狀態的信號線,比如由于阻抗的不匹配而造成Signal Integrity方面的問題。而LA可以驗證電路時序是否正確。用示波器可以正確地量測到實際信號的波形,并進行眼圖的精確掃描。用16900 Logic Analysis測量了FLASHMEM2ORY控制電路的部分時序,結果表明FLASH MEMORY總線邏輯功能正確,符合FLASH MEMORY總線規范標準。對于PCI Controller、IDE Controller、DMA Controller均采用了相同方式進行量測驗證,結果均符合其協議規范標準,可以正常穩定地工作。

4 結束語

介紹了一種基于FPGA控制的,進行多片A /D器件流水采集的高速數據采集系統設計,對流水采樣的原理和實現、采集

中的數據轉存控制電路和FLASHMEMORY控制電路的設計進行了重點分析。在完成電路的軟件與硬件系統設計以后,用Agilent 16900 Logic Analysis和高速示波器進行測試驗證。結果表明該系統可以可靠穩定地工作,最高實時采集采樣頻率可以達到480MHz. 并應用到了雷達信號高速數據采集器中,在多次的實際應用中表現穩定、可靠。

電子發燒友App

電子發燒友App

評論