什么是鍵盤的鍵位沖突?

簡單的說,也就是當你同時按下鍵盤上的幾個鍵的時候,這幾個鍵不能同時反映出來,這就叫做鍵盤的鍵位沖突。例如說,你能想象當你按下Ctrl-Alt-Del時,系統只能接收到前兩個鍵,而死活不承認你按了Del鍵嗎?

?????? 當然,現實中是不會有這樣的鍵盤的,按不下Ctrl-Alt-Del的鍵盤根本就沒法出廠,但其他一些常見的鍵位沖突就不稀奇了。例如,經常有一些鍵盤不能同時對例如A-S-空格這樣的按鍵組合作出反應,這樣在FPS游戲中,使用者就會大為吃虧。

?????? 對于鍵位沖突問題,電腦用戶中有兩種完全不同的態度,絕大多數人根本意識不到鍵位沖突問題的存在,直到遇到沖突的時候才叫苦不迭,并且大呼“為什么他就能 做這個動作?”;而另一部分人,特別是一些游戲高手,又在孜孜不倦的尋找“沒有鍵位沖突的鍵盤”。這兩種人都是對鍵位沖突的原因認識不清楚的。

?????? 鍵位沖突的直接起因,是鍵盤的非編碼結構。在2月號的專題中,我們提到過現在的鍵盤幾乎都是非編碼的薄膜接觸式鍵盤,那么什么是非編碼鍵盤呢?在專題里我們沒有詳細的解釋,下面我們就來詳細說明一下非編碼鍵盤的原理與結構。

?????? 傳統的鍵盤,是編碼式鍵盤,它的每個鍵按下時都會產生唯一的按鍵編碼,并且通過專有的一組導線傳輸到鍵盤接口電路,由于其線路和編碼的唯一性,這種鍵盤是不存在鍵位沖突的問題的,但是編碼鍵盤結構復雜,現在已經很少使用了。

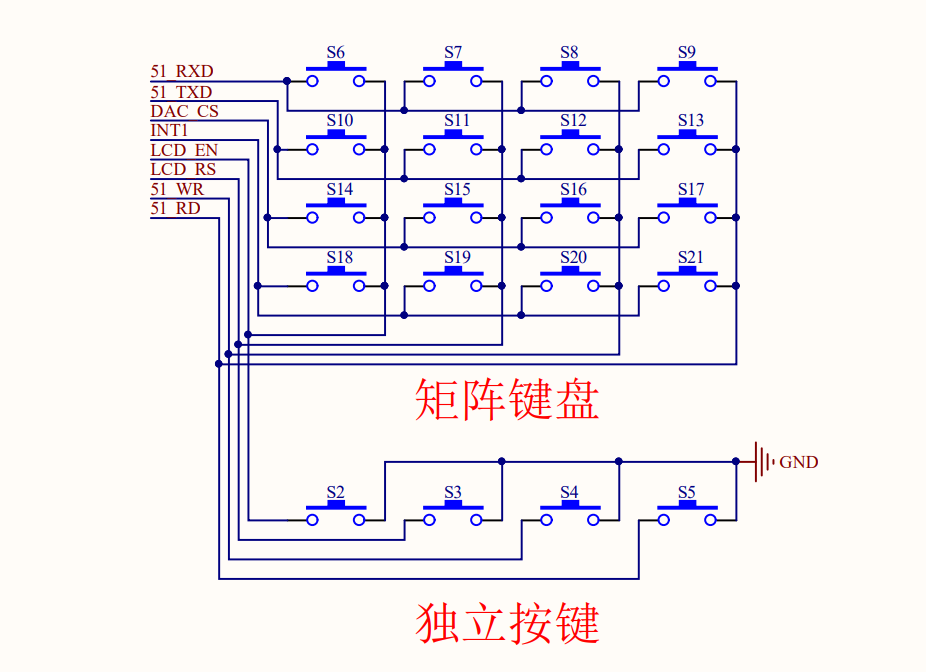

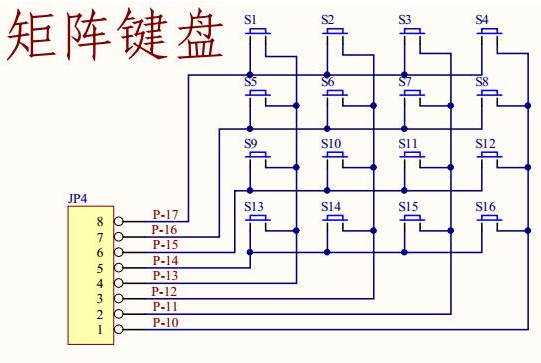

?????? 而現代的薄膜接觸式鍵盤,任何一個按鍵都有上下兩層薄膜的觸點,我們將它拆開來仔細看一看(如圖),就會發現在任何一層薄膜上,導線數都遠少于按鍵數,而 且每一條導線都同時連通多個按鍵的觸點,而且,上層和下層的任何兩條導線都最多只在一個按鍵上重合。也就是說,上層的1號導線可能會同時經過1、2、3、 4、5……等按鍵,而下層的1號導線可能同時經過1、Q、A、Z……等按鍵,且兩條導線只在1鍵上重合。

?????? 什么是鍵盤的鍵位沖突?簡單的說,也就是當你同時按下鍵盤上的幾個鍵的時候,這幾個鍵不能同時反映出來,這就叫做鍵盤的鍵位沖突。例如說,你能想象當你按下Ctrl-Alt-Del時,系統只能接收到前兩個鍵,而死活不承認你按了Del鍵嗎?

?????? 當然,現實中是不會有這樣的鍵盤的,按不下Ctrl-Alt-Del的鍵盤根本就沒法出廠,但其他一些常見的鍵位沖突就不稀奇了。例如,經常有一些鍵盤不能同時對例如A-S-空格這樣的按鍵組合作出反應,這樣在FPS游戲中,使用者就會大為吃虧。

?????? 對于鍵位沖突問題,電腦用戶中有兩種完全不同的態度,絕大多數人根本意識不到鍵位沖突問題的存在,直到遇到沖突的時候才叫苦不迭,并且大呼“為什么他就能 做這個動作?”;而另一部分人,特別是一些游戲高手,又在孜孜不倦的尋找“沒有鍵位沖突的鍵盤”。這兩種人都是對鍵位沖突的原因認識不清楚的。

?????? 鍵位沖突的直接起因,是鍵盤的非編碼結構。在2月號的專題中,我們提到過現在的鍵盤幾乎都是非編碼的薄膜接觸式鍵盤,那么什么是非編碼鍵盤呢?在專題里我們沒有詳細的解釋,下面我們就來詳細說明一下非編碼鍵盤的原理與結構。

?????? 傳統的鍵盤,是編碼式鍵盤,它的每個鍵按下時都會產生唯一的按鍵編碼,并且通過專有的一組導線傳輸到鍵盤接口電路,由于其線路和編碼的唯一性,這種鍵盤是不存在鍵位沖突的問題的,但是編碼鍵盤結構復雜,現在已經很少使用了。

?????? 而現代的薄膜接觸式鍵盤,任何一個按鍵都有上下兩層薄膜的觸點,我們將它拆開來仔細看一看(如圖),就會發現在任何一層薄膜上,導線數都遠少于按鍵數,而 且每一條導線都同時連通多個按鍵的觸點,而且,上層和下層的任何兩條導線都最多只在一個按鍵上重合。也就是說,上層的1號導線可能會同時經過1、2、3、 4、5……等按鍵,而下層的1號導線可能同時經過1、Q、A、Z……等按鍵,且兩條導線只在1鍵上重合。

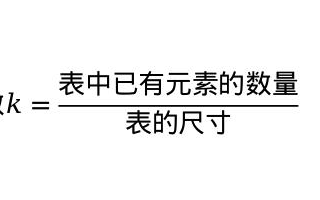

?????? 這樣,根據上層薄膜和下層薄膜所經過的按鍵,就可以排出一個類似下面的表格:

?

|

? ? |

? 上層導線1 |

? 上層導線2 |

? 上層導線3 |

? 上層導線4 |

? 上層導線5 |

? …… |

|

? 下層導線1 |

? 1 |

? 2 |

? 3 |

? 4 |

? 5 |

? …… |

|

? 下層導線2 |

? Q |

? W |

? E |

? R |

? T |

? …… |

|

? 下層導線3 |

? A |

? S |

? D |

? F |

? G |

? …… |

|

? 下層導線4 |

? Z |

? X |

? C |

? V |

? B |

? …… |

|

? …… |

? …… |

? …… |

? …… |

? …… |

? …… |

? …… |

在非編碼鍵盤的接口控制電路中,就存儲著這樣一張表格,當按下某個按鍵,例如“Q”時,那么在這一點上,上下兩個觸點就會連通,反映到接口電路中,就會檢 測到上層導線1與下層導線2被連通了。相對應在表中一查,就會知道,被按下的是字母“Q”,然后通過接口輸出其ASCII碼。

?????? 與老式的編碼式鍵盤相比,非編碼鍵盤的結構要簡單許多,省略了復雜的編碼電路和蜘蛛網似的走線,而且更重要的是,由于非編碼式鍵盤將按鍵結構和輸出鍵碼分 離,所以當需要制造不同鍵位排列的鍵盤時,不需要重新設計鍵盤線路,而只要將控制電路中的鍵位排列表格重新刷新就可以了。例如在德文鍵盤上,子母“Y”和 “Z”的位置是互調的,那么如果要把一條英文鍵盤生產線改造成德文鍵盤生產線,什么都不用改變,只須在控制芯片中刷進一個新的排列表,將“上層導線1-下 層導線4”的位置寫作“Y”,“Z”字也作同樣處理就行了,顯然比重新布線要簡單了很多。這也就是為什么非編碼式鍵盤大行其道的原因。

?????? 但是非編碼式鍵盤帶來的就是“鍵位沖突”的問題。以上面的按鍵排列表為例,當按下一個按鍵時,鍵盤肯定會正常識別的;當按下兩個按鍵時,例如同時按下 “Q”與“D”,此時上層導線1與下層導線2連通,而上層導線3與下層導線3連通,系統完全可以正常識別;或者同時按下“Q”與“E”,此時,上層導線 1、下層導線2、上層導線3同時連通,系統同樣可以正常識別出是按下了這三個按鍵。

?????? 但在同時按下3個或3個以上按鍵時,情況就復雜了。

?????? 在一種情況下,例如同時按下“Q”、“D”、“B”時,此時,從表中我們可以看出,上層導線1-下層導線2、上層導線3-下層導線3、上層導線5-下層導線4都分別連通,此時系統完全可以正常識別出按下了這三個按鍵。

?????? 但當按下的第三個按鍵不是“B”,而是“E”呢?

?????? 此時,我們可以發現,由于第三組連通的導線變成了上層導線3-下層導線2,所以,此時反映到接口控制芯片的信號是:上層導線1-下層導線2-上層導線3-下層導線3統統被連通到了一起。

?????? 但是,問題就在于,除了按下的第三個按鍵是“E”以外,如果按下的第三個鍵是用來連通上層導線1和下層導線3的“A”,也會有同樣的信號組合?事實上, “Q”、“E”、“A”、“B”四個按鍵中按下任何三個都會有同樣的信號組合,那么此時接口電路怎么判斷呢?究竟是按下了哪三個按鍵或者是同時把四個按鍵 都按下了呢?

?????? 這個時候,大多數鍵盤選擇的方式,就是按照一個固定的規則輸出固定的按鍵組合代碼,對于其他可能的組合方式統統予以忽略,換句話說,在上面的鍵盤中,可能 無論你怎么按這四個按鍵,它可能永遠只會輸出“Q”-“E”-“D”的組合,盡管可能你按下的實際是“Q”-“A”-“D”(這里只是一個假設,實際上為 了避免誤碼,大多數鍵盤根本只輸出兩個按鍵而已)。于是,“鍵位沖突”就出現了。

?????? 由于非編碼鍵盤的固有結構,“鍵位沖突”是不可避免的。于是就需要鍵盤的設計者絞盡腦汁修改鍵盤的線路排列和待查表格,盡量使可能會有的常用組合按鍵避開 沖突鍵位——盡管要做到所有的按鍵都不發生沖突是不可能的,但你總不能讓Ctrl-Alt-Del相互沖突吧?那這樣的鍵盤還怎么用?還有如果四個方向鍵 相互沖突,那賽車類的游戲還怎么玩?

?????? 不過,由于市場上的游戲實在太多,每個游戲都可能會有自己常用的按鍵組合,甚至每個人都有自己的習慣按鍵,鍵盤的設計者當然不可能面面俱到,有經驗的設計 師可能會考慮得多一些,至少對最常見的游戲和最常見的按鍵設置能夠保證不出現問題,但要考慮到所有情況當然是不可能的。

?????? 所以,當你購買鍵盤的時候,絕對不要忽略“鍵位沖突”的問題,一定要把鍵盤裝到電腦上,試一試自己常玩的游戲是否能夠正常使用(只有實際試用才能試出鍵位 沖突問題,由于它與鍵位表相關,所以看外表是看不出來的)。同時,一些游戲高手朋友也不要白費心機去尋找什么“沒有鍵位沖突的鍵盤”了,只要它依然是非編 碼鍵盤,那么鍵位沖突就是不可避免的,只要它的鍵位沖突不對你所玩的游戲構成影響,這就足夠了。

PS/2協議分析

The PS/2 mouse and keyboard implement a bidirectional synchronous serial protocol.

PS/2鼠標和鍵盤執行一個雙向同步串行協議。

The bus is "idle" when both lines are high (open-collector).

總線空閑時,兩條線都是高電平(集電極開路)。

This is the only state where the keyboard/mouse is allowed begin transmitting data.

在這種狀態下,鍵盤/鼠標才允許開始傳輸數據。

The host has ultimate control over the bus and may inhibit communication at any time by pulling the Clock line low.

主機對總線有最高的控制權,在任何時候通過將時鐘線拉低就可以禁止通信。

The device always generates the clock signal.

時鐘信號總是由設備端生成的。

If the host wants to send data, it must first inhibit communication from the device by pulling Clock low.

如果主機想發送數據,它必須先將時鐘拉低來禁止來自設備端的通信。

The host then pulls Data low and releases Clock.

然后主機再拉低數據線,釋放時鐘。 注釋:釋放時鐘,就是再恢復時鐘為高

This is the "Request-to-Send" state and signals the device to start generating clock pulses.

這就是"請求發送(Request-to-Send)"狀態,提示 設備端 開始生成時鐘信號。

Summary: Bus States

Data = high, Clock = high: Idle state.

Data = high, Clock = low: Communication Inhibited.

Data = low, Clock = high: Host Request-to-Send

總結:總線狀態

????????????? 數據????????????????????? 0??????????????????????? 1

????????????????????????? 0????????? ---------通信禁止-----------

??? 時鐘

????????????????????????? 1????????? 主機要求發送????????? 總線空閑

The clock and data pins are bidirectional, open-collector

signals that are pulled to 5 V by pullup resistors in the keyboard.

時鐘和數據 引腳時 雙向 集電極開路的信號,可以被鍵盤內部的上拉電阻 拉高到5V

Data sent from the device to the host is read on the falling edge of the clock signal; data sent from the host to the device is read on the rising edge.

從設備發送給主機的數據時在時鐘信號的下降沿讀取的;從主機發給設備的數據是在上升沿讀取的。

The clock frequency must be in the range 10 - 16.7 kHz. This means clock must be high for 30 - 50 microseconds and low for 30 - 50 microseconds..

時鐘頻率必須在10-16.7KHz之間。這意味著時鐘必須是 高電平持續30~50毫秒,低電平持續

30~50毫秒。

If you're designing a keyboard, mouse, or host emulator, you should modify/sample the Data line in the middle of each cell. I.e. 15 - 25 microseconds after the appropriate clock transition.

如果你設計一個鍵盤 鼠標 或者 主機模擬器,你必須 在每個單元的中間時刻 (也就是,在時鐘跳變之后的15~25毫秒后) 修改/取樣數據線.

Again, the keyboard/mouse always generates the clock signal, but the host always has ultimate control over communication.

重復一遍,鍵盤/鼠標 總是 生成時鐘信號, 而 主機 控制著整個通信過程。

Timing is absolutely crucial. Every time quantity I give in this article must be followed exactly.

時序是非常重要的。在本文中給出的時間數必須嚴格遵循。

電子發燒友App

電子發燒友App

評論