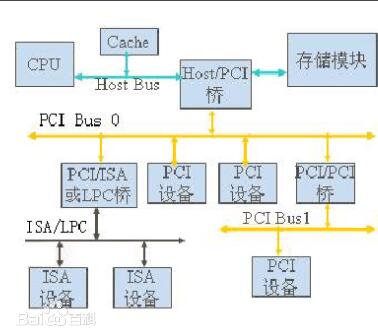

外圍部件互連總線PCI(Peripheral Component Interconnect)總線,是一種先進的高性能32/64位地址數據復用局部總線,可同時支持多組外圍設備,并且不受制于處理器,為中央處理器與高速外圍設備提供了一座溝通的橋梁,提高了數據吞吐量(32位時最大可達132 MB/s),是現在PC領域中流行的總線。PCI總線具有嚴格的總線規范,這就保證了它具有良好的兼容性,符合PCI總線規范的擴展卡可以插入任何PCI系統可靠地工作。

1 PLX-PCI9054的結構和性能

PCI9054是PLX公司生產的PCI總線通用接口芯片,采用先進的PLX數據管道結構技術,符合PCIV2.1和V2.2規范。提供2個獨立的可編程DMA控制器,每個通道均支持塊和分散/集中的DMA方式,在PCI總線端支持32位/33 MHz,本地端可以編程實現8、16、32位的數據寬度,傳輸速率最高可達132 MB/s,本地總線端時鐘最高可達50 MHz支持復用/非復用的32位地址數據。

PCI9054提供了PCI、EEPROM、LOCAL總線3個接口。PCI9054作為一種橋接芯片在PCI總線和LOCAL總線之間提供傳遞消息,既可以作為兩個總線的主控設備去控制總線,也可以作為兩個總線的目標設備去響應總線。PCI9054有6個零等待可編程FIFO存儲器,它們分別完成PCI發起讀、寫操作,PCI目標讀、寫操作和DMA讀、寫操作。由于FIFO存儲器的存在,數據可以大量突發傳輸而不丟失。這樣不僅滿足實時性要求,同時可根據用戶的需要采用與PCI時鐘異步的本地頻率。串行EEPROM是用來在開機時初始化配置內部寄存器的。內部寄存器(ItnternalRegis-ters)標識地址映射關系以及PCI端和本地端工作狀態,包括PCI配置寄存器組、Local配置寄存器組、Runtime寄存器組、DMA寄存器組、I2O消息寄存器組。FIFO和內部寄存器在計算機主機或者本地端都是統一編址的,用戶可以從兩端通過編程訪問它們的每一個字節。

2 數據轉換模塊設計實現

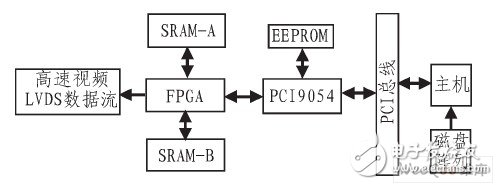

數據轉換模塊主要是為了把軟件仿真的數據通過PCI總線DMA傳輸,經緩存、解碼、編碼、驅動等處理轉換成高速串行數據流(LNDS數據流)。本設計中,數據轉換模塊的硬件組成包括:PCI接口芯片PCI9054、FIGA、EEPROM和SRAM。數據轉換模塊設計原理框圖如圖1所示。

圖1 數據轉換模塊設計原理框圖

2.1 PCI9054硬件接口設計

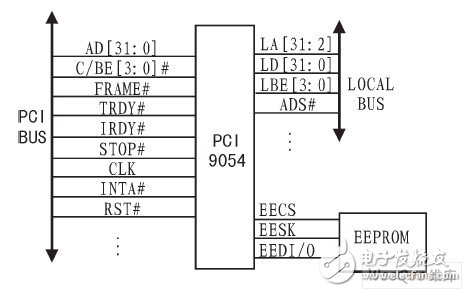

PCI9054供了3種物理總線接口:PCI總線接口、LOCAL總線接口和串行EPROM接口。FPGA通過專用接口芯片PCI9054與PCI總線相連,在FP-GA內部分配一塊RAM用作數據的緩沖區,可用VHDL語言編程實現FPGA作為RAM控制器。PCI9054專用接口芯片內部2個獨立DMA通道,可以實現系統數據在PC機內存與PCI板卡之間的高速傳輸,接口電路示意圖如圖2所示。

圖2 接口電路示意圖

2.1.1 PCI9054與PCI總線接口

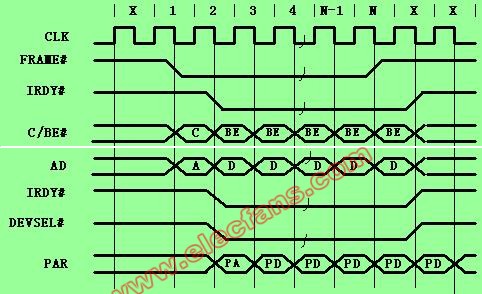

PCI9054與PCI總線接口連接相對簡單,只要將PCI9054芯片的PCI端信號線與PCI插槽相應的信號線對應連接即可。這些信號包括地址數據復用信號、接口控制信號線、中斷等信號線。在電路板制作上,需注意PCI總線信號的走線,為了滿足反射條件,對信號走線有嚴格要求:普通信號長度,從插槽連接器到PCI橋芯片不大于1.5 inch(1 inch=0.025 4 m),CLK信號走線長度為2.5±0.1 inch。否則會導致信號不穩定甚至總線沖突,無法開機。

2.1.2 PCI9054與LOCAL Bus接口

PCI9054與本地信號接口是相對重要的一部分。PCI9054有3種工作模式:M、C和J模式。M模式是專為Motorola公司的MCU設計的工作模式,主要針對Motorola公司高性能PC850/860的應用而設計。C模式下PCI9054芯片通過片內邏輯控制將PCI的地址線和數據線分開,方便地為本地工作時序提供各種工作方式,一般廣泛應用于系統設計中。J模式是一種沒有Local Master的工作模式,它的好處是地址數據線沒有分開,嚴格仿效PCI總線的時序。J模式的接口設計相對復雜,最常用的是C模式。C模式下PCI9054分為PCIInitiator操作和PCI Target操作。在PCI Initiator操作過程中,本地總線主控設備能夠直接通過PCI9054訪問PCI總線,發起Local-to-PCI的數據傳輸。而在PCI Target操作過程中,PCI總線主控設備可以以總線寬度和突發傳輸功能訪問PCI9054的3個本地空間(空間0,空間1和擴充ROM空間),本設計就采用了C模式。

信號線連接主要包括:LHOLD(申請使用本地總線,輸出信號)、LHOLDA(對LHOLD應答,輸入信號)、ADS#(新的總線訪問有效地址的開始,在總線訪問first clock設置時輸出信號)、BLAST#(表示為總線訪問的last transfer,輸出信號)、LW/R#(高電平表示讀操作,低電平表示寫操作,輸出信號)、LA[31:2](地址線)、LD[31:0](數據線)、READY#(表示總線上讀數據有效或寫數據完成,用以連接PCI9054等待狀態產生器,輸入信號)。

2.1.3 PCI9054與EEPROM接口

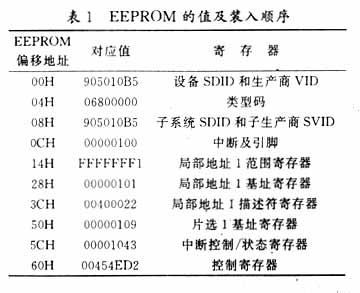

PCI9054在加電啟動時,需要從外部EEPROM讀取初始化數據來配置PCI9054的內部寄存器,而且依賴于硬件板卡的硬件資源要求,以及選擇正確的PCI9054工作模式。PCI9054提供4個管腳與串行EEPROM相連接,它們分別是EEDI、EEDO、EESK和EECS。本文選擇的串行EEPROM是93L-C56,因此對應于93LC56的DI、DO、SK、CS這4個管腳。

在計算機加電自檢期間,PCI總線的RST#信號復位。PCI9054內部寄存器的默認值作為回應。PCI9054出本地LRESET#信號并檢測串行EEP-ROM,若串行EEPROM中的前33個bit不全為1,那么PCI9054確定串行EEPROM非空,用戶可通過向9054的寄存器CNTRL的29位寫1來加載EEPROM的內容到PCI9054的內部寄存器。配置的信息可在P1xSdk中的PLXMON下對EEPROM進行配置。

EEPROM配置信息主要包括以下兩部分:1)PCI配置寄存器,填寫生產商ID號、器件ID號、類碼子系統ID號和子系統生產商ID號。對于PCI-9054,其生廠商ID號為1OB5,器件ID號為9054,子系統號為9054,子系統ID號為10B5,類碼號為0680,表示其為橋設備中的其他橋設備類。 2)本地配置寄存器的配置,即對本地地址空間及其本地總線屬性的配置。這些配置要根據實際開發的硬件板卡的硬件資源進行配置。設備人員配置寄存器的任務就是要把某一段本地地址映射為PCI地址,也就是當主機CPU要訪問本地地址空間時,要知道其對應的PCI總線地址。

2.2 數據緩存器設計

數據緩存器由兩組SRAM組成,在模擬數據時,主機從磁盤陣列上讀取要模擬的數據,通過PCI總線的DMA傳輸給FPGA,首先存到SRAM-A里,SRAM-A存儲滿時,開始以一定的速率讀SRAM-A里的數據,并串轉換成串行數據,用LVDS信號形式發送,在讀的同時主機啟動第二次DMA傳輸數據給FPGA,再存到SRAM-B,SRAM-A讀完、SRAM-B寫滿就開始以一定的速率讀SRAM-B的數據,并串轉換成串行數據,用LVDS信號形式發送,這樣輪番交替形成“乒乓機制”,有效克服了數據流不連續的現象,解決了形成不間斷數據流和兩次DMA傳輸之間的數據間斷問題。

3 工作流程

在設計中,PCI端的數據傳輸主要是利用PCI9054的BLOCK DMA模式。PCI9054集成了2個相互獨立的DMA通道,每個通道都支持Block DMA和Scatter/Gather DMA,通道0還支持Demand DMA傳輸方式。

Block DMA要求PCI主機或Loeal主機提供PCI和Local的起始地址、傳輸字節數、傳輸方向。主機設定DMA開始位啟動DMA數據傳輸,一旦傳輸完成,PCI9054設定DMA“傳輸結束位”結束DMA。如果啟動中斷允許位,在傳輸結束時PCI9054將向主機(PCI主機或LOCAL主機)產生中斷。在DMA傳輸中,PCI9054既是PCI總線的主控器又是Loeal總線的主控器。

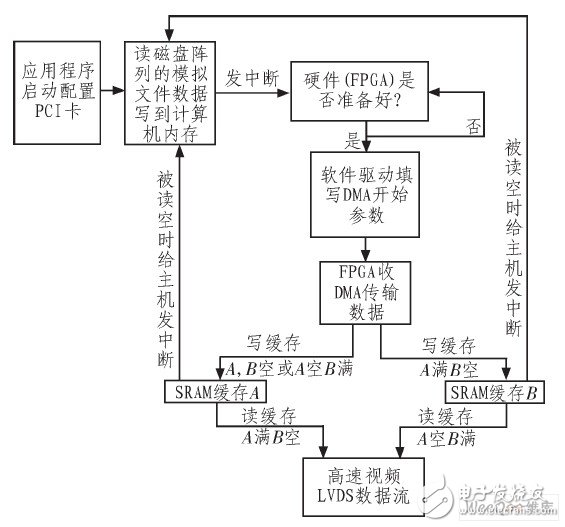

Scatter/Gather DMA要求主機在PCI空間或Local空間設定Descriptor模塊,模塊包括PCI和Local的起始地址、傳輸字節數、傳輸方向和下一個Descriptor模塊的地址。PCI9054載人第1個Descriptor模塊并發起傳輸,連續加載下一個模塊,直到它偵測到“鏈結束位”有效,PCI 9054設置“傳輸結束位”,或者申請PCI或Local中斷。這種模式下,PCI9054也可以在每個模塊加載時有效中斷信號,結束DMA傳輸。若Desc-riptor模塊在本地存儲空間,可以編程使DMA控制器在每次DMA傳輸結束后清除傳輸字節數。具體工作流程如圖3所示。

圖3 數據轉換流程圖

通過設置其DMA控制器內部的寄存器即可實現兩總線之間的數據傳輸。PCI9054的DMA傳輸過程可由以下幾個步驟實現:

1)設置方式寄存器:設置DMA通道的傳輸方式,寄存器DMAMODE0或者DMAMODE1;

2)設置PCI地址寄存器:設置PCI總線側的地址空間起始地址;

3)設置LOCAL地址寄存器:設置LOCAL總線側的地址空間起始地址;

4)設置傳輸計數寄存器:以字節位單位設置每次DMA數據傳輸量;

5)設置描述寄存器:設置DMA傳輸的方向,0表示數據從PCI總線到Local總線,1表示數據從Local總線到PCI總線;

6)設置命令/狀態寄存器:啟動或停止DMA操作。

當應用程序啟動開始模擬后,驅動程序收到應用程序開始模擬的命令后,同時填寫PCI9054的門鈴寄存器(PCI端偏移地址:60H)產生LO-CAL端的中斷通知硬件接收DMA的數據,FPGA收到中斷后,清除中斷,同時判斷收到開始模擬的命令。硬件準備好以后發中斷告訴主機已經準備好,同時填寫PCI9054的門鈴寄存器(PCI端偏移地址:64H)產生PCI端的中斷通知硬件已經準備好,主機收到中斷后,清除中斷,填寫啟動DMA開始寄存器,把計算機內存空間的數據通過PCI總線傳輸到PCI9054的LOCAL端,FPGA接收LOCAL端的數據存入數據緩沖區,同時由FPGA控制讀取緩沖區中的數據經并串轉換用LVDS信號形式發送。當DMA結束后產生主機PCI中斷,主機收到中斷后清除中斷,并等待硬件準備好中斷來后清中斷填寫下一個DMA開始,直到模擬數據模擬完為止。

4 WDM驅動程序設計

4.1 WDM驅動程序簡介

WDM驅動程序是一種PnP驅動程序,它同時還遵循電源管理協議,并能在Windows 98和Windows 2000間實現源代碼級兼容。WDM驅動程序還細分為類驅動程序(class driver)和迷你驅動程序(minidriver),類驅動程序管理屬于已定義類的設備迷你驅動程序向類驅動程序提供廠商專有的支持。在WDM驅動程序模型中,每個硬件設備至少有兩個驅動程序。其中一個驅動程序稱為功能(function)驅動程序,了解使硬件工作的所有細節,負責初始化I/O操作,處理I/O操作完成時所帶來的中斷事件,為用戶提供一種設備適合的控制方式。另一個驅動程序稱為總線(bus)驅動程序,它負責管理硬件與計算機的連接。例如,PCI總線驅動程序檢測插入到PCI槽上的設備并確定設備的資源使用情況,它還能控制設備所在PCI槽的電流開關。

4.2 驅動程序開發環境及設計

項目開發中選擇的是Numega公司的Driverstudio驅動程序開發工具包,它是建立在Windows Driver Development Kit之上的驅動程序開發工具,包含了VtoolsD、DriverWorks、DriverNetWorks和SoftICE等開發工具。DriverWorks用于開發普通設備的WDM驅動程序,SoftICE提供了強大的調試工具。在安裝Driverstudio之前,還需要安裝相應操作系統的DDK,如XPDDK和VC6.0工具。

在Driverstudio驅動程序向導里可以輕易方便地建立起PCI9054的驅動程序框架,而且Driverstudio還提供了PCI9054驅動程序中大量類函數的接口,降低了開發難度,縮短了程序編寫時間。調試程序可以使用SoftICE和Driver Moniter,極為方便查錯及優化程序設計。

5 結束語

本文通過介紹PCI總線接口協議芯片PCI9054的性能、特點,分析Windows的WDM驅動程序的特點,對所設計的數據轉換模塊結構進行了詳細說明,提出了雙SBAM結構數據緩存器的應用方案。應用結果表明,該設計可滿足數字視頻帶寬20 MHz以內的高速串行數據流(INDS數據流)的轉換與傳輸,保證了硬件內存大容量讀取的高速、實時性。

電子發燒友App

電子發燒友App

評論