設計原理

本系統中,Basys3的MicroBlaze模塊調用基于AXI協議的UART IP核,通過AXI總線實現MicroBlaze-UART之間的通信,完成串口打印。

操作步驟

一、基于GUI界面創建工程

1.?創建新的工程項目

1)?雙擊桌面圖標打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2)?點擊‘Create Project’,或者單擊File>New Project創建工程文件;

3)?將新的工程項目命名為‘lab6’,選擇工程保存路徑,勾選‘Create project subdirectory’,創建一個新的工程文件夾,點擊Next繼續;

4)?選擇新建一個RTL工程,由于本工程無需創建源文件,故將Do not specify sources at this time(不指定添加源文件)勾選上。點擊 Next繼續;

5)?選擇目標FPGA器件:xc7a35tcpg236-1或Basys3;

6)?最后在新工程總結中,檢查工程創建是否有誤。沒有問題,則點擊Finish,完成新工程的創建。

2. 創建原理圖,添加IP,進行原理圖設計。

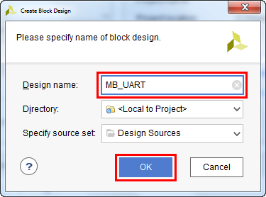

1)?在Project Navigator下,展開IP INTEGRATOR,選擇‘Create Block Design’創建新的原理圖設計;

2)?將新的設計命名為‘MB_UART’;

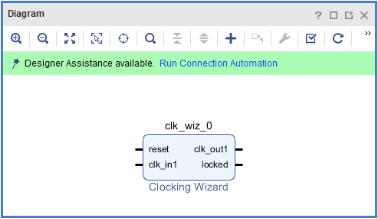

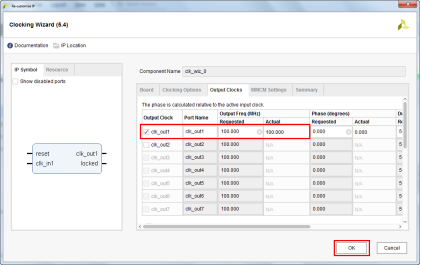

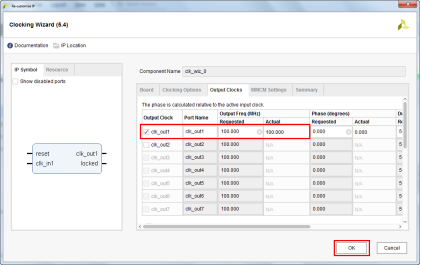

3)?添加一個clock IP,在原理圖(Diagram)界面中鼠標右擊,選擇‘Add IP’。在IP搜索框中輸入‘clocking’,雙擊添加Clocking Wizard;

4)?雙擊Clocking Wizard模塊進行自定義配置,選擇Output Clocks一欄,確定clk_out1頻率為100(MHz),Reset Type為Active High;

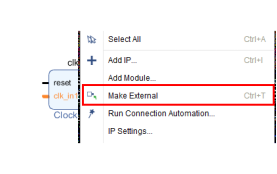

5)?鼠標右擊‘clk_in1’,選擇Make External添加引腳;

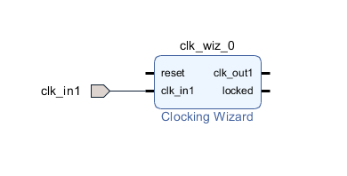

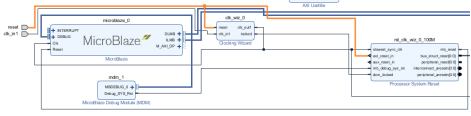

6)?完成后,如下圖所示:

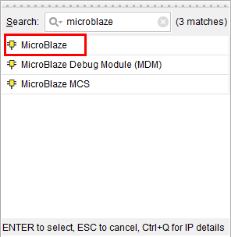

7)?同樣的,在Diagram中添加MicroBlaze IP;

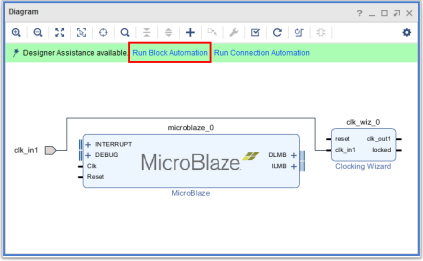

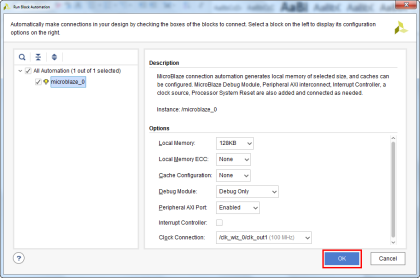

8)?添加完成后如下圖所示,點擊‘Run Block Automation’;

9)?在彈出窗口中,使用以下設置替換默認設置;

Local Memory: 128KBLocal Memory ECC: NoneCache Configuration: NoneDebug Module: Debug OnlyPeripheral AXI Port: EnabledInterrupt Controller: 不勾選Clock Connection: /clk_wiz0/clk_out1(100 MHZ)

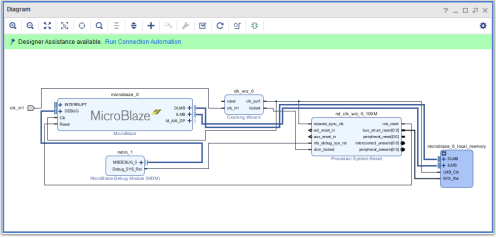

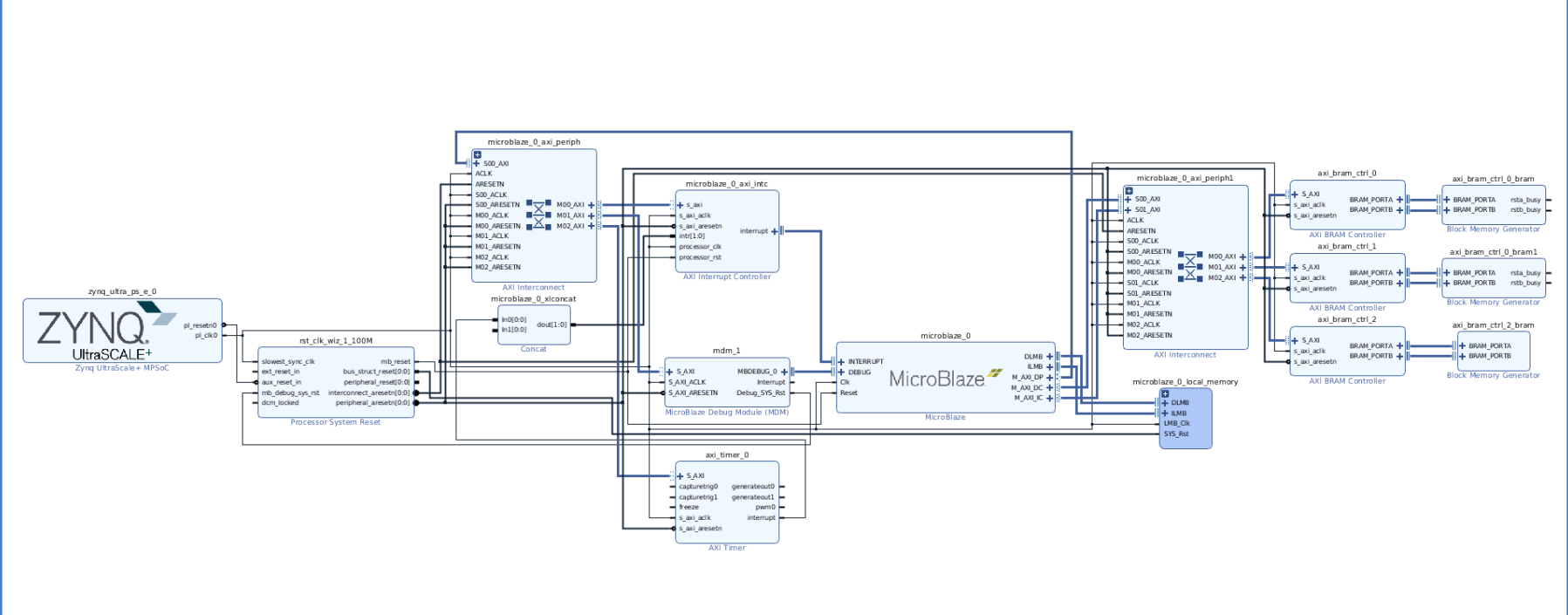

10)?完成之后,Vivado會基于之前的設置自動生成一些額外的IP,并且會自動連接完畢,此時不要點擊‘Run Connection Automation’;

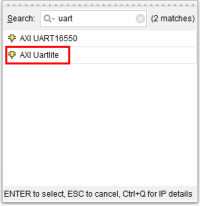

11)?在Diagram中添加AXI Uartlite IP,在搜索框輸入‘uart’,選擇相應的IP;

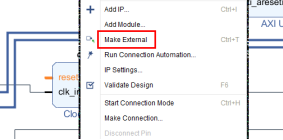

12)?鼠標右擊Clocking Wizard的‘reset’,選擇Make External添加引腳;

13)?使用連線工具將Processor System Reset的‘ext_reset_in’與‘reset’相連接。

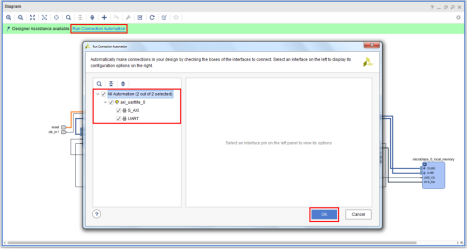

14)?完成后,點擊‘Run Connection Automation’,在彈出窗口中勾選所有端口,點擊OK繼續;

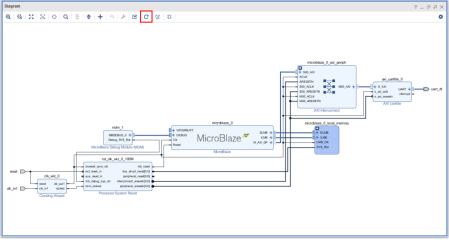

15)?完成后,點擊按鈕重新布局,完成后如下圖所示:

16)?點擊按鈕驗證設計是否正確

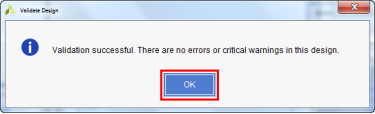

17)?驗證成功,設計與連線都正確,點擊OK,Ctrl+S保存設計。

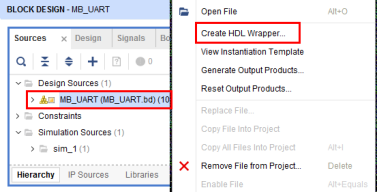

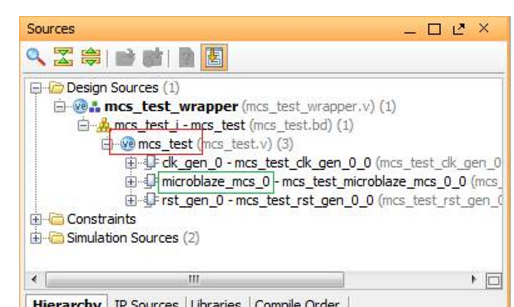

18)?在Sources窗格中鼠標右鍵‘MB_UART’,選擇‘Create HDL Wrapper’。

19)?使用默認選項,點擊OK繼續,完成HDL文件的創建。

20)?添加約束文件

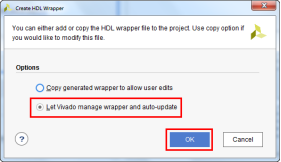

a)?在Flow Navigator中,展開PROJECT MANAGER,點擊‘Add Sources’。

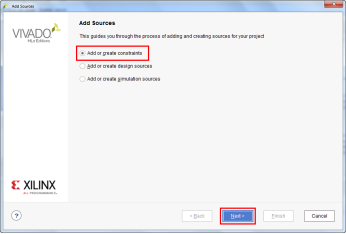

b)?選擇‘Add or create constraints’,點擊Next繼續。

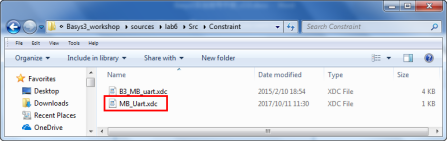

c)?選擇‘Add Files’,找到并添加‘MB_Uart.xdc’文件。注意,要勾選Copy constraints files into project

(文件路徑:Basys3_workshopsourceslab6SrcConstraint)

?

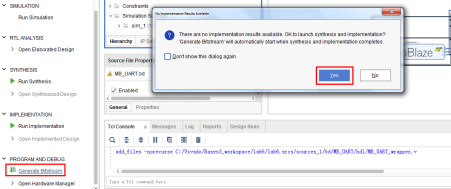

3.?綜合、實現、生成比特流文件

1)?在Flow Navigator中展開PROGRAM AND DEBUG,點擊Generate Bitstream。Vivado工具會提示沒有已經實現的結果,點擊‘Yes’,Vivado工具會依次執行綜合、實現和生成比特流文件。

二、基于Tcl腳本創建工程

1.?打開Vivado 2017.2

2. 在底部Tcl命令框使用‘cd’命令,進入MB_Uart.tcl文件所在路徑。參考路徑:C:Basys3_workshopsourceslab6SrcTcl,在Tcl命令框輸入:cd C:/Basys3_workshop/sources/lab6/Src/Tcl (注意:Vivado使用‘/’)

3. 在Tcl命令框中,輸入命令:source ./ MB_Uart.tcl。輸入完畢按回車,運行Tcl,等待Tcl進行創建、綜合、實現,最后生成比特流文件。

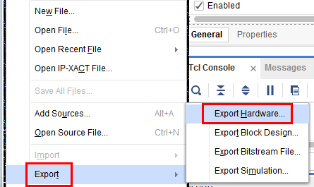

4.?建立SDK應用工程

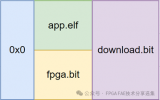

1)??在頂部工具欄中,選擇File>Export>Export Hardware導出硬件工程到Vivado SDK;

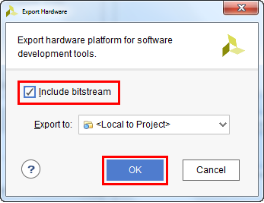

2)?在彈出窗口中勾選‘Include bitstream’,點擊OK繼續;

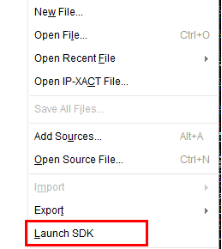

3)?在工具欄中,選擇File>Launch SDK,使用默認工程,啟動Vivado SDK;

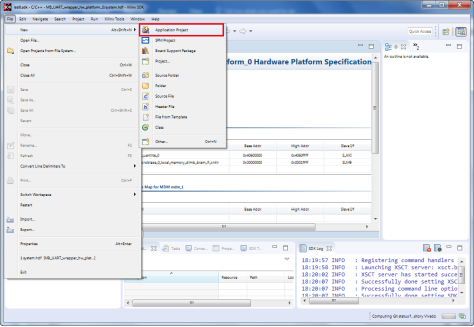

4)?在SDK上方工具欄中,選擇File>New>Application Project,新建一個SDK應用工程;

5)?工程取名為‘helloworld’,點擊Finish完成創建;

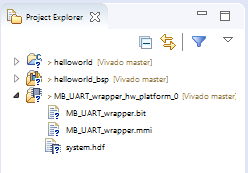

6)?可以看到 SDK 界面左側如下,新增加了helloworld和helloworld_bsp兩項。其中helloworld_bsp為helloworld應用工程的板級支持包:

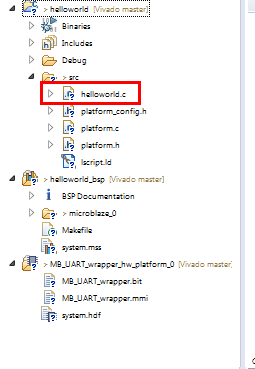

7)?雙擊helloworld下的src下的helloworld.c。這個文件為包含主函數的C語言文件,然后可以通過 CTRL+B 完成工程的 build;

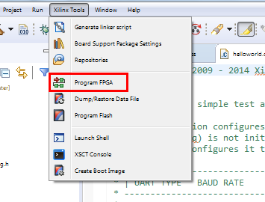

8)?連接Basys3開發板,打開電源,點擊SDK任務欄Xilinx Tools>Program FPGA;

9)?在彈出窗口中點擊Program完成比特流文件的下載:

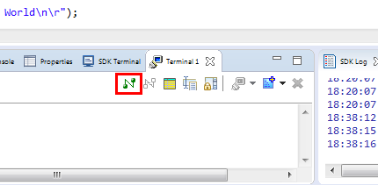

10)?連接Basys3的串口。選擇SDK界面下方的Terminal窗口,點擊下圖的連接按鈕:

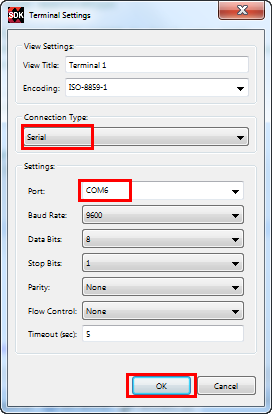

11)?在彈出窗口中,將Connection Type設置為Serial,在Port一欄選擇正確的串口,點擊OK完成串口配置并連接;

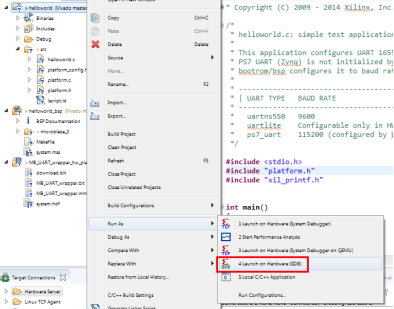

12)?在SDK界面左側Project Explorer中鼠標右擊helloworld,選Run As>Launch on Hardware(GDB),運行SDK軟件工程;

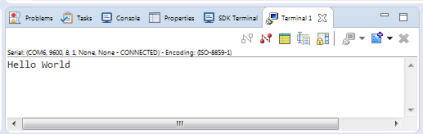

13)?稍等幾秒,可以看到Terminal界面出現了打印的‘Hello World’字樣。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論