現在來講soc的神經末梢,它們依附在骨架上,受和調控制,并將外部信息分享給核心以及其他成員。它是什么呢?

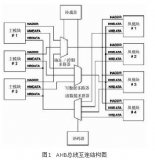

它就是我們所說的標準總線。soc上所有模塊想要被核心控制,都需要掛載到crossbar上,以便cpu下配置,以及cpu和dma進行數據傳輸。我們以最簡單的APB總線入手,來進一步了解標準總線的工作原理。

1、APB協議簡介

APB(Advanced Peripheral Bus) 作為高級外設總線是AMBA協議之一,也是最基本的總線協議。按照ARM官方定義,APB是一種低成本的接口協議,可以實現低功耗以及精簡的接口設計,降低接口設計的復雜度。

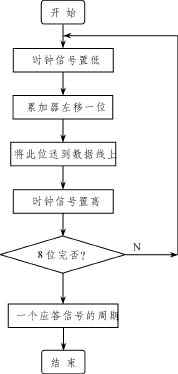

APB協議不支持流水線設計,它主要應用在低帶寬設計需求的接口中,高性能帶寬需求可以使用AXI總線。APB協議的實現與時鐘沿對齊,以簡化外設接口的設計。每次傳輸至少需要消耗兩個時鐘周期。

在SOC設計中,AHB一般作為IP的配置接口,包括低速IP如I2C,UART,I2S等,也包括DDR,PCIe,Ethernet等高速IP,可以方便的實現CPU對外設IP的寄存器配置。系統中一般會實現一個AXI2APB或者AHB2APB的轉換橋將APB口掛載在系統上。

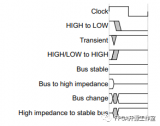

APB的傳輸信號只與時鐘上升沿有關,故其具備以下優點:

·易于實現高頻操作;

·性能與時鐘占空比無關;

·靜態時序分析簡單;

·易于與基于上升沿的寄存器訪問;

·易于集成到基于周期的仿真器中。

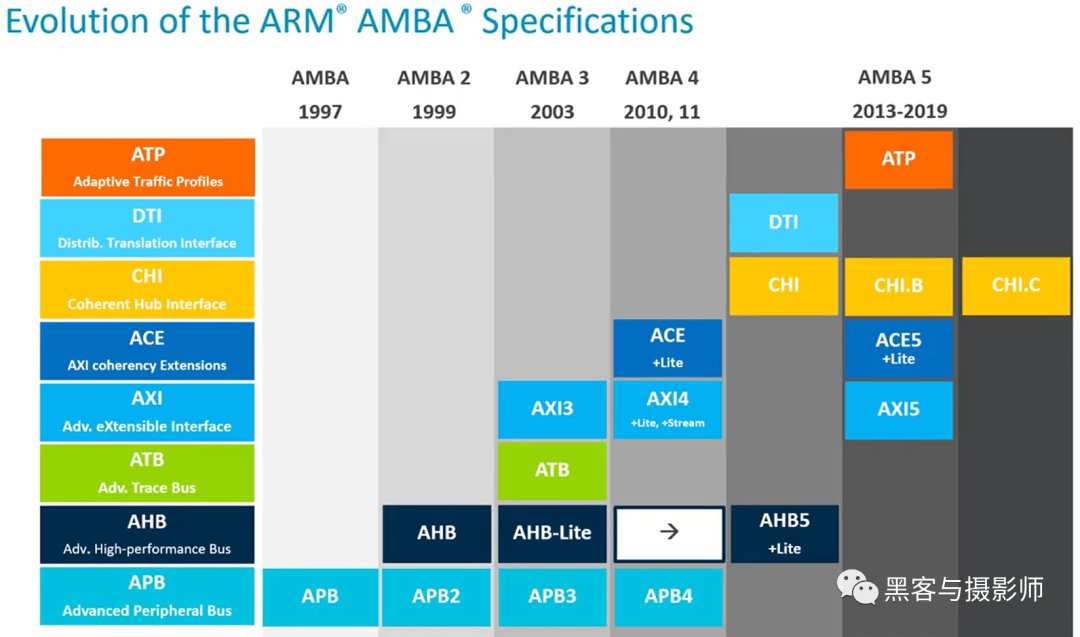

1.1、APB的發展史

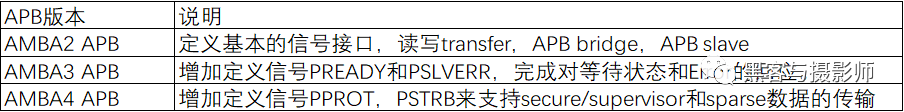

協議已經從APB2.0發展到現在的APB4.0。具體區別如下:

·APB2.0 :該版本協議定義基本的接口信號(具體可見端口信號章節,刪除APB3.0有的接口就行);

·APB3.0:增加信號PREADY用以指示slave準備好數據,增加信號PSLAVERR代表傳輸錯誤;

·APB4.0:增加信號PROT保護類型,增加信號PSTRB來支持byte級的訪問;

2.0和3.0的區別是什么?

APB2.0和APB3.0的差別:APB3.0提供了一個低功耗的接口,并降低了接口的復雜性。且APB3比APB2增加了兩個信號:

PREADY:來擴展APB傳輸,主要是增加延時;

錯誤信號PSLVERR:來指示傳輸失敗。

3.0和4.0的區別是什么?

·增加了PROT和PRSTB兩個信號。

·PPROT一種保護信號,用于支持APB上的非安全交易和安全交易。

·PSTRB一個寫選通信號,用于在寫數據總線上進行sparse data transfer(稀疏數據傳輸)。APB4用的比較少。

APB協議向下兼容。

目前soc上最常用的是APB2.0和APB3.0,下面我們主要介紹這兩個版本。

2、APB 2.0

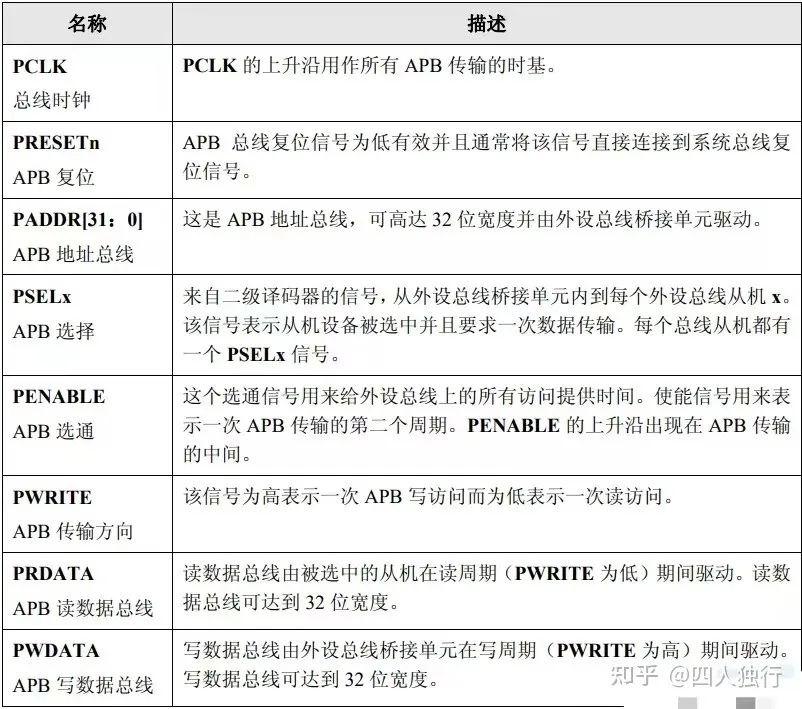

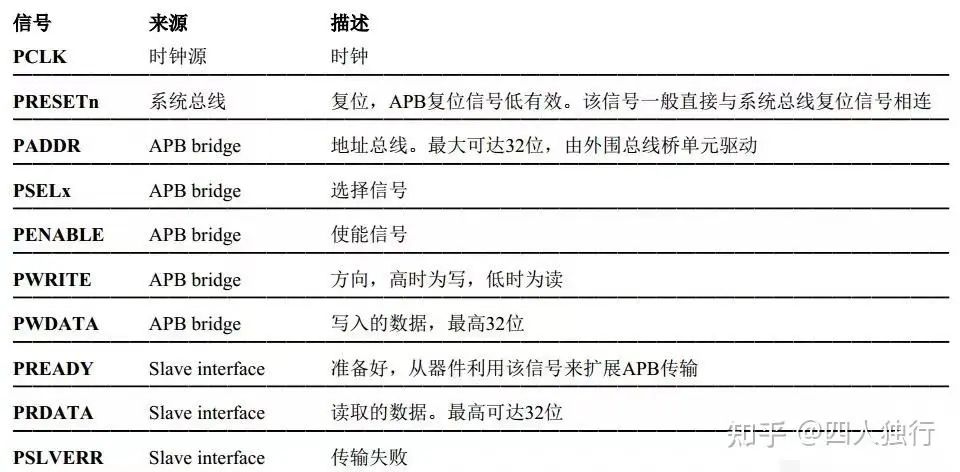

2.1、APB2.0信號列表

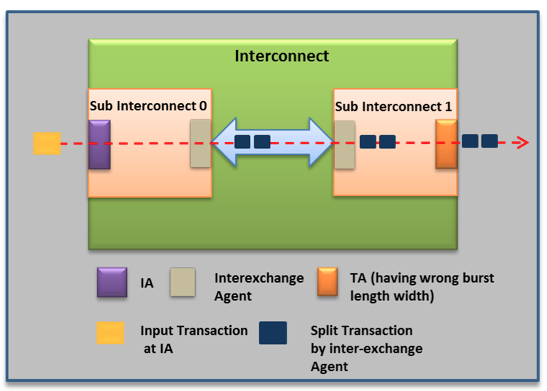

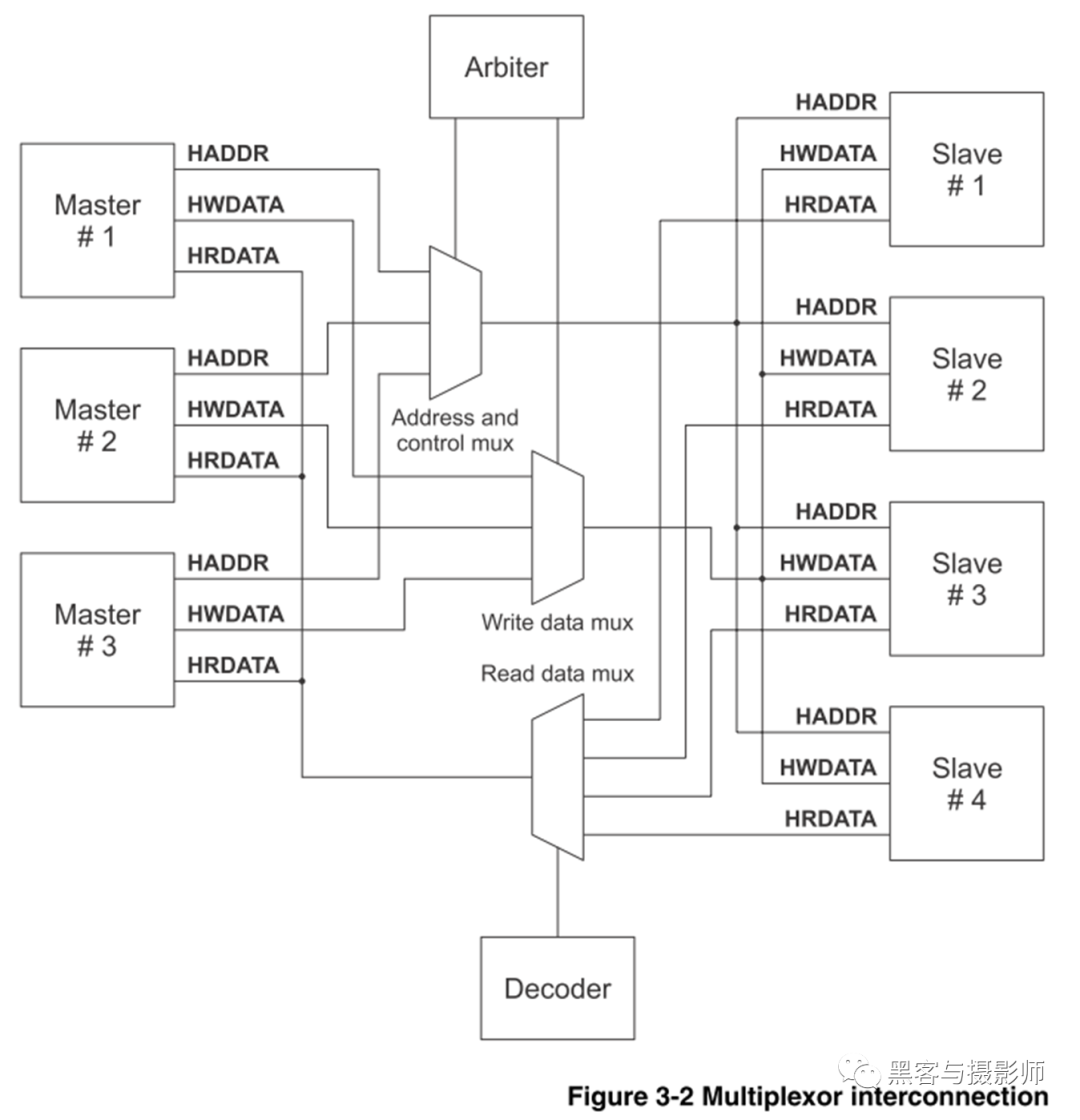

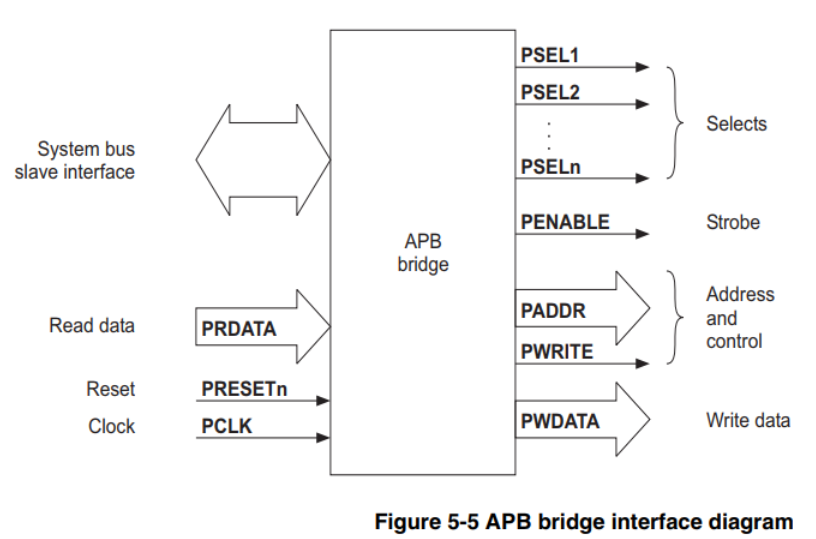

這里需要區分Master和Slave的區別,Master是主機,Slave是從機,一個總機下可以有n個從機,所有的數據傳輸都是master來控制的,slave來回應。這里需要用到APB 1TO多bridge,APB bif不需要仲裁,只需要對地址的decode,如果地址處于某個slave的域內,就拉高它的PSELn等控制信號,n為slave號。

APB2.0信號

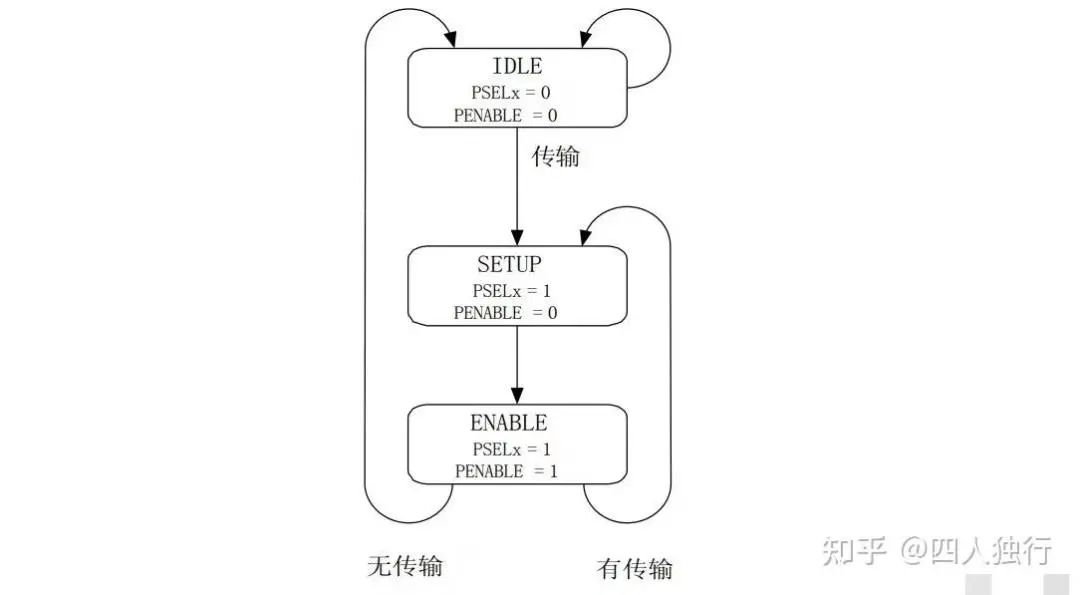

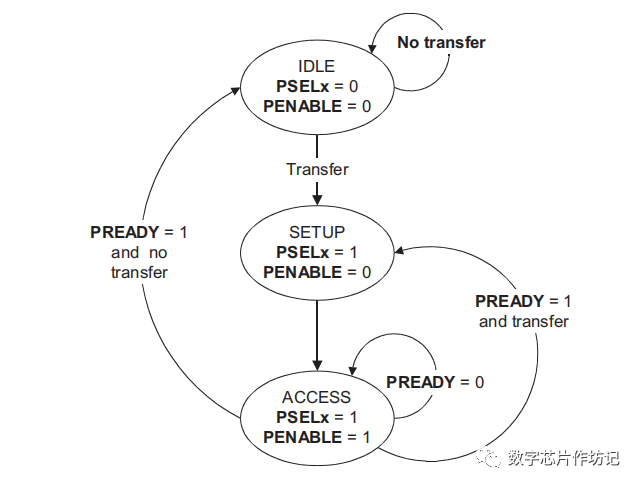

2.2 、狀態機

通過PSELx和PENABLE信號的變化,使APB總線處于下面3個狀態:

狀態機

·IDLE:PSELx和PENABLE都為0,表明master和slave之間無通信請求,因此處在該狀態。

·SETUP:當master和某一個slave之間準備進行數據傳輸時,會進入該狀態,這時PSELx=1,PENABLE=0。意思是master選中某一個slave告訴slave我準備要和你交換數據啦,請你準備好!這個狀態會保持一個時鐘周期然后進入ENABLE狀態。這個狀態可以直接給wdata。

·ENABLE:這個時候PENABLE拉高,master和某一slave進行數據傳輸,持續一個時鐘周期。這個狀態開始等待rdata。

在自己寫master時,就按照這個狀態輸出控制信號就可以了。

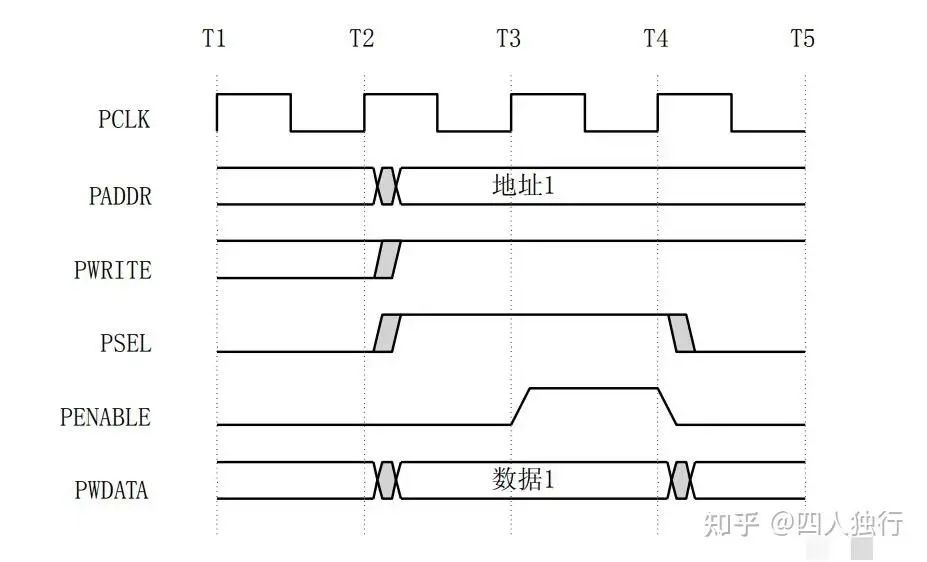

2.3 、寫操作

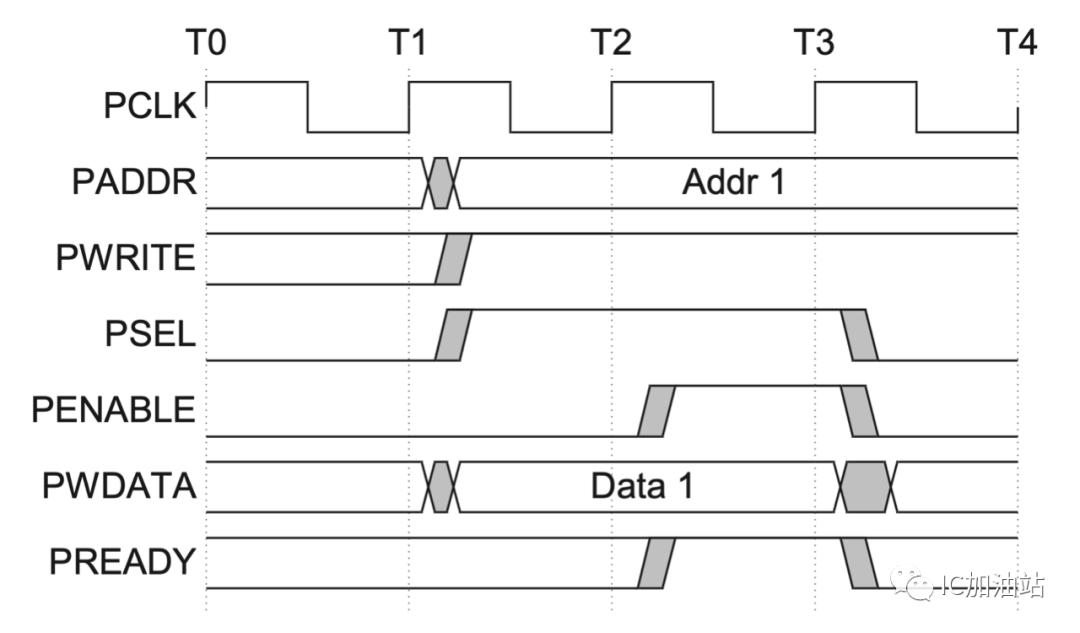

下面就是寫傳輸的時序圖:

寫時序

·T1~T2:這個階段master和某一slave無交互數據,因此處于IDLE狀態。

·T2:在該時刻,master準備將數據寫入某一slave中,因此進入SETUP狀態,同時把某一slave的PSEL信號拉高,PWRITE信號拉高,這表示master告訴某一slave:我即將要和你進行數據傳輸,是我把數據寫到你里面,請你準備好!同時改變PADDR和PWDATA信號,這是為了滿足下個上升沿的時序。

·T2~T3:保持一個時鐘周期。

·T3:此時將PENABLE信號拉高,真正將wdata寫到addr。

·T3~T4:保持一個時鐘周期。

·T4:數據傳輸結束,再次回到初始狀態。

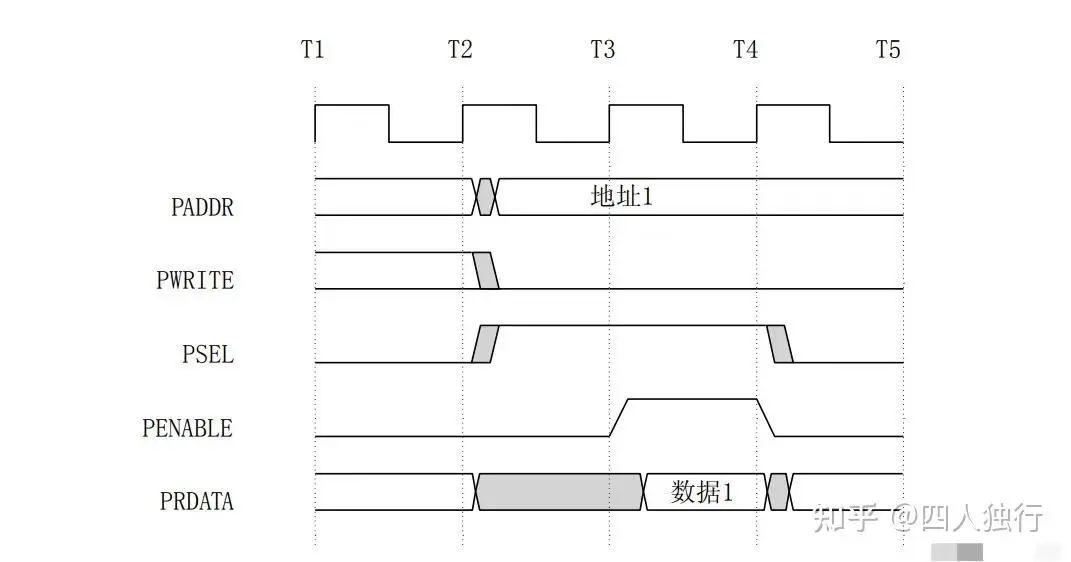

2.4、讀操作

讀時序

·T1~T2:這個階段master和某一slave無交互,因此處于IDLE狀態

·T2:在該時刻,master準備從某一slave中讀取數據,因此進入SETUP狀態,同時把某一slave的PSEL信號拉高,PWRITE信號拉低,這表示master告訴某一slave:我即將要和你進行數據傳輸,是我要讀你的數據,請你準備好!同時改變PADDR,這是為了滿足下個T4采樣沿的時序。

·T2~T3:保持一個時鐘周期。

·T3:此時將PENABLE信號拉高,表示master正式把某一slave之中的數據讀出來,注意,數據在ENABLE周期末尾的時鐘上升沿被采樣,也就是T4時刻。

·T3~T4:保持一個時鐘周期。

·T4:數據傳輸結束,再次回到初始狀態。

3、APB 3.0

APB 3.0協議是在APB 2.0協議的基礎上新加了2個信號,PREADY和PSLVERR組成的;PREADY信號是slave設備用來表示slave是否準備好的信號,PSLVERR是表示slave接收的數據是否有誤。

信號表

APB3.0信號

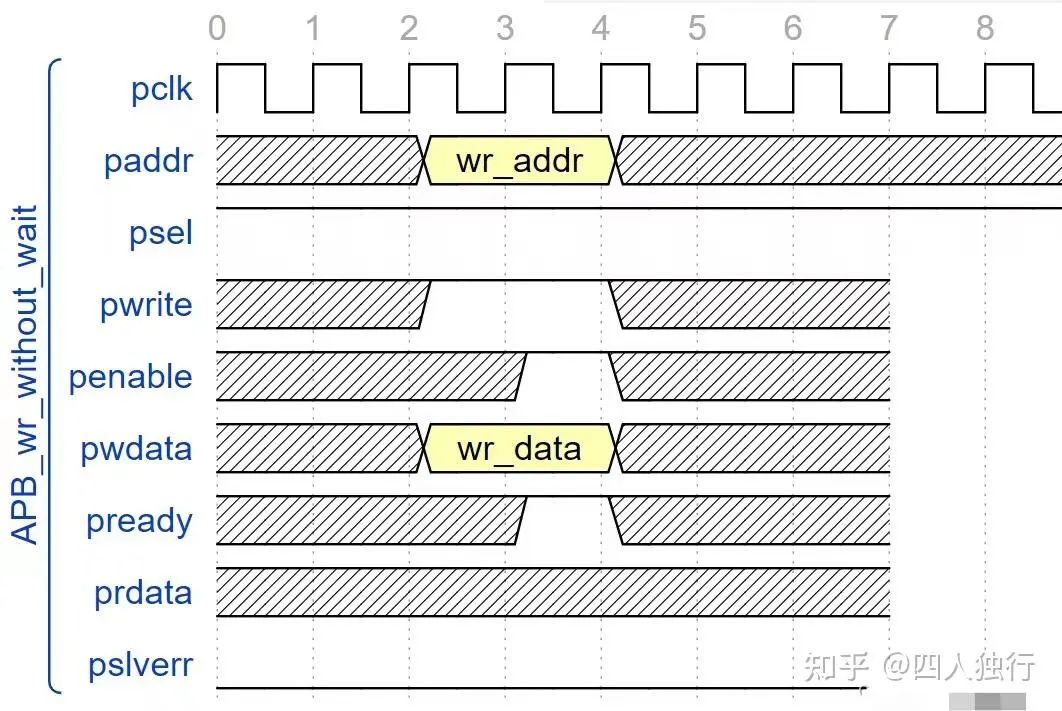

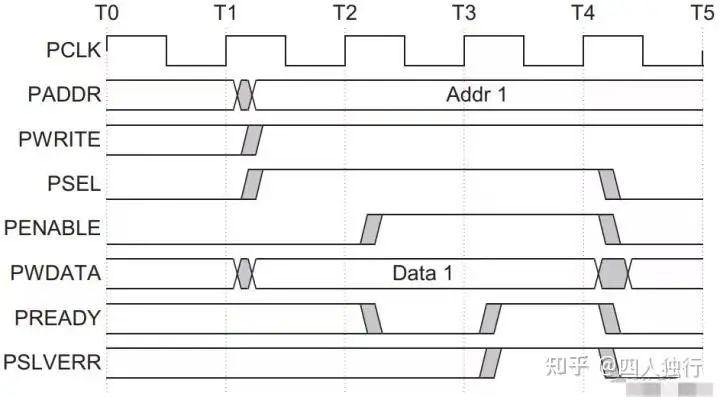

3.1、寫操作

寫操作,無等待

寫無等待時序

該種情況和APB2.0沒有任何區別,當PENABLE拉高后,會檢查PREADY是否拉高,如果拉高表示slave當前準備好了數據傳輸,則在上升沿3將數據寫給salve。

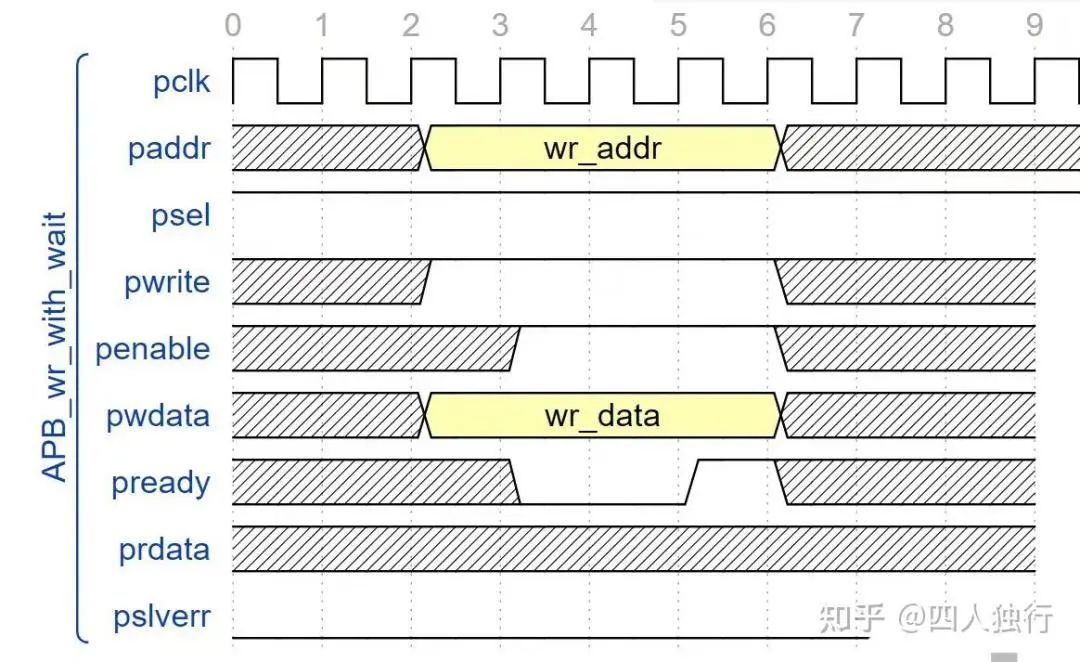

寫操作,有等待

寫有等待時序

如果PENABLE拉高后,發現PREADY沒有拉高,則表示slave還沒有準備好數據傳輸,這時所有信號保持不變直到PREADY拉高,在上升沿5將數據寫入。

3.2、讀操作

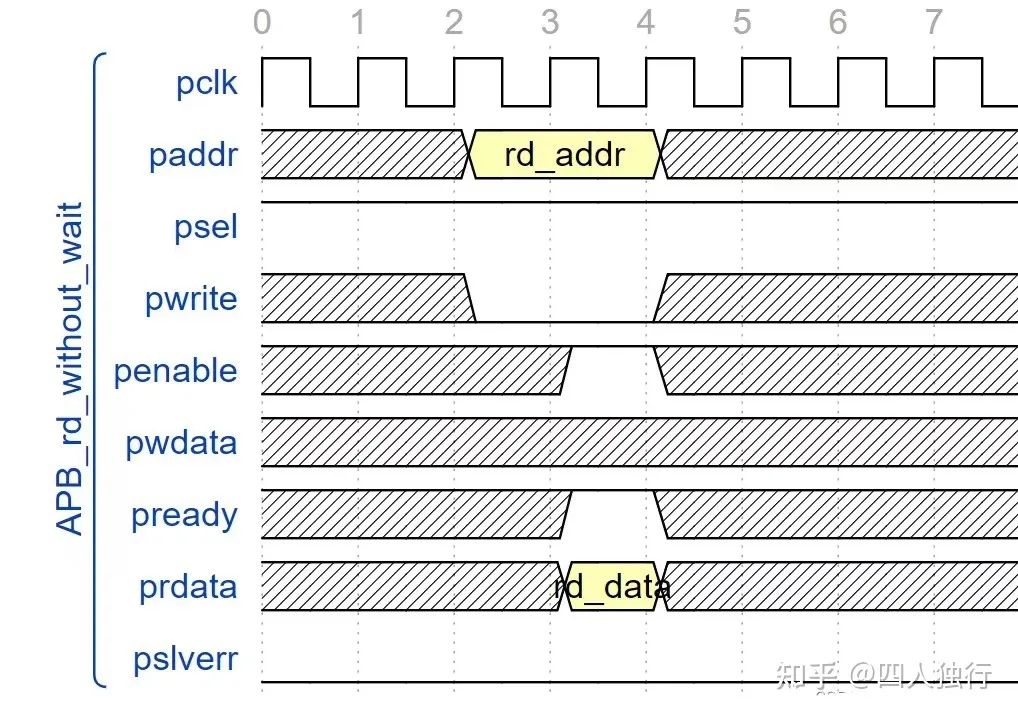

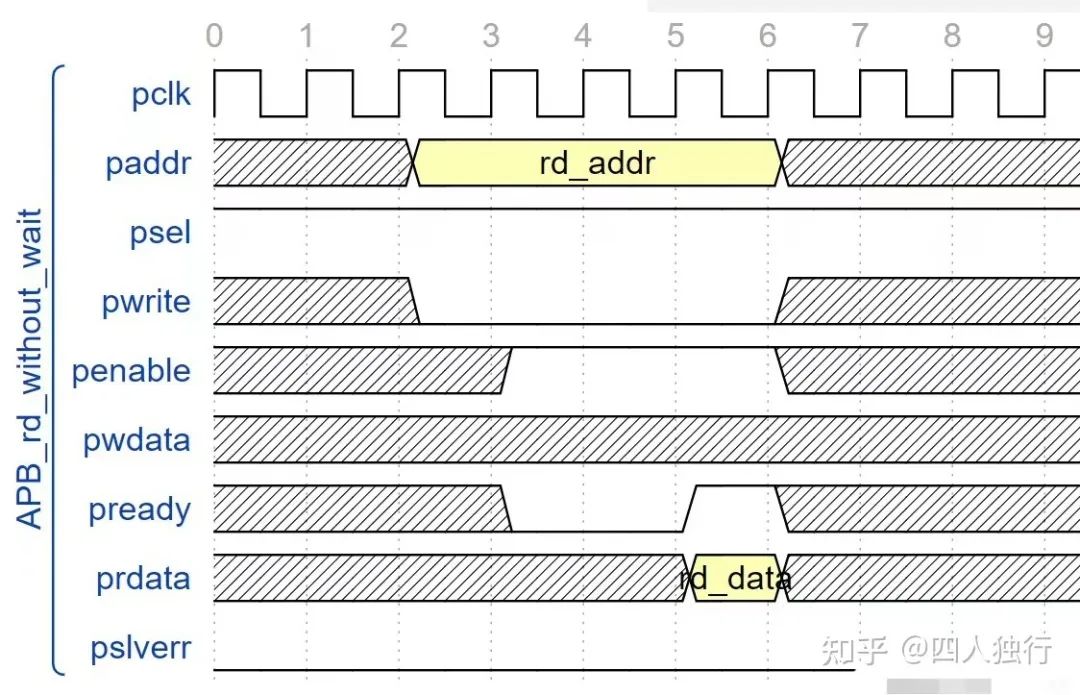

讀操作,無等待

讀無等待時序

該種情況和APB2.0沒有區別,與寫操作無等待類似,不再細說

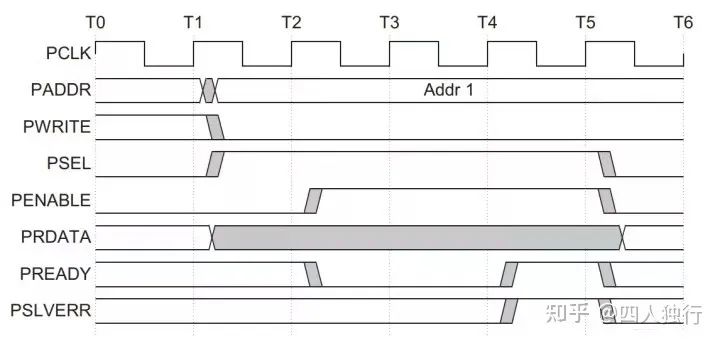

讀操作,有等待

讀有等待時序

當PENABLE拉高后,發現PREADY信號還沒有拉高,表示slave還沒有準備好,這時會等待直到PREADY信號拉高,在上升沿6時刻采樣數據

3.3、錯誤反饋

PSLVERR來指示APB傳輸上的錯誤情況。讀取和寫入事務都可能發生錯誤。當PSEL,PENABLE和PREADY均為高電平時,僅在APB傳輸的最后一個周期內才認為PSLVERR有效,其他時間不考慮PSLVERR。

寫操作

slverr寫時序

在前面的有等待的寫操作的基礎上,添加PSLVERR,也就是在T4時刻采樣,發現PSEL,PENABLE和PREADY均為高電平的前提下,PSLVERR為高,說明這次數據傳輸有錯誤。軟件決定后續行為。

讀操作

讀slverr時序

在前面的有等待的讀操作的基礎上,添加PSLVERR,也就是在T5時刻采樣,發現PSEL,PENABLE和PREADY均為高電平的前提下,PSLVERR為高,說明這次數據傳輸有錯誤。軟件決定后續行為。

4、APB應用場景。

APB因為其面積小,接口少,經常用在外設上,為什么呢?

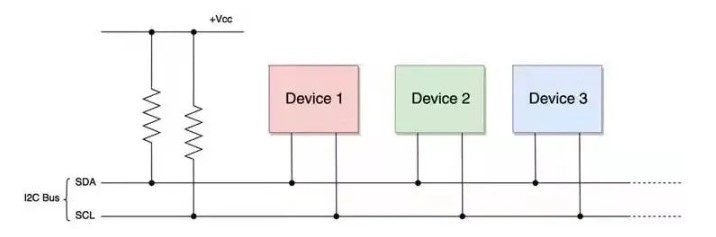

因為soc上外設很多,包括spi,i2c,uart,timer,wdt等,他們對時鐘要求不高,如果使用APB接口,可以省面積,降低芯片的復雜度。這也是為什么外設優先的標準接口是APB。

這里主要講一些APB在SOC上的特殊用法。

·某些IP預留用戶控制信號,我們需要用寄存器控制此信號,一般soc每個子系統都會有一個模塊專門做這個事情,這是就可以選擇APB接口用來配置這些寄存器。

·某些IP,例如SRIO,serdes預留用戶配置接口,synosys叫做cr配置口,用于配置或者debug。這時候我們可以自己寫一個APB2CR的橋。

·核間通訊模塊。通過寫寄存器產生中斷輸出,這時候可以使用APB接口,因為中斷發生次數少,無性能要求,可以使用APB,簡單。

·APB轉sram接口或者APB轉fifo。某些模塊對外接口是sram,需要我們使用轉接橋,根據性能我們選擇使用合適的AMBA總線;自研模塊數據緩存時,涉及到異步處理,這時候可能用到APB轉FIFO的設計。

但是他也有局限,帶寬低且不支持pipeline,所以module有這些要求不要使用APB。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論