基于嵌入式網絡的遠程數據采集系統具有不受地理環境、氣候、時間的影響,小型便攜,使用靈活方便,交互操作性好,傳輸速率高,可靠性高,功耗低和移動性好等優點。目前常用的嵌入式CPU中,ARM由于性價比在同類產品中比較突出,目前用得越來越多,尤其是結合開源的嵌入式Linux操作系統以后,更是得到越來越多設計者的青睞。LabVIW作為一種功能強大,簡單易用和設計靈活的圖形化編程語言,已經廣泛地被工業界、學術界和研究實驗室所接受,越來越多地應用在虛擬儀器、測試測量、數據分析、信號處理以及遠程控制中。本設計中,遠程數據采集系統采用基于ARM和嵌入式Linux的方案來實現。采用高性能的ARM嵌入式微處理器Samsung S3C2440作為系統的核心,結合數據采集、下變頻、存儲模塊,實現了數據高速實時采集。同時,利用處理器外部配備的以太網控制器CS8900完成與主機上運行的LabVIEW服務器通信,實現數據的傳輸與系統的遠程控制。

1 系統整體結構

采用SamsungS3C2440作為前端數據采集系統的核心控制器件。系統的整體設計任務分為信號采集與下變頻、數據存儲與傳輸、信號顯示與處理分析等。整體設計方案構架見圖1。信號采集部分采用ADI公司的AD9244完成,AD9244是一款14 bit,40/65 MSPS的高性能ADC。為了滿足AD9244差分輸入的要求,在信號的輸入端配合了AD8138低失真單端轉差分ADC驅動芯片。信號采集完成后,送至ADC6620正交數字下變頻器(Digital Down Conversion,DDC)處理,經過抽取和濾波后的I,Q兩路正交信號在其輸出的數據有效以及I/Q指示信號的配合下,由FPGA產生靜態隨機存取存儲器(static Random Access Memory,SRAM)存儲時序并存儲至64 K×16 bit的SRAM中。

在FPGA中主要完成SRAM讀寫時序產生、SRAM讀寫地址生成、數據通道選擇等工作,FPGA中的邏輯在一個16 bit的控制字寄存器的控制下有序地工作。當SRAM中存儲一定量的數據后產生中斷信號,提示ARM將數據取走。為了提高系統的速度,ARM采用直接數據存儲(Direct Memory Address,DMA)方式讀取數據。之后運行在ARM上的客戶端程序將數據通過網絡發送給遠程主機。遠程主機上的LabVIEW服務器程序對收到的數據進行顯示、頻譜分析、存儲回放等處理,同時遠程主機的控制信號以及為下變頻器ADC6620設計的濾波器文件也可以通過網絡發送給客戶端,實現遠程控制。

2 現場數據采集系統的硬件設計

2.1 ADC設計

外部模擬信號從SMA(Sub Miniature-A)接口輸入,隔離直流后進入AD8138 ADC驅動芯片,AD8138將單路輸入信號變成兩路差分信號,送至AD9244轉換。AD9244中幾個重要引腳的含義及接法:

a)CML(Common Mode Reference):串聯一個0.1μF的電容后接地。

b)DCS(Duty Cycle Stabilizer):接+5 V電源時表示轉換時鐘為50%占空比,接地表示轉換時鐘的上升沿與下降沿均由外界控制。本設計中DCS接+5 V電源。

c)SENSE(Internal Reference Control):接地時將輸入信號峰峰值的范圍限制為1 V,接VREF時將輸入信號峰峰值的范圍限制為2 V。本設計中SENSE接VREF。

d)DFS(Data Format Select):接+5 V電源時輸出數據格式為補碼,接地時為直接二進制碼輸出。由于ADC6620將其輸入數據解釋成補碼,本設計中DFS接+5 V電源。

2.2 ADC6620設計

AD6620的任務是將高速數據流變成當前可實時處理的中低速數據流。在本設計中,AD6620數據輸入端代表指數含義的3位(EXP0~EXP2)接地,且工作在單輸入通道模式下(A/B=3.3 V),以模式0接收來自于ARM的配置信息(MODE=GND),采用并行方式輸出數據(PAR/SER=3.3 V)。

2.3 其它設計

本設計所采用的ARM開發板是由廣州友善之臂公司所生產的QQ2440V3,其上有一個44針的系統總線接口,它與FPGA連接起來完成數據與控制信息的傳輸。FPGA與SRAM的設計比較簡單,這里不再贅述。

3 數據采集系統的軟件設計

為完成系統任務,需要實現幾個方面的軟件設計:

a)正交數字下變頻器AD6620濾波器以及控制寄存器設計。

b)在FPGA上實現系統控制、SRAM讀寫地址生成、數據通道選擇等功能的Verilog HDL程序。

c)ARM上基于嵌入式Linux操作系統的數據采集硬件驅動程序。

d)ARM上客戶端應用程序。

e)遠程主機上基于LabVIEW的服務器以及顯示、頻譜分析、存儲與回放程序。

3.1 AD6620濾波器及控制寄存器設計

AD公司專門針對AD6620芯片推出了濾波器設計軟件fltrdsn以及監視控制軟件AD6620,但該軟件是基于計算機并口與AD6620芯片連接的,不適應設計中遠程數據傳輸與控制、多客戶端的任務要求。可以利用該軟件將設計成功的濾波器以及配置文件保存下來,利用LabVIEW的文件處理功能自動將信息提取出來,通過網絡遠程配置AD6620。

3.2 FPGA邏輯設計

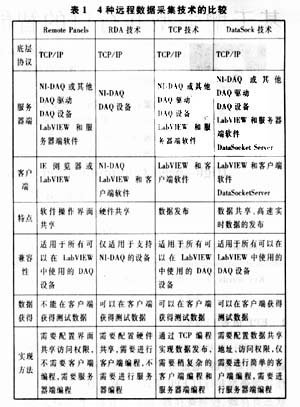

FPGA內部邏輯電路結構見圖2。考慮到后續設計的需要,FPGA內部使用ARM地址總線的低3位來選擇當前操作的模塊,具體的地址與內部模塊對應關系見表1。

圖2中各模塊功能進一步說明如下:

a)Input_db_part:雙向數據總線分離。配合由Control_register送來的控制信號,在Conf_6620有效時將數據總線上的數據送至Config_6620模塊,完成AD6620配置,在Fetch_sram信號有效時將讀SRAM得到的數據傳送至ARM數據總線。

b)Control_register:控制寄存器。內部模塊有序工作的核心,具體的控制定義見表2。

c)Config_6620:配置AD6620。此模塊在Conf 6620位有效時接收由ARM傳來的AD6620配置信息,完成DDC濾波器和控制寄存器配置。它除了本身使用ARM地址總線的3位ARM ADD[3:1]作為FPGA內部模塊選擇之外,還用了ARM ADD[6:4]作為AD6620的外部接口寄存器地址。Rdy in信號用于指示寫入操作成功,ARM檢測到此信號有效后,進行下一次的寫操作。

d)PII:鎖相環。Cyclone EP1C6Q240中有2個鎖相環模塊,設計中使用了其中的一個將20 MHz的時鐘倍頻至50 MHz,供AD9244,AD6620以及FPGA內部使用。

e)Ad_to_sram:AD6620輸出數據寫入SRAM時序產生模塊。AD6620工作在單通道模式時典型輸出時序見圖。

此模塊主要完成的功能有:用2個數據鎖存器在DV與IQ信號的控制下鎖存I路和Q路數據,產生寫SRAM所需的地址。由于AD6620抽取率較高的緣故,輸出數據率一般較低,在模塊中使用了狀態機在2次有效數據期間產生寫SRAM的時序。此外,當寫地址到達設定值時,模塊產生寫溢出中斷,提示ARM改變控制寄存器內容,讀取數據。

a)Read_add_gen:讀地址產生。在Fetch_sram位的控制下,產生讀SRAM時的地址,當讀地址到達設定值時,產生讀溢出中斷,提示ARM改變控制寄存器內容,進行下一步操作。

b)Control_logic:控制邏輯。模塊在Start_daq有效時選擇由Ad_to_sram模塊產生的寫SRAM的地址、數據與控制總線與SRAM相接,而在Fetch_sram有效時選擇讀SRAM的地址、數據與控制總線與SRAM相接。與DMA讀取有關的請求與響應信號也在此模塊中處理。

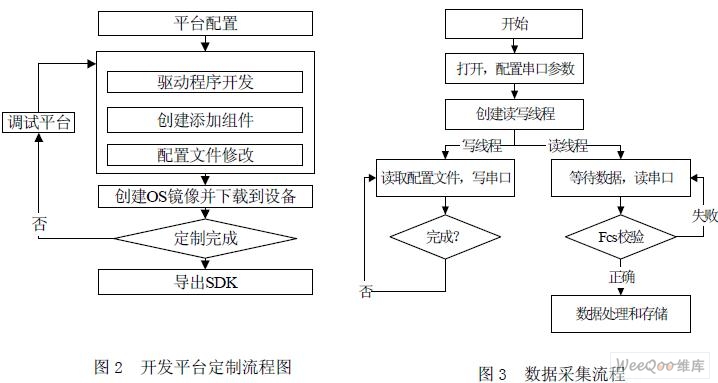

3.3 嵌入式Linux驅動程序設計

驅動程序是硬件與應用程序的接口。針對設計任務與硬件特點,在驅動程序中設計了以下函數:

a) AD6620_read:申請DMA緩存,睡眠等待寫溢出中斷到來,DMA傳輸完成后,將數據從內核空間傳送至用戶空間,釋放DMA緩存。

b) AD6620_ioctl:核心是一個switch選擇結構,根據應用程序中用戶命令,完成初始化DMA,寫控制寄存器或者配置AD6620的工作。

c)AD6620 open:主要完成DMA通道參數設置,初始化IO端口和信號量。

d) AD6620 release:完成與AD6620_open相反的工作,主要是一些清理和釋放申請資源的工作。

函數編寫好后,通過下面的file_operations結構體聯系起來:

e) AD6620 init:初始化函數,完成驅動程序注冊、中斷與中斷處理函數注冊、創建設備文件節點等。其中的驅動程序注冊的核心就是上面的file_operations結構體。

驅動程序編寫好后,用戶就可以在應用程序中調用這些函數,實現通過一組標準化的調用來操作底層硬件。

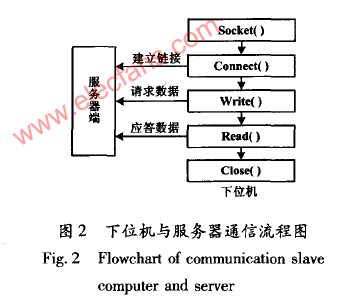

3.4 客戶端應用程序

客戶端應用程序為了保證數據與控制信息的可靠傳輸,采用的是基于TCP協議的Socket網絡編程。本次設計客戶端運行在ARM上,采用的是Linux下的C編程;而服務器端運行在遠程主機上,利用LabVIEW的圖形化語言實現。具體客戶端的通信與控制流程圖見圖4。可以看出。客戶端是依賴于讀取由遠程主機發送的控制字符來完成實時控制,實現與服務器端的交互操作的。因此,無論是客戶端還是服務器端,在每一次發送數據與控制信息時,都會發送一個控制字符,接收端就是依靠識別此字符來完成相應的操作。表3中給出了控制字符與所執行操作之間的對應關系。

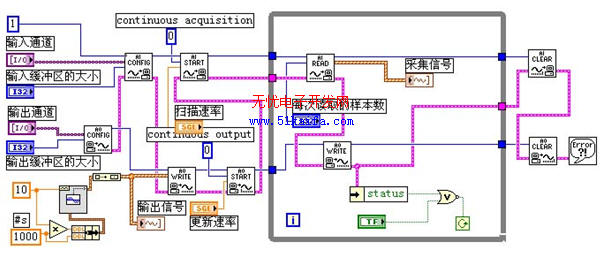

3.5 LabVIEW服務器程序設計

服務器端的完整程序見圖5。服務器在指定的端口上偵聽,等待遠程客戶端的連接。程序的核心是兩個循環框,上面的循環框完成發送數據和控制信息的任務,主要包括傳送AD6620濾波器設計與控制寄存器配置文件、實時改變AD6620可動態配置寄存器內容、開始數據采集以及停止系統控制等模塊。

數據與控制信息內容放在LabVIEW事件框圖中,當用戶單擊前面板上的控制按鈕時,相應的信息被發送,這樣就避免了系統無休止地查詢,節約了系統資源。下面的循環框完成讀SRAM數據接收、分離IQ信號、頻譜分析與顯示等,當用戶使得存儲文件路徑不為空時,可以將此時數據顯示控件上的數據保存下來;而當回放文件路徑不為空時,用戶可以回放之前保存的歷史數據。頻譜顯示控件有線性與對數顯示兩種格式,它受前面板上的一個系統復選框的控制。

4 設計結果驗證

采用了3組實驗來驗證設計的正確性。實驗條件:現場數據采集系統IP地址192.168.1.230,遠程主機IP地址192.168.1.1,二者位于同一個局域網內。系統工作主頻50 MHz,AD6620濾波器為低通濾波器,通帶截止頻率10 kHz,阻帶截止頻率15 kHz,通帶內衰減0 dB,阻帶衰減-60 dB,三級濾波器的抽取系數分別為10,25,2。

第1組實驗的輸入信號為單頻信號,頻率1.005 MHz,幅度250 mV,AD6620中NCO頻率字設定為1 MHz。實驗恢復的I路信號及其頻譜分析見圖6(a)。從實驗結果來看,系統采集數據頻率準確,較好地恢復了信號。第2組實驗的輸入信號為調幅信號,載波頻率1 MHz,幅度250 mV,單音調制信號頻率為3 kHz,調制深度30%。AD6620中NCO頻率字設定為1 MHz。實驗恢復的信號與頻譜分析見圖6(b)。這時從頻譜圖上可以清晰地看出差頻之后,在零頻周圍300 Hz處有1根清晰的譜線。第3組實驗的輸入信號為單頻信號,頻率1.018 MHz,幅度250 mV,AD6620中NCO頻率字設定為1 MHz。實驗恢復的I路信號與頻譜分析見圖6(c)。此時由于信號處于濾波器通帶之外,衰減很大,不能恢復信號。I路信號顯示圖中類似于“毛刺”的信號是由于電路底噪聲在AD6620中運算所產生。綜合3組實驗的結果,本次設計較好地完成了設計任務。

5 結論

數據采集與網絡遠程傳輸系統是一個高集成,特別講究軟硬件間相互配合的綜合系統,強調的是協調、穩定、高速、精準地完成各項數據采樣工作。本設計中,在合理設計硬件的基礎上,分別對FPGA,ARM以及遠程主機上的服務器程序精心設計,解決了以往系統在大量數據采集、傳輸、儲存、讀寫和處理時的速度以及靈活性問題。利用LabVIEW功能強大、簡單易用,設計靈活的圖形化編程語言,很容易地實現了對遠程數據采集終端的配置與控制。

電子發燒友App

電子發燒友App

評論