為了正確理解時鐘相關器件的抖動指標規格,同時選擇抖動性能適合系統應用的時鐘解決方案,本文詳細介紹了如何理解兩種類型時鐘驅動器的抖動參數,以及從鎖相環輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 14342

14342

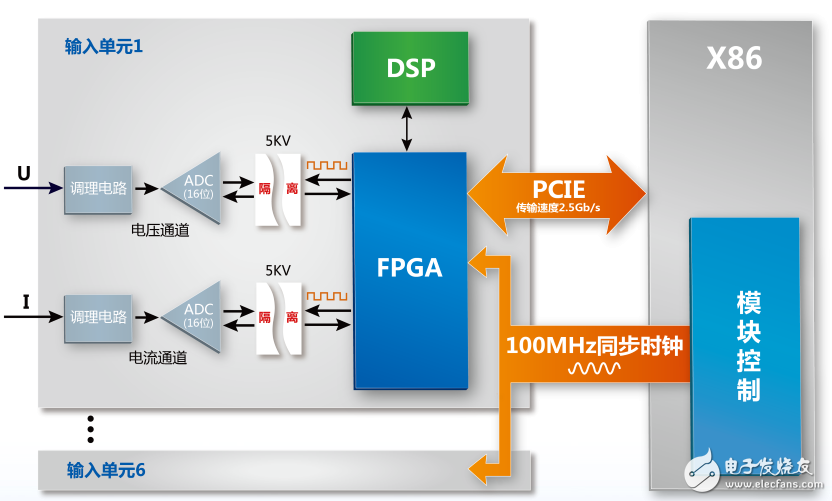

我們在使用示波器的時候,要想穩定的顯示波形,我們往往需要選擇一個合適的觸發方式。而在功率測量領域,如何實現“電壓”和“電流”的同步測量至關總要,今天我們就來揭秘周立功致遠電子是如何來實現功率測量的“神同步”!

2015-07-22 16:30:56 3013

3013

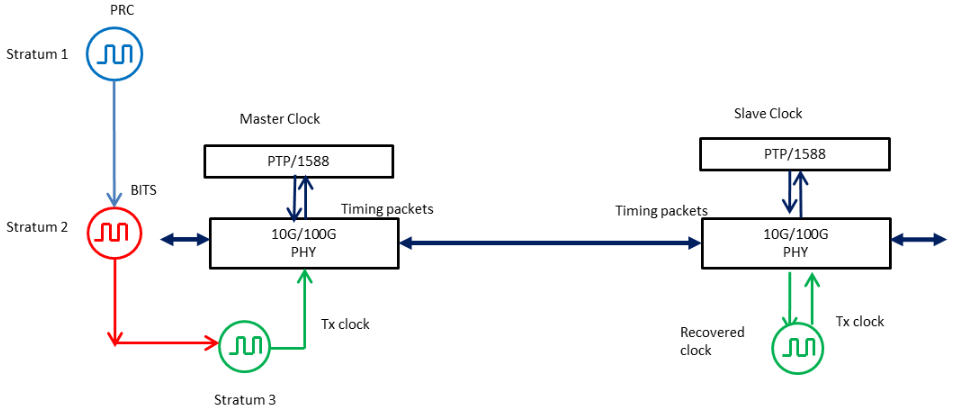

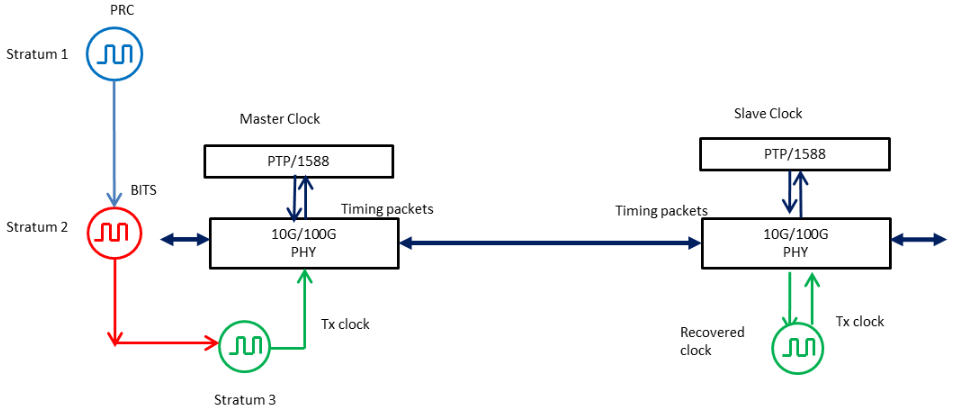

同步以太網是一種采用以太網鏈路碼流恢復時鐘的技術, 簡稱SyncE。同步以太網通過從串行數據碼流中恢復出發送端的時鐘,從而實現網絡時鐘同步。但SyncE不能提供時間同步。

2020-05-12 09:24:02 1945

1945

學習STM32的同學知道,STM32有好多時鐘,如32.768Khz,8Mhz,被時鐘樹搞迷糊了,下面一一解析。HSE:高速外部時鐘信號(4--16Mhz常用的為8Mhz)HSI:高速內部時鐘信號

2017-04-27 16:34:26

其他時間源。同步時鐘服務器能夠精確測量到不同設備的時間偏差,并能夠自動校準時間,使得整個網絡中的時間保持同步。這種設備不僅在通信和計算機領域得到廣泛應用,而且在現代工業生產、安防監控等領域也大受歡迎

2023-04-14 13:36:20

請教各位,同步源和PLL源有什么異同,它們的作用是什么?

2021-04-29 06:16:23

同步源和PLL源有什么異同?作用是什么?

2021-05-07 06:17:21

工作。唯有通過參考時鐘來同步這樣的“對表操作”,才能讓它們步調一致,從而緊密連接形成網絡。

對于參考時鐘,它首先要確定一個參考源,然后再是不同節點之間的同步關系。在通信系統中,一般來說精度較低的節點

2023-05-10 17:09:50

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數據通信、有線及無線基礎設施以及其它高速應用等高級系統中,時鐘抖動是整體系統性能的關鍵因素。要

2018-09-13 14:38:43

利用9401測量頻率,采用“隱式測量”,可以測量,但是采樣率與信號頻率一致。現在希望可以自己設定采樣率,所以必須要設置成“采樣時鐘”但是設置成采樣時鐘后,必須要提供“外部時鐘”(測量頻率必須要提供

2017-04-12 23:48:44

,這個選通信號也可以稱為源同步時鐘信號。源同步時鐘系統中,數據和源同步時鐘信號是同步傳輸的,我們保證這兩個信號的飛行時間完全一致,這樣只要在發送端的時序是正確的,那么在接收端也能得到完全正確的時序。整個

2014-12-30 13:54:22

處于正常工作的狀態)。比如51單片機使用典型的12MHz晶振作為時鐘源,則外設如IO口、定時器、串口等設備的驅動時鐘速率便已經是固定的,用戶無法將此時鐘速率更改,除非更換晶振。解析STM32的時鐘樹[hide][/hide]

2011-10-21 14:36:05

您好:ADRF6602的參考時鐘源能給我一個推薦型號或是哪個公司的嗎?我找了好久都沒找到峰峰值1V,最大功率13DBM的晶振。

2019-03-08 09:05:31

)。我還使用V5中的PLL_base而不是DCM_base進行了一些測試。這比我的DCM產生更多的位錯誤。但在我的PLL設計中,我使用了源同步(我不知道為什么,一位同事把它放在我的代碼中,我不知道他

2020-06-15 15:27:25

摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

我正在使用帶有兩個內部源和組合器的N5241A PNA-X進行IMDx測量;端口1是輸入,端口2是輸出。我在DUT輸出端測量相對于載波的IM3,在音調功率對話框中輸出音調功率設置為-5dBm;我還將

2018-12-13 16:54:52

RTC是什么?RTC工作過程是怎樣的?RTC的時鐘源來源有哪些?如何選擇RTC的時鐘源?

2021-09-29 09:18:39

STM32中定時器的時鐘源是什么?

2021-11-24 06:22:09

一、在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE、PLL。①HSI是高速內部時鐘,RC振蕩器,頻率為8MHz。②HSE是高速外部時鐘,可接石英/陶瓷諧振器,或者接外部時鐘源,頻率范圍為4MHz~16MHz。③LSI是低速內部時鐘,RC振蕩器,頻率...

2021-08-13 07:24:19

:時鐘頻率速度,英語:clock rate),是指同步電路中時鐘的基礎頻率,它以“若干次周期每秒”來度量,量度單位采用SI單位赫茲(Hz)。它是評定CPU性能的重要指標。一般來說主頻數字值越大越好...

2021-08-18 07:21:56

用時鐘源來產生時鐘!在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE、PLL。①、HSI是高速內部時鐘,RC振蕩器,頻率為8MHz。②、HSE是高速外部時鐘,可接石英/陶瓷諧振器,或者

2021-08-19 06:49:53

在學習STM32的過程中,一個需要我們理解的知識點就是時鐘STM32的時鐘源有4個:HSL :內部高速時鐘源HSE:外部高速時鐘LSl:低速內部時鐘LSE:低速外部時鐘STM32輸入時鐘源1.1

2021-08-19 07:06:25

一、綜述:1、時鐘源在 STM32 中,一共有 5 個時鐘源,分別是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。 ①HSI 是高速內部時鐘, RC 振蕩器,頻率為 8MHz

2021-08-23 06:24:59

在看u***,書上說u***數據包的同步域可以同步主機端和從機端的時鐘,這個怎么理解u***接口沒有時鐘線,我又想到了單片機串口的波特率,不知道有沒有關系,向大家請教了這個簡單的問題,很想知道答案

2019-07-02 18:06:13

就是時鐘同步,計數器輸出脈沖和數字I/O口接受脈沖數據同時進行,如何將計數器通道的時鐘作為數字通道的時鐘源啊?同時數字通道中還有觸發,觸發的時鐘源也是計數器的時鐘 如圖中所示,這是別人做的,但是我

2015-01-14 11:26:01

對stm32時鐘源的進一步理解stm32中五個時鐘源的介紹HSI 是高速內部時鐘,RC 振蕩器,頻率為 8MHz。HSE 是高速外部時鐘,可接石英/陶瓷諧振器,或者接外部時鐘源,頻率范圍為4MHz

2021-08-18 07:45:18

stm32時鐘源1.HSI high speed internal,即高速內部時鐘,時鐘頻率約為8Mhz,因為是由RC振蕩器產生,所以不穩定。2.HSE High Speed External

2021-08-20 08:07:15

stm32可選的時鐘源在STM32中,可以用內部時鐘,也可以用外部時鐘,在要求進度高的應用場合最好用外部晶體震蕩器,內部時鐘存在一定的精度誤差。準確的來說有4個時鐘源可以選分別是HSI、LSI

2021-08-18 07:32:05

源同步輸入的1080P視頻信號,148.5M時鐘,從fifo寫入端輸入。讀出端時鐘采用50M主時鐘經2級DCM產生148.5M的時鐘clkfx。然后輸出到pad給下級器件。請問此方案是否合理?疑問是輸出時序如何確定?調整?器件選用spartan3 1400a。希望***下

2015-01-21 14:20:53

你好社區, 當SAI子塊時鐘源與另一個子塊處于同步從動模式時,它是否重要?換句話說,兩個子塊是否應該具有相同的時鐘源?謝謝。以上來自于谷歌翻譯以下為原文 Hello Community, Does

2019-07-18 08:00:32

為什么功率測量需要時鐘?同步源是什么?

2021-05-11 06:39:23

的 。 那么為什么FREERTOS 不是用SYSTIMER 做TICK的時鐘源呢? 或者我對這幾個時鐘的作用理解是否還存在誤區。 能幫解答一下嗎?

2023-02-20 06:28:24

如圖所示:左側兩個寄存器中沒有DATA1和DATA2啊之前看網站舉辦過關于源同步的沙龍,求大神幫忙解答一下!!!

2015-01-26 14:07:42

一個緊密同步的儀器中。圖1.一個ADALM1000 SMU通道的框圖。所述ADALM1000處于其心臟一個源測量單元,但它也可以被看作是一個獨立的示波器和函數發生器。但是,由于輸出功能(發生器)和輸入

2018-10-24 10:34:08

我正在使用由計時器觸發的注入轉換來測量緩沖電壓。如參考手冊中所述,我已將 ADC 的頻率限制為 F_adc < F_adc_hclk/4。當我使用同步時鐘

2023-01-04 07:11:27

,這個接口是不是讀FD的數據的時鐘啊?就一個輸入時鐘,它同步到底是和誰同步?異步是與誰異步?我理解的意思是:同步就是讀和寫的速度一樣,異步就是不一樣,要注意它到底能緩存多少,最終的速率是否滿足。我只要

2016-12-15 10:34:51

STM32F103學習筆記四時鐘系統本文簡述了自己學習時鐘系統的一些框架,參照風水月1. 單片機中時鐘系統的理解1.1 概述時鐘是單片機的脈搏,是單片機的驅動源用任何一個外設都必須打開相應的時鐘不使

2021-08-12 08:06:09

性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。在FPGA中,同步信號、異步信號和亞穩態的理解PGA(Field-Programmable Gate Array),即現場

2023-02-28 16:38:14

一、綜述: 1、時鐘源在 STM32 中,一共有 5 個時鐘源,分別是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。①HSI 是高速內部時鐘, RC 振蕩器,頻率為 8MHz

2021-08-18 07:56:26

—————————————————————————————————————————————————————————在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE、PLL。 其實是四個時鐘源,如下圖所示(灰藍色),PLL是由鎖相環電路倍頻得到PLL時鐘

2021-08-23 07:54:07

一、綜述:1、時鐘源在 STM32 中,一共有 5 個時鐘源,分別是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。①HSI 是高速內部時鐘, RC 振蕩器,頻率為 8MHz ;②HSE

2021-08-18 06:00:53

一、在STM32中,有五個時鐘源,為HSI、HSE、LSI、LSE、PLL。①HSI是高速內部時鐘,RC振蕩器,頻率為8MHz。②HSE是高速外部時鐘,可接石英/陶瓷諧振器,或者接外部時鐘源,頻率

2021-08-06 09:01:16

的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種

2019-07-29 07:03:50

1、源同步接口設計之master篇源同步接口在設計中十分常見,例如SPI接口,async NAND FLASH接口。這類接口的時鐘由master生成,并經過IO發送到slave中。對master

2022-06-21 17:38:18

如何利用大功率數字源表構建多源測量單元系統?

2021-05-14 06:11:56

在串行數據傳輸的過程中,如何在FPGA中利用低頻源同步時鐘實現LVDS接收字對齊呢?

2021-04-08 06:39:42

我最初在錯誤的論壇上發布了這個,我無法編輯它 - 可能是因為我太新了。如果你再看到這個,我道歉。大家好 - 我有一個設計,我需要讀取源同步DDR數據與500MHz時鐘,所以1GHz比特率。時鐘到達

2020-08-14 08:46:30

我想知道如果 STM 和 FTM 共享相同的時鐘源,如何檢查它們之間的漂移。

我假設,由于時鐘源配置樹,STM 和 FTM 定時器之間的同步不能保證所有可用配置(例如:STM 的時鐘源來自 CORE PLL,FTM 來自 FIRC 或 PERIPH PLL)

我的假設正確嗎?

2023-05-22 08:32:38

【追蹤嫌犯的利器】定位技術原理解析(4)

2020-05-04 12:20:20

在SDRAM的代碼中,有的模塊工作頻率50MHz,有的100MHz,不同時鐘域間的數據同步太難理解了,請各位前輩指點。代碼如下所示。//同步SDRAM初始化完成信號always @(posedge

2023-09-12 20:39:18

微波作為無線和傳輸設備的重要接入設備,在網絡設計和使用中要針對接入業務的類型,提供滿足其需求的時鐘同步方案。當前階段,微波主要支持的時鐘同步類型包括:GPS,BITS,1588,1588

2019-07-12 07:46:39

`手機通信原理解析:第 1 章 無線通信原理第2 章 移動通信系統第3 章 移動通信系統的多址接入技術第4 章 移動通信系統的語音編碼第5 章 GSM移動通信系統的數字

2011-12-14 14:31:20

子系統部分射頻子系統部分就是實現各種尤源互調測量功能的組件,包括正向和反射接收頻段互調測量,正向發射頻段互調測量,反向互調測量,跨頻段互調測量,諧波測電,多載頻互調測量,大功率穩定性測量和大功率合成系統

2017-11-14 14:47:20

子系統部分射頻子系統部分就是實現各種尤源互調測量功能的組件,包括正向和反射接收頻段互調測量,正向發射頻段互調測量,反向互調測量,跨頻段互調測量,諧波測電,多載頻互調測量,大功率穩定性測量和大功率合成系統等

2017-11-15 10:36:31

我對使用源同步時鐘將大量數據從一個FPGA移動到另一個FPGA感興趣。但由于設計的性質,我沒有很多可用的PLL,因此我無法發送許多時鐘數據對。假設所有跡線具有相同的延遲,是否可以將一個源同步時鐘與多個數據線相關聯?非常感謝你

2020-08-07 09:14:30

氮化鎵功率半導體技術解析基于GaN的高級模塊

2021-03-09 06:33:26

本篇文章為永磁同步電機諧波電流注入控制策略原理解析及仿真教程目前關于此方向的資源教程較少,我個人對其進行了原理總結,仿真實驗分析希望大家有所收獲,喜歡本篇文章的話點個關注收藏贊吧!!!!!!永磁

2021-06-30 06:16:44

。 1 電力系統時間同步概況 目前,電力系統中的時間同步處于變電站內GPS統一的狀態,甚至有很多老舊變電站還沒有實現GPS統一,需要對時的每套設備都配置一套獨立的時鐘系統。由于GPS設備

2012-10-18 10:20:47

E4418B功率計上執行了這些測量,并使用手冊中調出的方法計算出它為0.981 mW,這意味著我需要調整功率參考以滿足規范。但是,當我測量功率參考時。使用E4419B和功率傳感器,我的讀數為1.001

2019-07-26 14:29:45

大家好,又到了每日學習的時候了。今天我們來聊一聊異步電路中的時鐘同步處理方法。既然說到了時鐘的同步處理,那么什么是時鐘的同步處理?那首先我們就來了解一下。時鐘是數字電路中所有信號的參考,沒有時鐘或者

2018-02-09 11:21:12

我已經嘗試了一些使用計數器的UDB組件,但看起來它們與ButhLoCH同步。我們的應用需要一個異步時鐘,因為數字PLL通常會產生太多的抖動(或者相反地,我們可能想要運行一個慢速的系統總線來節省功率

2019-09-11 11:33:23

IEEE 1588標準誕生于2002年,主要定義網絡分布式時鐘的同步協議。測試與測量、電信和多媒體流處理等許多不同應用,都開始首選這種時鐘同步方法。這種標準化時鐘同步法成本效益高,支持異構系統,并可提供納秒級同步精度。

2019-11-01 06:07:58

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40 高精度時鐘同步芯片高精度時鐘芯片典型應用場景:·核心網路由器、交換機·同步以太網設備·電信級邊界時鐘(T-BCS)和從時鐘設備(TimeSlave)·高速以太網端口設備·時鐘時間源設備BITS、時間

2023-12-29 09:37:02

基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 2890

2890

同步網時鐘及等級

基準時鐘 同步網由各節點時鐘和傳遞同步定時信號的同步鏈路構成.同步網的功能是準確地將同步定時信號從基

2010-04-03 16:27:34 3661

3661 虛擬存儲器部件原理解析

2010-04-15 14:25:20 2909

2909 觸摸屏的應用與工作原理解析

2017-02-08 02:13:17 38

38 分享到:標簽:嵌入式; 同步時鐘 同步時鐘系統是同步設備中實現同步通信的核心,因此,要實現數字同步網的設備同步就要求同步時鐘系統一方面要能提供精確的定時同步,另一方面還要能方便實現網絡管理中心對同步

2017-11-04 10:21:44 6

6 時鐘同步是分布式系統的核心技術之一,為實現基于ARM-WinCE嵌入式系統平臺的測試儀器組建分布式測試系統,在介紹IEEE1588精確時鐘協議基本原理的基礎上,提出了使用具有IEEE1588協議硬件

2017-11-28 10:56:07 9

9 微波作為無線和傳輸設備的重要接入設備,在網絡設計和使用中要針對接入業務的類型,提供滿足其需求的時鐘同步方案。當前階段,微波主要支持的時鐘同步類型包括:GPS,BITS,1588,1588

2017-12-07 20:51:01 559

559 現在的硬件設計中,大量的時鐘之間彼此相互連接是很典型的現象。為了保證Vivado優化到關鍵路徑,我們必須要理解時鐘之間是如何相互作用,也就是同步和異步時鐘之間是如何聯系。 同步時鐘是彼此聯系的時鐘。

2018-05-12 10:15:00 19562

19562 我們系統中,主板與從板之間通過交換網片的HW0、HW4互連,要使主板與從板的交換網之間能夠正常交換,必須使這兩個交換網片有一致的幀同步時鐘及位同步時鐘。在現在的單板中,從板的時鐘由主板直接送出。整個系統采用的時鐘源有3種方式:

2018-10-30 11:36:23 7

7 同步相量測量裝置(PMU:phasor measurement unit)是利用全球定位系統(GPS)秒脈沖作為同步時鐘構成的相量測量單元。可用于電力系統的動態監測、系統保護和系統分析和預測等領域.是保障電網安全運行的重要設備。目前世界范圍內已安裝使用數百臺PMU。

2019-11-25 09:21:02 38951

38951 本發明提供了一種將異步時鐘域轉換成同步時鐘域的方法,直接使用同步時鐘對異步時鐘域中的異步寫地址狀態信號進行采樣,并應用預先設定的規則,在特定的讀地址位置對同步時鐘域中的讀地址進行調整,使得在實現

2020-12-21 17:10:55 5

5 在UWB定位系統中,TDOA定位算法那的優勢明顯。我們知道TDOA算法中需要測量UWB信號的到達時間差。如果說TDOA定位的前提是需要測量到達時間差,那么測量到達時間差的前提就是時間需要同步一致

2021-09-26 15:14:44 9908

9908 解析MSP430系統時鐘資源

2021-09-26 11:39:09 1

1 異步復位,同步釋放的理解目錄目錄 同步復位和異步復位 異步復位 同步復位 那么同步復位和異步復位到底孰優孰劣呢? 異步復位、同步釋放 問題1 問題2 問題3 問題4 問題5 參考資料同步

2022-01-17 12:53:57 4

4 史密斯圓圖和阻抗匹配原理解析

2022-11-02 20:16:23 1620

1620 什么是晶振 晶振工作原理解析

2022-12-30 17:13:57 3726

3726

時鐘信號的同步 在數字電路里怎樣讓兩個不同步的時鐘信號同步? 在數字電路中,時鐘信號的同步是非常重要的問題。因為在信號處理過程中,如果不同步,就會出現信號的混淆和錯誤。因此,在數字電路中需要采取一些

2023-10-18 15:23:48 771

771 兩個機器的時鐘怎么同步? 在現代社會中,時間同步對于各種科學研究、工業生產和通信技術都具有重要意義。在許多應用程序中,如分布式系統、計算機網絡和數據同步等領域,為了確保數據的一致性和準確性,需要確保

2024-01-16 14:26:32 254

254 時鐘同步怎樣組網? 時鐘同步是計算機網絡中的重要問題,主要用于確保在多個節點之間保持時間的一致性。時鐘同步對于網絡的可靠性和性能至關重要,因此組網時時鐘同步必須仔細考慮。 在計算機網絡中,各個節點

2024-01-16 15:10:13 168

168 忽視,因為5G網絡具有更高的速率和更低的延遲需求,網絡時鐘同步可以實現更有效和準確的數據傳輸和通信。 首先,讓我們理解一下網絡時鐘同步的基本原理。計算機網絡中使用的時鐘體系主要有兩種,分別是物理時鐘和邏輯時鐘。物理

2024-01-16 16:03:23 227

227 網絡時鐘同步有哪些要求?要注意哪些問題?如何在5G網絡中測試時間與時鐘同步? 網絡時鐘同步是指在計算機網絡中,各個時鐘節點之間通過協議和算法進行時間的同步,以確保網絡中的各個設備擁有相近的時間,從而

2024-01-16 16:03:25 276

276

電子發燒友App

電子發燒友App

評論