在同步電路設(shè)計中,邊沿檢測是必不可少的!

2012-03-01 09:59:04 4918

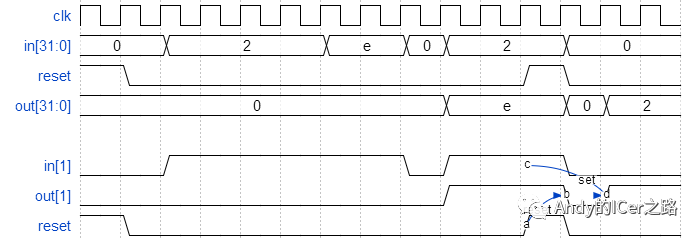

4918 在同步電路設(shè)計中,邊沿檢測是必不可少的!后一種方法所耗的資源要比前一種方法多(一個觸發(fā)器),但是就可以大大提高可靠性,這絕對是物有所值!!

2012-02-01 10:53:05 894

894

這里FPGA牛人一些經(jīng)驗和大家分享,希望能對IC設(shè)計的新手有一定的幫助,能使得他們能少走一些彎路!

2012-03-21 10:17:49 1054

1054 當(dāng)然,任何編程語言的學(xué)習(xí)都不是一朝一夕的事,經(jīng)驗技巧的積累都是在點滴中完成,FPGA設(shè)計也無例外。下面就以我的切身體會,談?wù)?b class="flag-6" style="color: red">FPGA設(shè)計的經(jīng)驗技巧。

2022-10-25 15:51:21 787

787 電子發(fā)燒友網(wǎng)為大家提供了IC檢測經(jīng)驗。集成電路常用的檢測方法有在線測量法、非在線測量法和代換法。

2011-10-28 11:40:06 634

634 信號都是這樣,我找xilinx公司的技術(shù)人員咨詢過,他們也從來沒有遇到這種現(xiàn)像,他們說要達到這種效果得專門設(shè)計一個雙邊沿的觸發(fā)器才行。大家都來分析分析,這到底是怎么回事!或者大家可自已去做個實驗試一下,比如外部一個按鍵信號送入FPGA的一個口子觸發(fā)一個D觸發(fā)器,來看一看是不是會有同樣的現(xiàn)像!

2012-07-17 21:46:37

FPGA CPLFPGA CPLD 數(shù)字電路設(shè)計經(jīng)驗分享FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享摘要:在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)

2012-08-11 10:17:18

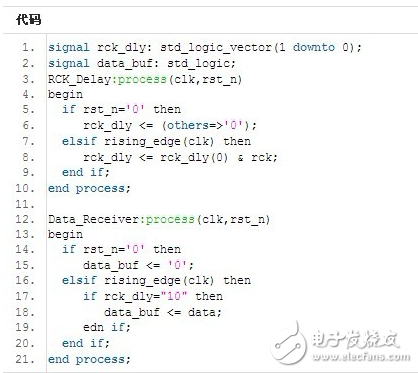

邊沿監(jiān)測代碼常用在接口邏輯設(shè)計中,通過監(jiān)測接口信號的高低電平邊沿的變化控制模塊中其它信號的操作;也可用在時序的實現(xiàn)中,通過監(jiān)測時鐘沿的監(jiān)測信號,做出相應(yīng)的邏輯操作;邏輯代碼如下:`timescale

2012-05-26 10:14:47

本帖最后由 xianer317 于 2014-6-21 19:34 編輯

FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享

2014-06-21 19:33:20

FPGA經(jīng)驗之談 摘要:在數(shù)字電路的設(shè)計中,時序設(shè)計是一個系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計方法中,對時序控制的抽象度也相應(yīng)提高,因此在設(shè)計中較難把握,但在理解RTL電路時序模型

2009-10-21 17:30:31

` 本帖最后由 eehome 于 2013-1-5 10:00 編輯

FPGA經(jīng)驗談(西安大唐電信)`

2011-09-29 11:05:40

FPGACPLD數(shù)字電路設(shè)計經(jīng)驗分享

2012-08-07 21:46:49

FPGA_100天之旅_邊沿檢測

2017-09-28 13:37:44

華為FPGA關(guān)于FIFO的經(jīng)驗之談!

2015-07-16 16:05:45

應(yīng)用,它的優(yōu)點在這里無庸贅述。從個人實用角度看,對于學(xué)生,掌握FPGA可以找到一份很好的工作,對于有經(jīng)驗的工作人員,使用fgpa可以讓設(shè)計變得非常有靈活性。掌握了fpga的設(shè)計,單板硬件設(shè)計就非常容易(不是

2011-10-14 13:31:46

以xinlixFPGA為載體 ,實現(xiàn) FPGA 對電梯異常的檢測 ,并能進行顯示。。。。至于后期報告 ,后面發(fā)布。。

2012-07-05 01:32:00

FPGA牛人的經(jīng)驗分享

2012-08-17 22:27:09

fpga經(jīng)驗談

2012-08-06 14:38:33

本帖最后由 qiang6 于 2012-8-17 09:59 編輯

fpga經(jīng)驗談(西安大唐電信)https://bbs.elecfans.com/forum.php?mod=viewthread&tid=266102&fromuid=483505

2012-08-17 09:49:14

fpga經(jīng)驗談(西安大唐電信)

2012-08-18 07:25:33

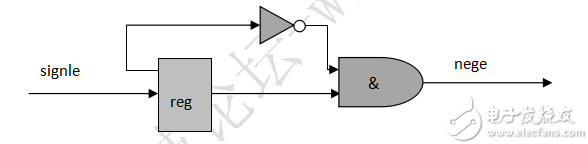

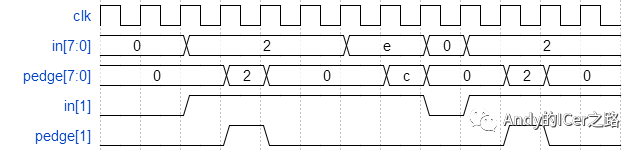

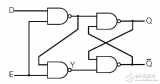

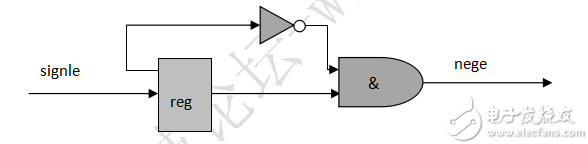

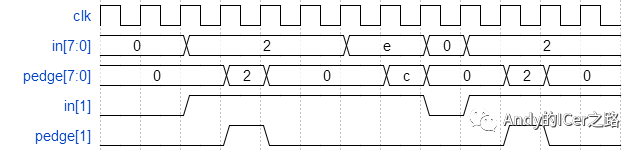

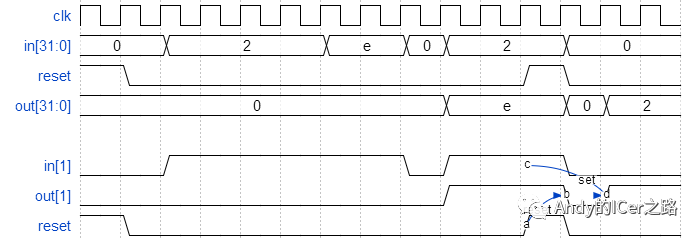

`fpga應(yīng)用篇(二):邊沿檢測上一篇介紹了阻塞賦值與非阻塞賦值,這次我們利用非阻塞賦值產(chǎn)生一個簡單的應(yīng)用即邊沿檢測,邊沿檢測一般用來產(chǎn)生使能信號。程序如下:綜合后電路:clk為主時鐘分頻之后得到

2017-04-06 21:28:08

fpga設(shè)計經(jīng)驗分享

2013-04-14 23:18:23

fpga高手經(jīng)驗談

2012-08-20 15:23:42

邊沿檢測設(shè)計報告

2017-09-26 15:38:19

形成的反射就變強,將會導(dǎo)致位寬度失調(diào)的錯誤。ISO11898中只規(guī)定1M波特率下分支不超過0.3米,但是在其它情況下并沒有做聲明,這個便取決于現(xiàn)場工程師們的經(jīng)驗。二、消除邊沿臺階邊沿臺階是造成錯誤波形

2019-10-07 07:00:00

STM32定時器怎樣通過ETR模式進行邊沿檢測并計數(shù)呢?如何去實現(xiàn)?

2021-11-24 06:51:27

請問各位大佬,stm32外部中斷的邊沿檢測時,對上升沿或者下降沿是否有要求,必須小于或者大于多少時間,或者在多少時間內(nèi)必須上升或者下降多少V才算觸發(fā)。在spec中只看到了最小是10ns就可以,同時邊沿檢測的電平是GPIO的VIH和VIL嗎?

2024-03-20 08:31:04

本帖最后由 mengyi1989 于 2019-12-7 12:40 編輯

立即學(xué)習(xí)>>夢翼師兄的FPGA實戰(zhàn)課程眾籌寫在前面的話在項目設(shè)計中,我們經(jīng)常需要檢測信號由高到低或者由

2019-12-04 10:24:31

程序邊沿檢測下降沿并統(tǒng)計數(shù)量(數(shù)量到達2后重新計數(shù),并發(fā)送動作信號),但是最終發(fā)現(xiàn)檢測結(jié)果不準(zhǔn)確,有時候能檢測到,有時候檢測不到。萬分感謝您的解答和建議!下面是verilog代碼[code]//邊沿檢測initial numinitial led

2021-08-21 12:58:00

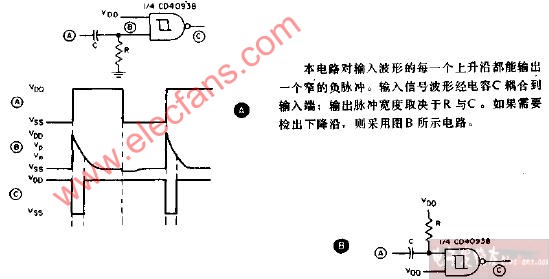

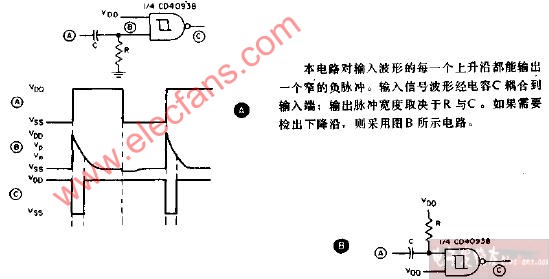

入圖,有沒有大神分析一下,是怎實現(xiàn)邊沿檢測的,它各個時期的電平狀態(tài)是什么

2016-04-13 14:36:25

我看到網(wǎng)上關(guān)于邊沿檢測的講解,有個地方不理解,t0時刻和t1時刻分別是怎樣的時刻,trigger在時鐘上升沿經(jīng)過觸發(fā)器輸出的信號和經(jīng)過非門的信號是什么樣的關(guān)系?我的理解是trigger分別輸出后是兩個電平相反的信號,為什么相與之后就可以檢測是否為上升沿或者下降沿?謝謝。

2023-05-10 14:52:22

新手入門FPGA,求入門經(jīng)驗{:1:}

2015-08-01 16:57:07

有誰有設(shè)計過DSP于FPGA通訊的經(jīng)驗,求講解一下思路

2015-10-30 18:16:15

二極管的檢測方法與經(jīng)驗三極管的檢測方法與經(jīng)驗

2021-04-09 06:54:46

請求大神分享一些關(guān)于FPGA設(shè)計的學(xué)習(xí)經(jīng)驗

2021-04-15 06:47:08

本文分享了一些常見電子元器件的檢測經(jīng)驗和技巧。

2021-06-07 07:08:50

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2012-05-23 19:49:45

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2012-08-20 15:37:36

電路設(shè)計[FPGA]設(shè)計經(jīng)驗

2019-01-03 14:19:28

1、本人現(xiàn)有四年的FPGA設(shè)計及測試經(jīng)驗,碩士學(xué)歷,目前在職。 2、曾經(jīng)作為某重要項目的FPGA軟件負責(zé)人,項目管理經(jīng)驗豐富。3、熟悉xilinx芯片的底層結(jié)構(gòu),優(yōu)化芯片資源以及時序約束。4、熟練

2014-01-02 11:16:50

至芯昭哥帶你學(xué)FPGA之FPGA_100天之旅_邊沿檢測

2017-08-17 09:46:51

我在手冊上看到AD9361 LVDS模式發(fā)送數(shù)據(jù)的時鐘要使用雙邊沿,在FPGA中,我將FB_CLK倍頻到2倍使用單邊沿發(fā)送數(shù)據(jù),再將FB_CLK不變輸出到ad9361,這樣可以嗎?還是必須在FPGA中直接使用FB_CLK雙邊沿發(fā)送數(shù)據(jù)?

2018-10-15 09:21:23

打開開關(guān)的時候,功耗就上來了,無法進入低功耗模式,如何讓我們的藍牙模塊監(jiān)測到高低電平之后,進入低功耗模式?群里問了下,說需要讓該io口支持雙邊沿觸發(fā),即,上升沿和下降沿同時觸發(fā)檢測,請問,方向是否是正確的?其二,如果正確,如果設(shè)置雙邊沿觸發(fā)?

2019-11-07 15:55:30

的數(shù)據(jù)進行計數(shù);停止位不參與,起始位加上數(shù)據(jù)位共9bit。該計數(shù)器的計數(shù)周期為9。本工程使用了檢測信號下降沿的方法,信號下降沿的檢測方法:檢查uart_rx的下降沿,就要用到FPGA里的邊沿檢測技術(shù)

2019-11-29 10:08:59

本人想做黑白塊的邊沿檢測,但是為了達到檢測的高精度,普通光電對管與光電傳感器的區(qū)別在哪里?因為原理相同,也不知道到底性能差別在哪里?有沒有大神可以一起討論一下?

2015-05-31 09:47:10

二極管的檢測方法與經(jīng)驗 1?檢測小功率晶體二極管 A?判別正、負電極 (a)?觀察外殼上的的符號標(biāo)記。通常在二極管的外殼上標(biāo)有二極管的符號,帶有三角形箭頭的

2009-10-07 12:02:21 12

12 三極管的檢測方法與經(jīng)驗 1?中、小功率三極管的檢測 A?已知型號和管腳排列的三極管,可按下述方法來判斷其性能好壞 (a)?測

2009-10-07 12:03:17 36

36 FPGACPLD設(shè)計經(jīng)驗與技巧

2010-02-09 09:43:56 73

73 三極管的檢測方法與經(jīng)驗

2006-04-17 21:41:56 4596

4596 二極管的檢測方法與經(jīng)驗

2006-04-17 21:41:58 1459

1459

電感器、變壓器檢測方法與經(jīng)驗

2006-04-17 21:42:11 660

660 電容器檢測方法與經(jīng)驗

2006-04-17 21:42:16 576

576 電阻器的檢測方法與經(jīng)驗

2006-08-08 09:56:00 760

760

常用電子元器件檢測方法與經(jīng)驗

2006-06-30 19:26:14 2969

2969

脈沖邊沿檢出器電路圖

2009-03-28 09:20:16 560

560

場效應(yīng)管檢測方法與經(jīng)驗

一、用指針式萬用表對場效應(yīng)管進行判

2009-07-02 18:28:30 427

427

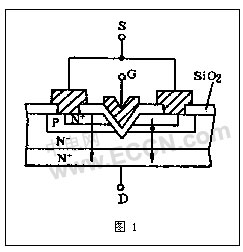

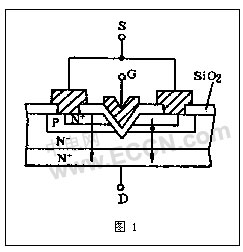

CMOS觸發(fā)器在CP邊沿的工作特性研究

對時鐘脈沖(簡稱CP)邊沿時間的要求,是觸發(fā)器品質(zhì)評價的重要指標(biāo)之一。觸發(fā)器只有在CP邊沿陡峭(短的邊沿時

2009-10-17 08:52:12 1621

1621

電容器的檢測方法與經(jīng)驗 1 固定電容器的檢測 A 檢測10pF以下的小電容 因10pF以下的固定電容器容量太小,用萬用表進行測量,只能定性的檢查其是否有漏

2009-11-24 11:15:59 840

840 電感器、變壓器檢測方法與經(jīng)驗 1 色碼電感器的的檢測 將萬用表置于R×1擋,紅、黑表筆各接色碼電感器的任一引出端,此時指針應(yīng)向右擺動。根據(jù)測出

2009-11-24 11:17:22 1005

1005 效應(yīng)管檢測方法與經(jīng)驗

一、用指針式萬用表對場效應(yīng)管進行判別(1)用測電阻法判別結(jié)型場效應(yīng)管的電極根據(jù)場效應(yīng)管的PN結(jié)

2009-11-30 10:52:21 1462

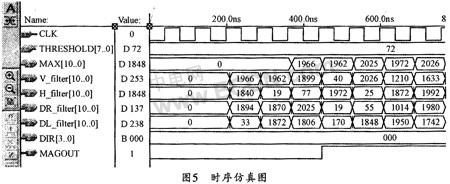

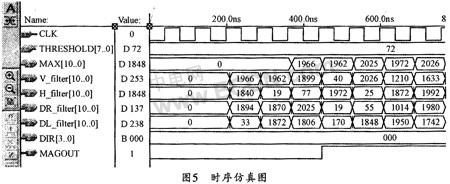

1462 基于FPGA的圖像邊緣檢測

引言

圖像邊緣檢測是圖像處理的一項基本技術(shù),在工業(yè)、醫(yī)學(xué)、航天和軍事等領(lǐng)域有著廣泛的應(yīng)用。圖像處理的速度一直是一

2010-01-14 11:07:57 1714

1714

可以將電平觸發(fā)器轉(zhuǎn)換成更為靈活的邊沿觸發(fā)器(采用時間控制方法)。邊沿觸發(fā)器只在上升沿或下降沿處對輸入采樣。這種轉(zhuǎn)換可以這樣來實現(xiàn):將原來的時鐘信

2010-08-10 11:10:26 5657

5657

為了滿足對隨機數(shù)性能有一定要求的系統(tǒng)能夠?qū)崟r檢測隨機數(shù)性能的需求,提出了一種基于FPGA的隨機數(shù)性能檢測設(shè)計方案。根據(jù)NIST的測試標(biāo)準(zhǔn),采用基于統(tǒng)計的方法,在FPGA內(nèi)部實現(xiàn)了

2013-07-24 16:52:06 45

45 100條FPGA經(jīng)驗 非常值得收藏

100條FPGA經(jīng)驗 非常值得收藏

2015-11-11 17:01:11 22

22 分析了FPGA器件發(fā)生單粒子效應(yīng)的空間分布特性,設(shè)計并實現(xiàn)了一種面向FPGA單粒子軟錯誤的檢測電路。將該電路放置在FPGA待檢測電路的附近,利用單粒子效應(yīng)的空間特性,則可以根據(jù)檢測模塊的狀態(tài)變化

2015-12-31 09:25:13 8

8 sobel_FPGA l邊緣檢測.源代碼。

2016-05-03 16:42:45 8

8 fpga經(jīng)驗談,有需要的朋友可以下來看看。

2016-05-10 10:46:40 23

23 電路設(shè)計[FPGA]設(shè)計經(jīng)驗,有需要的下來看看

2016-05-20 11:16:35 46

46 電子專業(yè)單片機相關(guān)知識學(xué)習(xí)教材資料——FPGACPLD數(shù)字電路設(shè)計經(jīng)驗,感興趣的小伙伴們可以瞧一瞧。

2016-09-13 17:46:48 0

0 一種單鎖存器CMOS三值D型邊沿觸發(fā)器設(shè)計

2017-01-17 19:54:24 25

25 邊沿觸發(fā)一般時間短,邊沿觸發(fā)一般時間都是us級的,響應(yīng)要快的,而電平觸發(fā)只須是高和低就可以了,沒時間要求,比如10s 時間內(nèi)總是低電平,那么它也是觸發(fā)的,比如中斷計時或計數(shù),最好用邊沿觸發(fā),用電平觸發(fā)誤差會很大,電平觸發(fā)一般用于簡單報警,開關(guān)一類(時間要求不高的

2017-11-14 11:38:47 27141

27141

邊沿檢測與提取程序

2018-01-29 14:56:31 0

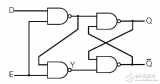

0 本文開始介紹了JK觸發(fā)器工作特性與邊沿JK觸發(fā)器的特點,其次介紹了邊沿JK觸發(fā)器工作原理與特點,最后介紹了集成邊沿式JK觸發(fā)器邊沿式JK觸發(fā)器設(shè)計及波形仿真圖形。

2018-01-30 17:17:49 35481

35481

邊沿觸發(fā)器,指的是接收時鐘脈沖CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數(shù)據(jù)。在CP=l 及CP=0 期間以及CP非約定跳變到來時,觸發(fā)器不接收數(shù)據(jù)的觸發(fā)器。具有下列特點的觸發(fā)器稱為邊沿觸發(fā)方式觸發(fā)器,簡稱邊沿觸發(fā)器。

2018-01-31 09:02:33 69649

69649

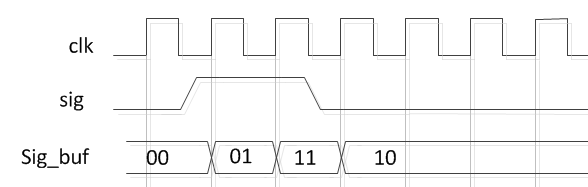

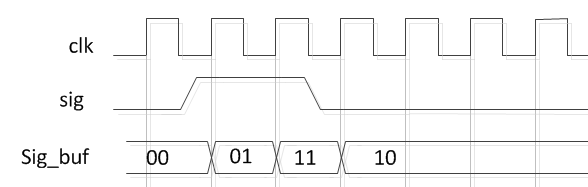

本文記錄一下關(guān)于用移位寄存器實現(xiàn)邊沿檢測的技巧。要學(xué)會硬件思維式的“模塊式”讀寫代碼,那么請多看別人的代碼,并用ISE或者VIVADO綜合出來看看。 邊沿檢測 邊沿檢測,顧名思義,就是檢查信號的邊沿

2018-04-15 10:26:01 2933

2933 設(shè)計背景: 在我們工程設(shè)計中,有時會需要到上升沿和下降沿這么一個說法,通過上升沿和下降沿來驅(qū)動一個電路,那么學(xué)習(xí)邊沿檢測就非常的重要了。 設(shè)計原理 : 在學(xué)習(xí)邊沿檢測前我們先學(xué)習(xí)一下下面的電路,這樣

2018-06-13 11:20:07 5161

5161

邊沿時間分為上升沿時間、下降沿時間。下降沿時間是按照電壓(20%~80%電壓區(qū)間,有些按照10%~90%電壓區(qū)間測量邊沿時間,文中以20%~80%電壓區(qū)間測量邊沿時間)。表中給出時間范圍,如果超出

2018-09-22 08:51:00 16710

16710

CAN總線邊沿時間會影響采樣正確性,而采樣錯誤會造成錯誤幀不斷出現(xiàn),影響CAN總線通信。

2018-11-23 14:04:27 7540

7540

元器件的檢測方法和經(jīng)驗很有必要以下對常用電子元器件的檢測經(jīng)驗和方法進行介紹供對考包括了:一電阻器的檢測方法與經(jīng)驗 ,二電容器的檢測方法與經(jīng)驗,三電感器變壓器檢測方法與經(jīng)驗

2019-02-18 08:00:00 14

14 邊沿檢測電路(edge detection circuit)是個常用的基本電路。所謂邊沿檢測就是對前一個clock狀態(tài)和目前clock狀態(tài)的比較,如果是由0變?yōu)?,能夠檢測到上升沿,則稱為上升沿檢測

2019-11-19 07:09:00 10011

10011 ADSY8401:帶VCOM、NRS緩沖器和高壓邊沿檢測器的LCD電平移位器數(shù)據(jù)表

2021-04-30 09:55:16 10

10 FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 “ 本文主要分享了在Verilog設(shè)計過程中一些經(jīng)驗與知識點,主要包括Verilog仿真時常用的系統(tǒng)任務(wù)、雙向端口的使用(inout)、邊沿檢測”

2022-03-15 13:34:56 1747

1747 邊沿采樣技術(shù)實現(xiàn)上升沿捕獲進而實現(xiàn)外部信號的上升沿觸發(fā)。 邊沿檢測電路的實現(xiàn)方法; 1、always @ (posedge signal) FPGA不便于處理此類觸發(fā)信號,除非外部輸入信號作為全局時鐘使用。另外眾所周知由于電路不能能避免抖動現(xiàn)象,所以用這

2022-11-26 10:20:09 914

914 邊沿檢測指令有掃描操作數(shù)的信號下降沿指令和掃描操作數(shù)的信號上升沿指令。

2023-04-10 09:38:27 884

884 邊沿檢測指令有掃描操作數(shù)的信號下降沿指令和掃描操作數(shù)的信號上升沿指令。

2023-04-12 09:23:26 4666

4666 本文將從Verilog和邊沿檢測的基本概念入手,介紹Verilog邊沿檢測的原理和應(yīng)用代碼示例。

2023-05-12 17:05:56 2183

2183

對于8位向量中的每個位,檢測輸入信號何時從一個時鐘周期的0變?yōu)橄乱粋€時鐘周期的1(類似于上升沿檢測)。應(yīng)在從0到1的跳變發(fā)生后的周期內(nèi)設(shè)置輸出位。

2023-06-05 16:24:02 541

541

在設(shè)計雙邊沿采樣電路(Dual-edge triggered flip-flop)之前,先從單邊沿采樣電路設(shè)計(Edge capture register)開始。

2023-06-05 16:27:30 852

852

1、什么是邊沿檢測 邊沿檢測用于檢測信號的上升沿或下降沿,通常用于使能信號的捕捉等場景。 2、采用1級觸發(fā)器的邊沿檢測電路設(shè)計(以下降沿為例) 2.1、設(shè)計方法 設(shè)計波形圖如下所示: 各信號說明如下

2023-06-17 14:26:40 1244

1244

邊沿檢測大致分為:上升沿檢測,下降沿檢測和,雙沿檢測。原理都是通過比輸入信號快很多的時鐘去采集信號,當(dāng)出現(xiàn)兩個連續(xù)的采集值不等的時候就是邊沿產(chǎn)生處。

2023-06-28 15:19:12 1037

1037

。如果該指令檢測到 RLO 從“0”變?yōu)椤?”,則說明出現(xiàn)了一個信號上升沿。 每次執(zhí)行指令時,都會查詢信號上升沿。檢測到信號上升沿時,該指令輸出 Q 將立即返回程序代碼長度的信號狀態(tài)“1”。在其它任何情況下,該輸出返回的信號狀態(tài)均為“0”。 說明 修改邊沿

2023-06-28 16:20:11 355

355

FPGA設(shè)計經(jīng)驗談

2022-12-30 09:20:07 1

1 電子發(fā)燒友網(wǎng)站提供《FPGA/CPLD數(shù)字電路設(shè)計經(jīng)驗分享.pdf》資料免費下載

2023-11-21 11:03:12 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評論