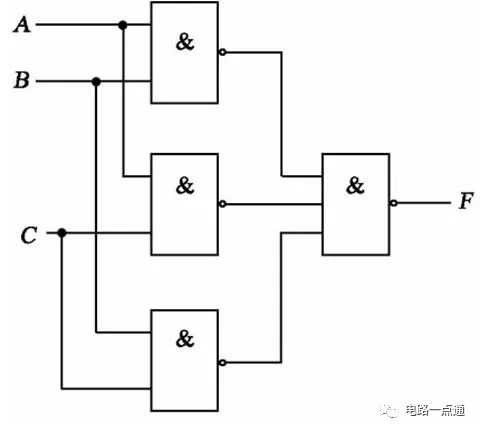

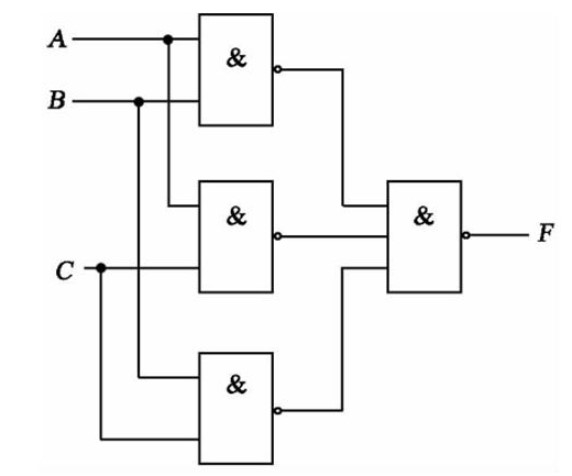

組合電路是最常見(jiàn)的邏輯電路,可以用一些常用的門(mén)電路來(lái)組合成具有其它功能的門(mén)電路。

2023-10-11 17:49:49 766

766

所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-08-16 09:15:23 740

740

本篇內(nèi)容主要回顧第三章組合邏輯電路的知識(shí),雖然前面提到過(guò)組合邏輯電路是數(shù)字電路中很重要的一部分,但是學(xué)習(xí)起來(lái)相對(duì)簡(jiǎn)單,主要是要學(xué)會(huì)掌握方法。

2023-05-24 14:38:59 401

401

時(shí)序邏輯電路分析和設(shè)計(jì)的基礎(chǔ)是組合邏輯電路與觸發(fā)器,所以想要分析和設(shè)計(jì),前提就是必須熟練掌握各種常見(jiàn)的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎(chǔ)顯得尤為重要。 本文主要介紹時(shí)序邏輯電路的分析方法。

2023-05-22 18:24:31 830

830

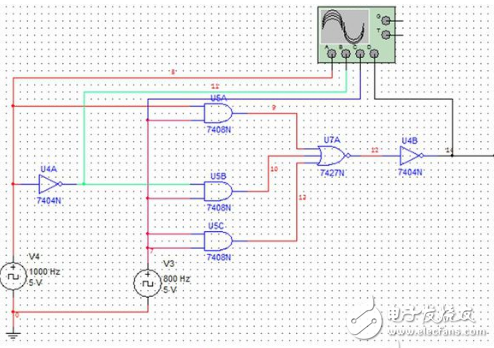

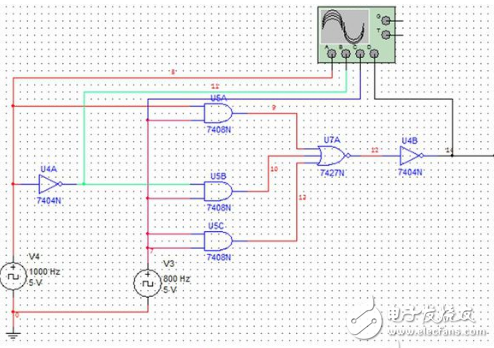

邏輯門(mén)及組合邏輯電路實(shí)驗(yàn)實(shí)驗(yàn)目的1. 掌握與非門(mén)、或非門(mén)、與或非門(mén)及異或門(mén)的邏輯功能。2. 了解三態(tài)門(mén)的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門(mén)的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)方法。4.

2008-09-25 17:28:34

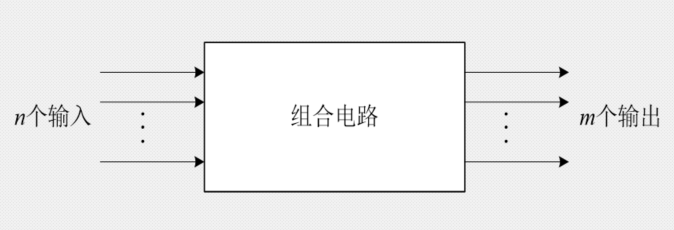

組合邏輯電路: 電路在任一時(shí)刻的輸出狀態(tài)僅由該時(shí)刻的輸入信號(hào)決定,與電路在此信號(hào)輸入之前的狀態(tài)無(wú)關(guān)。

2023-03-21 11:57:00 659

659

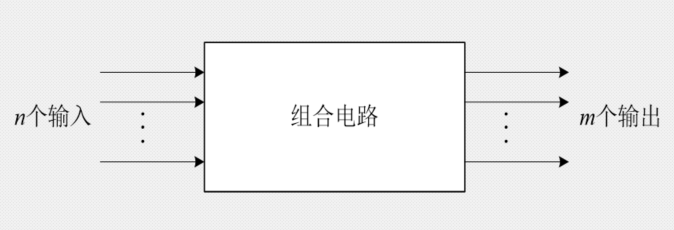

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2023-03-14 17:06:50 2914

2914

所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2023-03-06 14:37:26 1100

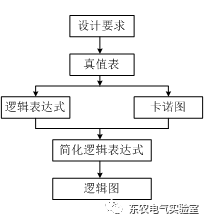

1100 數(shù)字電路中的組合邏輯電路的設(shè)計(jì)與分析過(guò)程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計(jì)步驟,順便回顧一下組合邏輯電路的分析方法。

2023-02-03 09:56:23 1563

1563 本文介紹開(kāi)發(fā)組合邏輯電路時(shí)可能發(fā)生的意外開(kāi)關(guān)事件,稱(chēng)為危險(xiǎn)。 本文是關(guān)于使用邏輯門(mén)進(jìn)行組合電路設(shè)計(jì)和仿真的介紹性系列文章的第二部分。在上一篇文章中,我們介紹了 組合邏輯電路 以及如何簡(jiǎn)化它們

2023-01-27 14:18:00 757

757

組合邏輯電路:用各種門(mén)電路組成的,用于實(shí)現(xiàn)某種功能的復(fù)雜邏輯電路。特點(diǎn):某一時(shí)刻的輸出狀態(tài)僅由該時(shí)刻電路的輸入信號(hào)決定, 而與該電路在此輸入信號(hào)之前所具有的狀態(tài)無(wú)關(guān)。

2022-12-05 14:52:54 3

3 組合邏輯電路的特點(diǎn)是輸入的變化直接反映了輸出的變化,其輸出的狀態(tài)僅取決于輸入的當(dāng)前狀態(tài),與輸入、輸出的原始狀態(tài)無(wú)關(guān)。如果從電路結(jié)構(gòu)上來(lái)講,組合邏輯電路是沒(méi)有觸發(fā)器組件的電路。

2022-10-24 16:02:32 719

719 從今天開(kāi)始新的一章-Circuits,包括基本邏輯電路、時(shí)序電路、組合電路等。

2022-10-10 15:39:01 681

681 所謂組合邏輯電路的分析,就是根據(jù)給定的邏輯電路圖,求出電路的邏輯功能。

2022-08-12 17:19:26 9712

9712

1、掌握組合邏輯電路的設(shè)計(jì)方法。

2、掌握組合邏輯電路的靜態(tài)測(cè)試方法。

3、熟悉CPLD設(shè)計(jì)的過(guò)程,比較原理圖輸入和文本輸入的優(yōu)劣。

2022-07-10 14:38:36 16

16 組合邏輯電路的組成及其分析設(shè)計(jì)方法說(shuō)明。

2021-05-10 10:10:42 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路和時(shí)序邏輯電路的學(xué)習(xí)課件免費(fèi)下載包括了:任務(wù)一 組合邏輯電路,任務(wù)二 編碼器,任務(wù)三 譯碼器,任務(wù)四 集成觸發(fā)器,任務(wù)五 寄存器,任務(wù)六 計(jì)數(shù)器。

2020-10-27 15:58:24 28

28 輸出信號(hào)只是該時(shí)刻輸入信號(hào)的函數(shù),與過(guò)去狀態(tài)無(wú)關(guān),這樣的數(shù)字電路就稱(chēng)為組合邏輯電路。

2020-10-20 14:41:29 10

10 邏輯電路在任何時(shí)刻產(chǎn)生的穩(wěn)定的輸出信號(hào)僅僅取決于該時(shí)刻的輸入信號(hào),而與過(guò)去的輸入信號(hào)無(wú)關(guān),即與輸入信號(hào)作用前的狀態(tài)無(wú)關(guān),這樣的電路稱(chēng)為組合邏輯電路。

2020-08-08 10:40:00 4638

4638

分析組合邏輯電路的目的是,對(duì)于一個(gè)給定的邏輯電路,確定其邏輯功能。

2020-08-04 15:50:00 29964

29964 本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路的學(xué)習(xí)教程課件免費(fèi)下載包括了:1 數(shù)字電路概述,2 邏輯門(mén)電路,3 邏輯函數(shù)及其化簡(jiǎn),4 組合邏輯電路的分析與設(shè)計(jì),5 組合邏輯部件

2019-10-11 16:47:00 15

15 組合邏輯電路是無(wú)記憶數(shù)字邏輯電路,其任何時(shí)刻的輸出僅取決于其輸入的組合.

2019-06-22 10:53:20 45022

45022

組合邏輯電路是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。而時(shí)序邏輯電路不僅僅取決于當(dāng)前的輸入信號(hào),而且還取決于電路原來(lái)的狀態(tài),或者說(shuō),還與以前的輸入有關(guān)。

2019-02-26 15:32:30 60005

60005 時(shí)序邏輯電路是由組合邏輯電路與記憶電路(又稱(chēng)存儲(chǔ)電路) 組合而成的。 常見(jiàn)時(shí)序邏輯電路有觸發(fā)器、 寄存器和計(jì)數(shù)器等。

2019-02-26 15:25:01 48178

48178 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-02-26 15:22:20 29485

29485 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路教程之組合邏輯電路課件詳細(xì)資料免費(fèi)下載主要內(nèi)容包括了:一 概述 二 組合邏輯電路的分析和設(shè)計(jì)方法 三 若干常用的組合邏輯電路 四 組合邏輯電路中的競(jìng)爭(zhēng)冒險(xiǎn)

2018-12-28 08:00:00 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路基礎(chǔ)之組合邏輯電路的詳細(xì)資料概述包括了:1.組合邏輯電路的特點(diǎn)2.組合邏輯電路的分析與設(shè)計(jì)方法3.常用組合邏輯電路的工作原理及其應(yīng)用 4.加法器、比較器、譯碼器、編碼器、選擇器5.組合邏輯電路中的競(jìng)爭(zhēng)和冒險(xiǎn)現(xiàn)象。

2018-10-17 08:00:00 26

26 根據(jù)邏輯功能的不同,可把數(shù)字電路分為組合邏輯電路(Combinational Logic Circuit)和 時(shí)序邏輯電路(Sequential Logic Circuit)兩大類(lèi)。

2018-07-20 08:00:00 4

4 分析時(shí)序邏輯電路也就是找出該時(shí)序邏輯電路的邏輯功能,即找出時(shí)序邏輯電路的狀態(tài)和輸出變量在輸入變量和時(shí)鐘信號(hào)作用下的變化規(guī)律。上面講過(guò)的時(shí)序邏輯電路的驅(qū)動(dòng)方程、狀態(tài)方程和輸出方程就全面地描述了時(shí)序邏輯電路的邏輯功能。

2018-01-30 18:55:32 120321

120321

組合邏輯電路和時(shí)序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。而時(shí)序邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出不僅取決于當(dāng)時(shí)的輸入信號(hào),而且還取決于電路原來(lái)的狀態(tài),或者說(shuō),還與以前的輸入有關(guān)。

2018-01-30 17:26:04 89189

89189

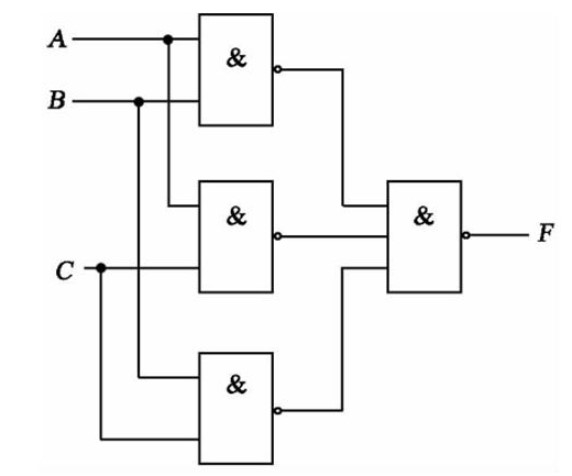

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。單一的與門(mén)、或門(mén)、與非門(mén)、或非門(mén)、非門(mén)等邏輯門(mén)不足以完成復(fù)雜的數(shù)字系統(tǒng)設(shè)計(jì)要求。組合邏輯電路是采用兩個(gè)或兩個(gè)以上基本邏輯門(mén)來(lái)實(shí)現(xiàn)更實(shí)用、復(fù)雜的邏輯功能。

2018-01-30 17:05:44 59977

59977

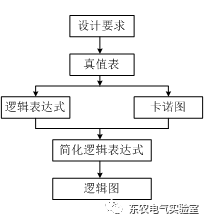

組合邏輯電路的設(shè)計(jì)與分析過(guò)程相反,本文小編主要跟大家介紹一下關(guān)于組合邏輯電路的設(shè)計(jì)步驟,順便回顧一下組合邏輯電路的分析方法。

2018-01-30 16:46:31 116708

116708

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。

2018-01-30 16:24:25 35974

35974

若一個(gè)邏輯電路在任何時(shí)刻產(chǎn)生的穩(wěn)定輸出信號(hào)僅僅取決于該時(shí)刻的輸入信號(hào),而與過(guò)去的輸入信號(hào)無(wú)關(guān),即與輸入信號(hào)作用前的電路狀態(tài)無(wú)關(guān),則稱(chēng)該電路為組合邏輯電路。

2018-01-30 16:03:16 47245

47245

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2017-11-29 11:28:01 9071

9071

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。

2017-05-22 15:15:59 67979

67979

詳細(xì)介紹了組合邏輯電路的分析方法,包括加法器、譯碼器、編碼器、分配器、選擇器等組合邏輯電路的分析方法

2017-01-22 13:13:01 1

1 分析數(shù)字邏輯電路的方法

2017-01-17 19:54:24 12

12 數(shù)字電子技術(shù)--組合邏輯電路

2016-12-12 22:07:22 5

5 數(shù)字電子技術(shù)-- 組合邏輯電路

2016-12-12 22:07:22 1

1 電子專(zhuān)業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之組合邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 19

19 電子專(zhuān)業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料之時(shí)序邏輯電路的分析與設(shè)計(jì)

2016-09-02 14:30:26 20

20 門(mén)電路,組合邏輯電路的分析方法和設(shè)計(jì)方法,編碼器,譯碼器,數(shù)據(jù)選擇器和分配器

,加法器和數(shù)值比較器。

2016-04-29 11:28:59 16

16 數(shù)字電路 實(shí)驗(yàn)一 組合邏輯電路的設(shè)計(jì)與測(cè)試

2015-11-17 18:23:49 1

1 組合邏輯電路,感興趣的可以下載看看,免費(fèi)的哦!

2015-10-29 15:08:16 31

31 為縮短理論與實(shí)踐的距離,提高靈活應(yīng)用數(shù)字元器件的能力,提出了組合邏輯電路設(shè)計(jì)的第五步。組合邏輯電路設(shè)計(jì)通常有四步,設(shè)計(jì)完成畫(huà)出符合功能要求的邏輯圖,一般是把其轉(zhuǎn)換

2011-05-03 17:58:26 61

61 一、實(shí)驗(yàn)目的掌握組合邏輯電路的設(shè)計(jì)與測(cè)試方法

2010-09-21 16:52:20 99

99 實(shí)驗(yàn)目的1. 掌握與非門(mén)、或非門(mén)、與或非門(mén)及異或門(mén)的邏輯功能。2. 了解三態(tài)門(mén)的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門(mén)的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)

2010-08-18 14:50:44 109

109 一、實(shí)驗(yàn)目的:

1. 熟悉編碼器、譯碼器、數(shù)據(jù)選擇器等組合邏輯功能模塊的功能與使用方法。

2. 掌握用MSI設(shè)計(jì)的組合邏輯電路的方法。

二、

2010-08-16 17:36:29 44

44 2.1 分立元件門(mén)電路

2.2 集成邏輯門(mén)電路

2.3 組合邏輯電路的分析方法

2.4 組合邏輯電的設(shè)計(jì)方法

2010-08-12 17:34:19 116

116 數(shù)字邏輯電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類(lèi)。組合邏輯電路在任一時(shí)刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過(guò)去的輸入無(wú)關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 47

47 數(shù)字邏輯電路按邏輯功能和電路組成的特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路兩大類(lèi)。

2010-08-10 11:51:58 39

39 講述組合邏輯電路設(shè)計(jì)基礎(chǔ)

2010-05-06 10:29:15 40

40 電子技術(shù)--組合邏輯電路掌握組合邏輯電路的分析方法與設(shè)計(jì)方法掌握利用二進(jìn)制譯碼器和數(shù)據(jù)選擇器進(jìn)行邏輯設(shè)計(jì)的方法理解加法器、編碼器、譯碼器等中規(guī)模集成電

2010-04-12 17:52:29 49

49 各種邏輯電路簡(jiǎn)介

邏輯電路:

以二進(jìn)制為原理、實(shí)現(xiàn)數(shù)字信號(hào)邏輯運(yùn)算和操作的電路。分組合邏輯電路和

2009-11-24 13:27:04 2788

2788 組合邏輯電路的分析、設(shè)計(jì)和調(diào)試(一)一、實(shí)驗(yàn)目的1.進(jìn)一步熟悉數(shù)字邏輯實(shí)驗(yàn)箱的使用。2.掌握用SSI(小規(guī)模數(shù)字集成電路)構(gòu)成的組合邏輯電路的分析與設(shè)計(jì)方法。

2009-11-19 15:01:53 185

185 同步時(shí)序邏輯電路:本章系統(tǒng)的講授同步時(shí)序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時(shí)序邏輯電路模型與描述方法開(kāi)始,介紹同步時(shí)序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 71

71 組合邏輯電路電子教案:數(shù)字邏輯電路可分為兩大類(lèi): 一類(lèi)叫組合邏輯電路;另一類(lèi)叫時(shí)序邏輯電路。本章首先介紹組合邏輯電路的共同特點(diǎn)和描述方法,然后重點(diǎn)介紹組合邏輯電

2009-09-01 08:58:29 86

86 組合邏輯電路(簡(jiǎn)稱(chēng)組合電路)任意時(shí)刻的輸出信號(hào)僅取決于該時(shí)刻的輸入信號(hào),與信號(hào)作用前電路原來(lái)的狀態(tài)無(wú)關(guān)時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)任意時(shí)刻的輸出信號(hào)不僅取決

2009-07-15 18:45:58 62

62 組合邏輯電路實(shí)驗(yàn)分析一、實(shí)驗(yàn)目的 1.掌握組合邏輯電路的分析方法與測(cè)試方法; 2.了解組合電路的冒險(xiǎn)現(xiàn)象及消除方法; 3.驗(yàn)證半加器、全加器的邏輯功

2009-07-15 18:35:50 64

64 時(shí)序邏輯電路的分析方法

1. 時(shí)序邏輯電路的特點(diǎn) 在時(shí)序邏輯電路中,任意時(shí)刻的輸出信號(hào)不僅取決于當(dāng)時(shí)的輸入信

2009-04-07 23:18:11 7731

7731

組合邏輯電路中的競(jìng)爭(zhēng)冒險(xiǎn)

前面分析組合邏輯電路時(shí),都沒(méi)有考慮門(mén)電路的延遲時(shí)間對(duì)電路產(chǎn)生的影響。實(shí)際上,從信號(hào)輸入到穩(wěn)定輸出需要一定的時(shí)間。由于從輸入

2009-04-07 10:13:03 10799

10799

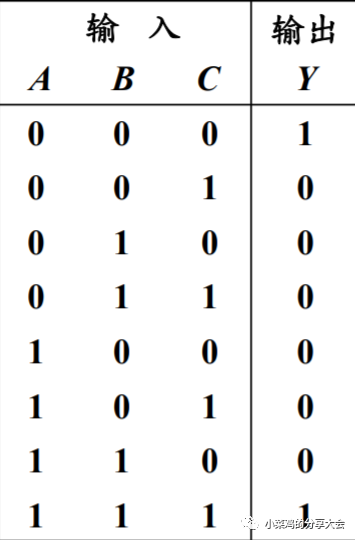

組合邏輯電路的設(shè)計(jì)

組合邏輯電路的設(shè)計(jì)與分析過(guò)程相反,其步驟大致如下: (1)根據(jù)對(duì)電路邏輯功能的要求,列出真值表; (2)由真值表寫(xiě)出邏輯表達(dá)

2009-04-07 10:12:22 12354

12354

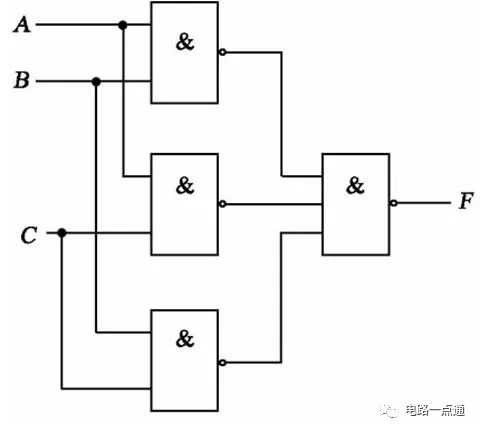

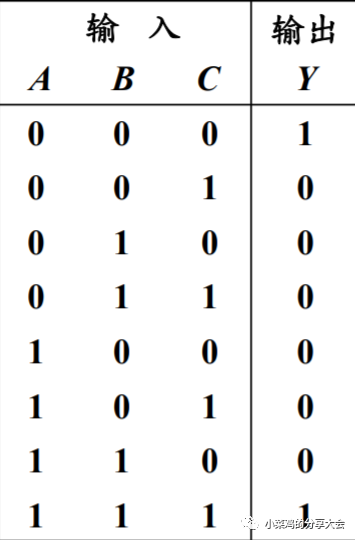

組合邏輯電路的分析

分析組合邏輯電路的目的是為了確定已知電路的邏輯功能,其步驟大致如下: 1.由邏輯圖寫(xiě)出各輸出端的邏輯表達(dá)式; 2.化簡(jiǎn)和變換各

2009-04-07 10:11:55 7022

7022

組合邏輯電路的分析與設(shè)計(jì)-邏輯代數(shù)

在任何時(shí)刻,輸出狀態(tài)只決定于同一時(shí)刻各輸入狀態(tài)的組合,而與先前狀態(tài)無(wú)關(guān)的邏輯電路稱(chēng)為組合邏輯電路。

2009-04-07 10:07:57 2503

2503

第十五講 組合邏輯電路的分析方法和設(shè)計(jì)方法

6.1概述組合邏輯電路:定義構(gòu)成電路特點(diǎn)6.2.1組合邏輯電路的分析方法

2009-03-30 16:21:07 4234

4234

門(mén)電路和組合邏輯電路20.1 脈沖信號(hào)20.2 基本門(mén)電路及其組合20.3 TTL門(mén)電路20.4 CMOS門(mén)電路20.5 邏輯代數(shù)20.6 組

2008-12-04 16:18:04 73

73 基本組合邏輯電路

一、 實(shí)驗(yàn)目的?⒈ 掌握一般組合邏輯電路的分析和設(shè)計(jì)方法。?⒉ 熟悉集成優(yōu)先編碼器的邏輯功能及簡(jiǎn)單應(yīng)用。

2008-09-24 22:14:03 2423

2423 組合邏輯電路設(shè)計(jì)一、實(shí)驗(yàn)目的1. 熟悉組合邏輯電路的基本設(shè)計(jì)方法;2. 練習(xí)用門(mén)電路、譯碼器、數(shù)據(jù)選擇器設(shè)計(jì)組合邏輯電路。二、實(shí)驗(yàn)設(shè)備1.

2008-09-12 16:41:23 55

55 基本邏輯電路: 組合邏輯電路、&

2008-09-12 16:35:29 40

40

數(shù)字邏輯電路的內(nèi)容:數(shù)制與編碼,,邏輯代數(shù)和邏輯函數(shù),集成邏輯門(mén),組合邏輯電路,中規(guī)模集成組

2008-09-06 01:54:26 22

22

組合邏輯電路 :

2007-12-20 23:02:07 28

28

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論