來源:旺材芯片

隨著5G、人工智能、元宇宙等新興科技產(chǎn)業(yè)快速崛起,發(fā)展低功耗、小尺寸、異質(zhì)整合及超高運算速度的芯片架構(gòu)技術(shù),已成為全球半導(dǎo)體制造業(yè)者最重要的產(chǎn)業(yè)趨勢與決勝關(guān)鍵。而跨過5 納米世代后,未來芯片制程又將迎來哪些白熱化的競爭與發(fā)展趨勢?

在芯片的先進制程競賽上,自英特爾(INTEL)于2012 年在22 納米芯片引入創(chuàng)新立體架構(gòu)的「鰭式晶體管」(FinFET)之后,全球半導(dǎo)體業(yè)者都在此基礎(chǔ)上進行研發(fā)。目前最先進的5 納米制程,即是采用FinFET 架構(gòu)來制作。該技術(shù)已由臺積電(TSMC)拔得頭籌,于2020 年成功投入量產(chǎn)。

然而,當(dāng)未來制程要再微縮至 3 納米時,F(xiàn)inFET卻會產(chǎn)生電流控制漏電的物理極限問題。事實上,三星(Samsung )已于近期趕在臺積電之前,發(fā)布了最新一代采用環(huán)繞式閘極場效晶體管(Gate-All-Around FET ;GAAFET )的全新架構(gòu)3納米制程。究竟在新一輪芯片制程的巔峰決戰(zhàn)中,誰能最終勝出仍待觀察。

由于GAAFET 的芯片架構(gòu)相比于FinFET,能以更小的體積實現(xiàn)更好的功耗表現(xiàn),實際可縮減45% 芯片面積、同時降低50% 的能耗。臺積電欲持續(xù)以FinFET 與三星GAAFET 在3 納米先進制程領(lǐng)域決戰(zhàn),2022 年絕對是決定勝負(fù)至為關(guān)鍵的一年。

而對于眾所矚目的下一代2 納米制程,臺積電也已公開表示亦將采用GAAFET 架構(gòu),并藉由導(dǎo)入低維度高電子遷移率材料以及特殊絕緣層材料等,來強化其在先進制程的競爭優(yōu)勢。GAAFET架構(gòu)儼然已成為下一世代延續(xù)莫爾定律(Moore‘s Law )發(fā)展的最佳選項。

01、淺談鰭式芯片架構(gòu)原理與發(fā)展

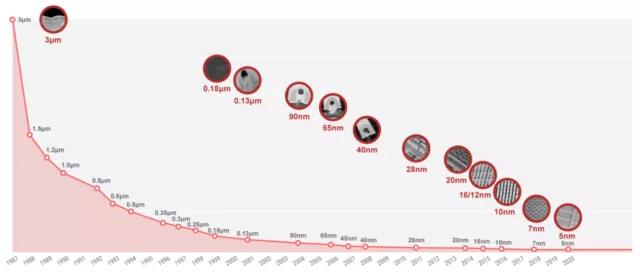

隨著摩爾定律(Moore’s Law)的發(fā)展,從微米(μm)技術(shù)節(jié)點演進至現(xiàn)今的5 納米技術(shù)節(jié)點(圖一),以及預(yù)計將于2022 年量產(chǎn)的3 納米技術(shù)節(jié)點[1],技術(shù)節(jié)點的數(shù)值越小,晶體管密度越高。

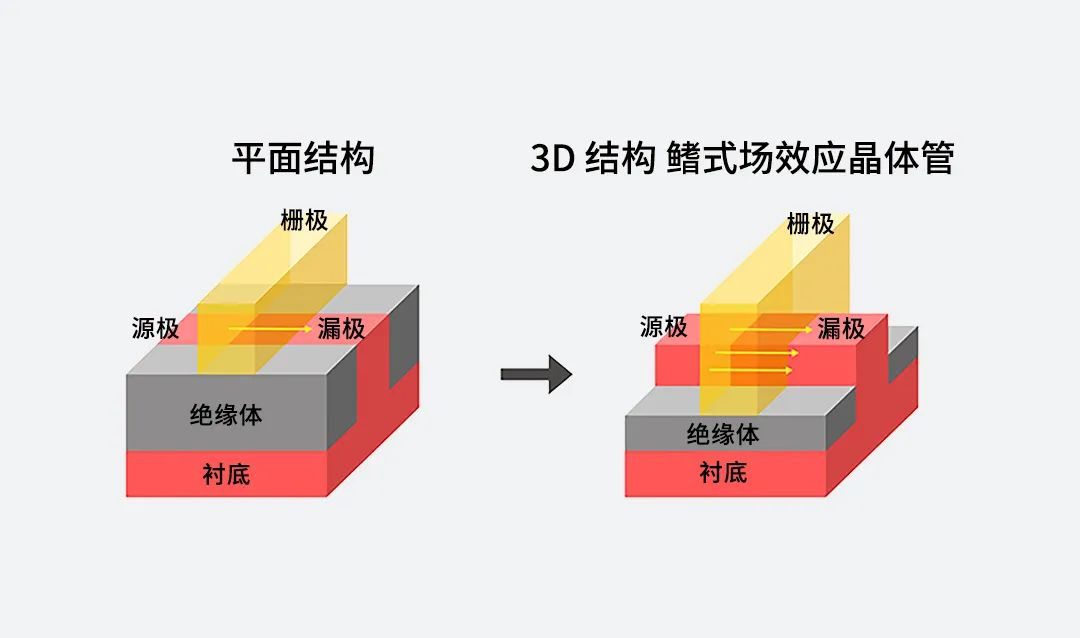

過去在平面晶體管(Planar FET)技術(shù)發(fā)展中,有兩項重要的技術(shù)突破:一是90 納米技術(shù)節(jié)點開始量產(chǎn)的應(yīng)變硅(strained Si),可提升硅通道的遷移率,增加電流;二是高介電常數(shù)/金屬閘極(high-k/metal gate),介電層的k 值越大,氧化層電容(Cox)越大,晶體管電流就越大,且可在相同的等效氧化層厚度(equivalent oxide thickness, EOT)下,以較大的物理厚度來降低漏電流。

▲圖一、臺積電的制程技術(shù)節(jié)點[1]。

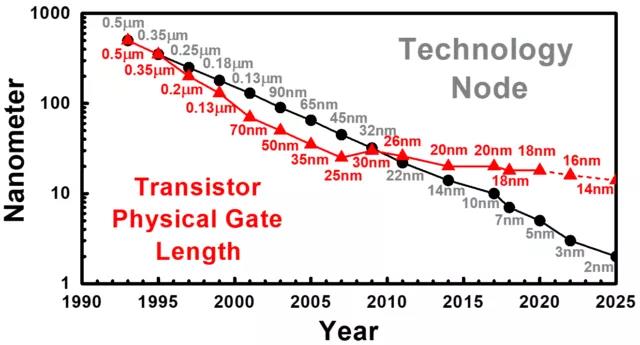

隨著傳統(tǒng)的半導(dǎo)體尺寸微縮,晶體管的閘極長度(gate length)也逐漸減小。實際上,閘極長度和技術(shù)節(jié)點的數(shù)值是不相等的,且在22納米技術(shù)節(jié)點以后,閘極長度會大于技術(shù)節(jié)點的數(shù)值(圖二)。隨著晶體管的尺寸越來越小,傳統(tǒng)的微縮方式逐漸接近其物理極限,單純依循摩爾定律的尺寸微縮,已無法提供如預(yù)期般效能的成長。自22 納米技術(shù)節(jié)點(Intel)及16 納米技術(shù)節(jié)點(臺積電)開始,由胡正明院士團隊提出的鰭式晶體管(FinFET)開始被業(yè)界所采用,三維晶體管也成為現(xiàn)今先進半導(dǎo)體的主流結(jié)構(gòu)。

▲ 圖二、約略估計晶體管技術(shù)節(jié)點(Technology Node )與閘極長度(Gate Length )。圖片來源:臺大電子工程學(xué)研究所劉致為教授研究團隊

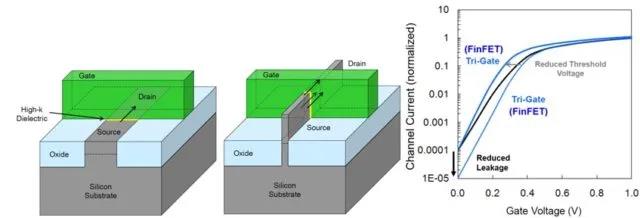

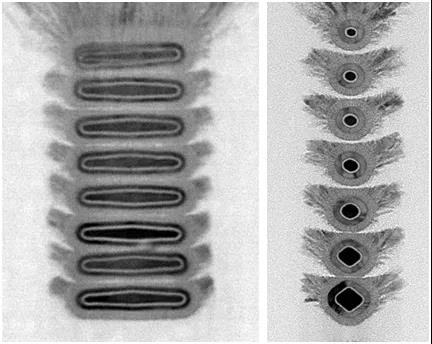

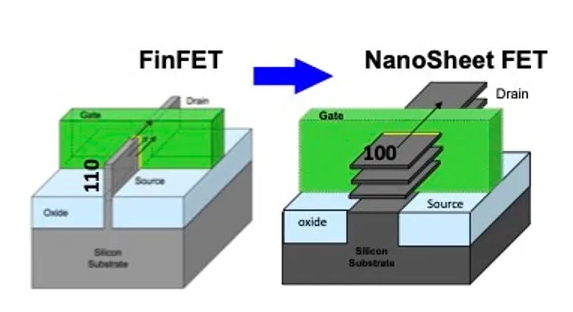

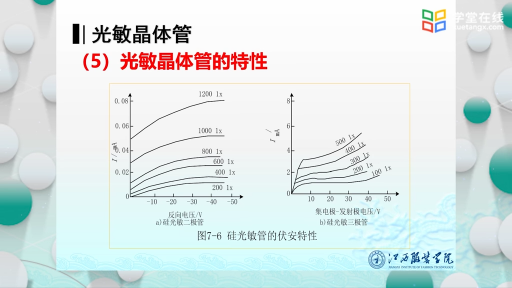

晶體管由傳統(tǒng)的平面式(圖三a)走向三維的立體結(jié)構(gòu)(圖三b),因為三面的閘極結(jié)構(gòu)(Tri-Gate)與魚鰭十分相似,所以稱為鰭式晶體管。鰭式晶體管具有比平面晶體管更大的等效寬度(effective width),可提高元件之電流密度,且其三維之結(jié)構(gòu)可增加通道控制能力,抑制短通道效應(yīng)(short channel effect)。

三維的鰭式晶體管結(jié)構(gòu)可降低次臨界擺幅(subthreshold swing, SS)與工作電壓,減少晶體管損耗功率(圖三c)。鰭式晶體管已從16 納米、10 納米、7 納米、5 納米、3 納米共發(fā)展了五代技術(shù)節(jié)點,為目前的主流元件結(jié)構(gòu)。

▲ 圖三、(a)平面晶體管示意圖(b)鰭式晶體管示意圖(c)電流–電壓關(guān)系圖。[2]

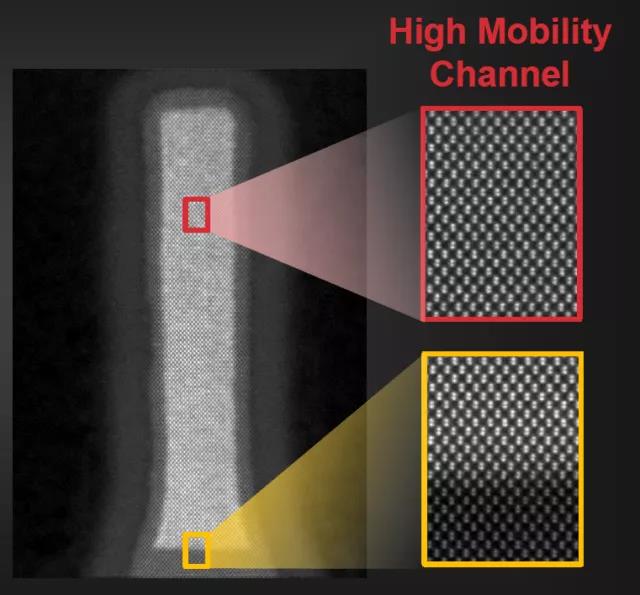

02、鰭式3 納米臺積電今年量產(chǎn)未來將采用閘極環(huán)繞式架構(gòu)

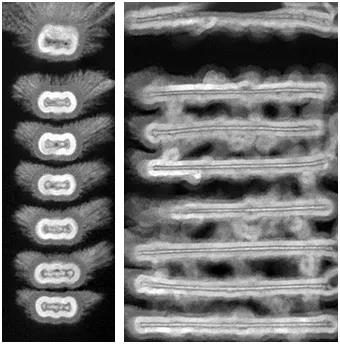

臺積電于2019 年國際電子元件會議(International Electron Devices Meeting, IEDM)宣布于5 納米技術(shù)節(jié)點量產(chǎn)擁有高遷移率通道(high mobility channel)之鰭式晶體管[3]。使用高遷移率通道,猶如駕駛跑車,速度更快,使晶體管的效能更佳。圖四[4] 為臺積電于2021 年國際固態(tài)電路研討會(International Solid-State Circuits Conference, ISSCC)中所展示的高遷移率通道鰭式晶體管,由圖中可看出高遷移率通道與底部的硅材料具有明顯的對比,且皆有清楚的啞鈴狀結(jié)構(gòu)(dumbbell)。

臺積電預(yù)計于2022 下半年開始量產(chǎn)3 納米技術(shù)節(jié)點的全世代制程晶體管,與5 納米技術(shù)節(jié)點相比,3 納米技術(shù)節(jié)點的邏輯密度將增加約70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30% [1]。

▲ 圖四、臺積電 5 納米技術(shù)節(jié)點的高遷移率通道鰭式晶體管 [4] 。? IEEE

為了進一步增加通道的控制能力與維持短通道效應(yīng)的抑制,必須改變晶體管之架構(gòu)。三星、臺積電、Intel 已宣布在3納米技術(shù)節(jié)點(Samsung )和2納米技術(shù)節(jié)點(TSMC 、Intel 20A )將采用閘極環(huán)繞式(Gate-All-Around, GAA )的納米片(nanosheet )結(jié)構(gòu)。

03、閘極環(huán)繞式晶體管架構(gòu)原理

閘極環(huán)繞式晶體管具有比鰭式晶體管更好的閘極控制能力,在先進技術(shù)節(jié)點將取代鰭式晶體管結(jié)構(gòu),晶體管密度也將持續(xù)提升。使用GAA 晶體管結(jié)構(gòu),猶如使用強力水龍頭,滴水不漏,使晶體管有效降低漏電流,更加節(jié)能省電。

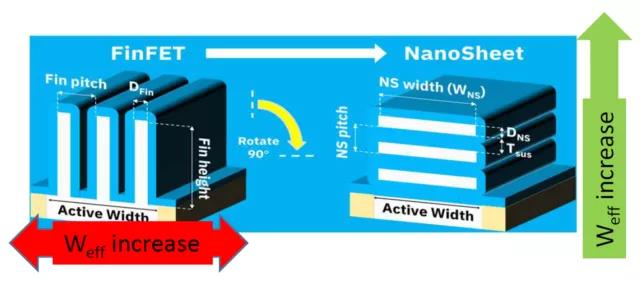

為了增加晶體管的驅(qū)動電流,采用通道堆疊(channel stacking)的方法,在垂直方向增加通道數(shù)目,猶如建構(gòu)雙層高架橋,在相同占地面積下,可負(fù)載更多車流量,使晶體管擁有更高電流并增加晶體管密度,有效提升元件效能。圖五[5] 為垂直堆疊納米片(stacked nanosheets)的結(jié)構(gòu),可視作將FinFET 旋轉(zhuǎn)90 度并進行垂直堆疊,形成四面環(huán)繞式的閘極結(jié)構(gòu)。

有別于FinFET 的通道寬度(D Fin)是由微影制程(Lithography)所限制,stacked nanosheets 的通道厚度(D NS)可藉由磊晶(epitaxy)來決定,因此可精準(zhǔn)控制厚度。除此之外,stacked nanosheets 可往垂直方向增加通道層數(shù),在相同的占地面積(footprint)下具有更大的等效寬度(effective width, W eff),提供更大的電流以提升晶體管效能。

磊晶(epitaxy)技術(shù)除了可精準(zhǔn)決定stacked nanosheets 的通道厚度外,也可以控制通道與通道之間的距離(suspension thickness, T sus),不會像FinFET 增加占地面積,且可以透過降低T sus的方式來減少元件的寄生電容(parasitic capacitance)。

▲ 圖五、鰭式晶體管(FinFET)與垂直堆疊納米片(Stacked nanosheets)之比較 [5] 。? IEEE

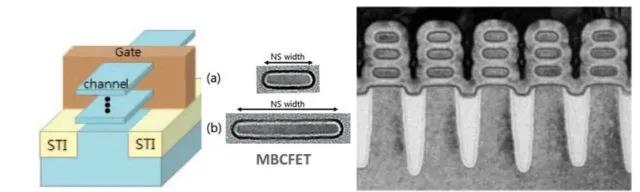

三星率先在2018 IEDM國際會議上宣布以Multi-Bridge-Channel FET (MBCFET )之GAA 晶體管作為3納米技術(shù)節(jié)點之晶體管結(jié)構(gòu)(圖六 a,b )[6] ,其中提到MBCFET采用90%的FinFET制程,與現(xiàn)今業(yè)界之FinFET制程具有良好的相容性。

MBCFET 顧名思義,結(jié)構(gòu)與多層橋梁相似,實際上和前述的stacked nanosheets 是相同的結(jié)構(gòu)。與FinFET 相比,MBCFET 具有更好的閘極控制,在相同的面積下,也有更大的等效寬度以提供更大的驅(qū)動電流,并可依照不同的應(yīng)用來調(diào)整通道寬度,提高電路設(shè)計之彈性。

另一方面,IBM 的2 納米技術(shù)節(jié)點提出三層垂直堆疊的stacked nanosheets (圖六c)[5],其通道寬度為40 納米、通道高度為5 納米、閘極長度為12 納米,并采用底部介電層絕緣(bottom dielectric isolation, BDI),能有效減少漏電流,降低芯片功耗。與7 納米制程技術(shù)相比,預(yù)計提升45% 的性能或降低75% 的耗能[7]。

▲ 圖六、(a, b)三星3納米技術(shù)節(jié)點之MBCFET [6] ? IEEE (c)IBM 2納米技術(shù)節(jié)點之三層垂直堆疊通道晶體管[5] 。? IEEE

04、高層數(shù)通道堆疊的GAA 晶體管將成未來主流結(jié)構(gòu)

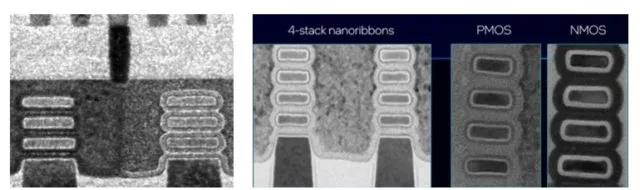

臺積電在2021 ISSCC 國際會議上展示三層垂直堆疊的stacked nanosheets 作為2 納米技術(shù)節(jié)點之晶體管結(jié)構(gòu)(圖七a),可提供更佳的性能及更低的次臨界擺幅[4]。Intel 則宣布2024 年將以RibbonFET(垂直堆疊四層的nanoribbons,也與stacked nanosheets 結(jié)構(gòu)相似)作為20A 技術(shù)節(jié)點之結(jié)構(gòu)(圖七b)[8],并將于2025 年以優(yōu)化的RibbonFET 作為18A 技術(shù)節(jié)點之結(jié)構(gòu)。

由業(yè)界趨勢可見,高層數(shù)通道堆疊的GAA晶體管為未來晶體管之主流結(jié)構(gòu)。在2020 年超大型積體電路技術(shù)研討會(Symposium on VLSI Technology, VLSI)中,法國半導(dǎo)體研究機構(gòu)CEA-Leti 發(fā)表了七層的Si GAA nanosheets 晶體管(圖八)[9]。

▲ 圖七、(a)臺積電2納米技術(shù)節(jié)點之三層垂直堆疊通道晶體管 [4] ? IEEE(b)Intel 20A技術(shù)節(jié)點之四層垂直堆疊通道晶體管(RibbonFET )[8] 。

▲圖八、法國半導(dǎo)體研究機構(gòu) CEA-Leti發(fā)表之七層垂直堆疊硅通道晶體管[9] 。? IEEE

05、由硅到鍺硅等晶體管通道材料發(fā)展

目前已發(fā)表的GAA晶體管,通道材料大部分以硅(Si )為主,為了增加電路的運作速度,必須提升晶體管的驅(qū)動電流(垂直堆疊通道電流的總和),除了往垂直方向增加通道數(shù)目外,采用高載子遷移率(mobility )的材料作為晶體管通道可進一步提高晶體管的驅(qū)動電流,例如鍺(Ge )、鍺硅(GeSi )、鍺錫(GeSn )等新四族材料,具有優(yōu)于硅的電子及電洞遷移率,并且與現(xiàn)今業(yè)界的硅半導(dǎo)體制程技術(shù)有良好的相容性。

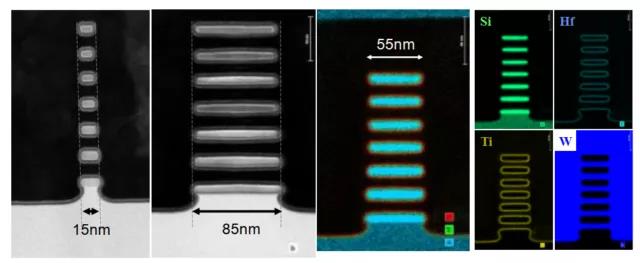

臺大電子工程學(xué)研究所劉致為教授研究團隊,于2021 VLSI國際會議上發(fā)表了八層鍺硅N型GAA晶體管(8 stacked Ge 0.75 Si 0.25 nanosheets )(圖九左)[10],擁有極高的通道均勻性。為進一步提高元件的驅(qū)動電流,將鍺硅通道的鍺濃度提升至95%,以提高通道之電子遷移率,并成功展示了世界首顆高效能七層鍺硅N 型GAA 晶體管(7 stacked Ge 0.95 Si 0.05 nanowires)(圖九右)[10],此研究成果也獲國際頂尖期刊Nature Electronics 報導(dǎo)于Research Highlight [11]。

由此可見,高層數(shù)堆疊之高遷移率通道GAA 晶體管為未來半導(dǎo)體技術(shù)節(jié)點的一大趨勢。其中磊晶(epitaxy )與蝕刻(etching )為高層數(shù)堆疊通道GAA晶體管最重要的兩大制程技術(shù),藉由兩者的互相優(yōu)化才能成功制備高效能晶體管。目前臺大是業(yè)界以外,唯一能研發(fā)多層堆疊通道GAA晶體管的大學(xué),也成為學(xué)界與業(yè)界接軌的重要橋梁。

▲圖九、本研究團隊發(fā)表之(左)八層 GeSi nanosheets [10](右)七層 GeSi nanowires [10] 。? IEEE

P 型晶體管方面,因為壓縮應(yīng)變的鍺錫(GeSn)材料擁有比純鍺和硅更高的電洞遷移率,可增加元件之驅(qū)動電流,成為通道材料的潛力之一。然而因鍺錫材料之能隙較小,元件具有較大之截止?fàn)顟B(tài)漏電流(I OFF)以及較小之開關(guān)電流比(I ON /I OFF),將造成元件功率耗損過大。此問題可藉由降低通道厚度來改善,隨著通道厚度變薄,受量子局限效應(yīng)(quantum confinement effect)影響使I ON /I OFF隨之上升,因閘極控制能力增強使次臨界擺幅(SS)下降。

然而當(dāng)通道厚度小于5nm 時因表面粗糙散射(surface roughness scattering)的影響,導(dǎo)致載子遷移率降低,故需搭配高堆疊、高載子遷移率之鍺錫通道,維持元件之驅(qū)動電流。因此研究團隊在2021 IEDM 國際會議上發(fā)表七層與八層堆疊鍺錫極薄通道P 型晶體管(7 stacked and 8 stacked Ge 0.9 Sn 0.1 ultrathin bodies)(圖十) [12],以鍺錫材料作為高遷移率通道(high mobility channel),優(yōu)化磊晶(epitaxy)與高蝕刻選擇比等向性干蝕刻(highly selective isotropic dry etching, HiSIDE)制程,制備出厚度為3 納米之極薄通道,有效降低元件之漏電流,且I ON /I OFF為鍺/鍺錫三維晶體管之世界紀(jì)錄,此篇論文也獲得2021 IEDM 最佳學(xué)生論文獎(Best Student Paper Award)。

▲圖十、本研究團隊發(fā)表之(左)七層與(右)八層鍺錫極薄通道[12] 。? IEEE

06、臺積電、三星及英特爾下一步?jīng)Q戰(zhàn)GAAFET

綜上所述,高層數(shù)(highly stacked )、高遷移率(high mobility ),以及極薄通道(ultrathin bodies )之GAA晶體管將能使半導(dǎo)體芯片效能更高、更省電,進而使先進半導(dǎo)體科技不斷進步,為人類帶來更好的生活。

接下來,先進制程架構(gòu)將從FinFET 轉(zhuǎn)進GAAFET,臺積電、三星及英特爾在未來5 納米以下的GAAFET 技術(shù)發(fā)展上勢必也將展開一場白熱化的競賽。然而,值得注意的是,欲在未來半導(dǎo)體霸權(quán)時代取得技術(shù)領(lǐng)先地位,除了晶圓制造技術(shù)上須掌握優(yōu)勢外,系統(tǒng)封裝整合技術(shù)也是半導(dǎo)體產(chǎn)業(yè)重要的發(fā)展方向。

而在GAAFET 世代之后,是否會有更為創(chuàng)新、可延續(xù)莫爾定律發(fā)展的新型晶體管結(jié)構(gòu)出現(xiàn)?就讓我們拭目以待。

審核編輯:符乾江

電子發(fā)燒友App

電子發(fā)燒友App

評論